背景

《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- 1、OSERDESE2 总述

- 1.1、数据并串转换器(Data Parallel-to-Serial Converter)

- 1.2、三态并串转换器(3-State Parallel-to-Serial Conversion)

- 2 ··· OSERDESE2 原语

- 3 ··· OSERDESE2 端口

- 4 ··· OSERDESE2 属性

- 5、OSERDESE2 时钟配置方法

- 6、OSERDESE2 位宽扩展

- 7、输出反馈(Output Feedback)

- 8、OSERDESE2 延迟

- 9、Timing Characteristics

- 10、OSERDESE2 原语例化

- 11、参考文献

前言

输入串并转换器 (Input serial-to-parallel converters,ISERDESE2) ,

输出并串转换器(output parallel-to-serial converters ,OSERDESE2),

支持极高的 I/O 数据速率,使内部逻辑的运行速度可以到 I/O 速率的1/8。

1、OSERDESE2 总述

-

OSERDESE2是7系列FPGA中专用的并串转换器,集成特定的时钟与逻辑资源,专为高速源同步接口设计。

-

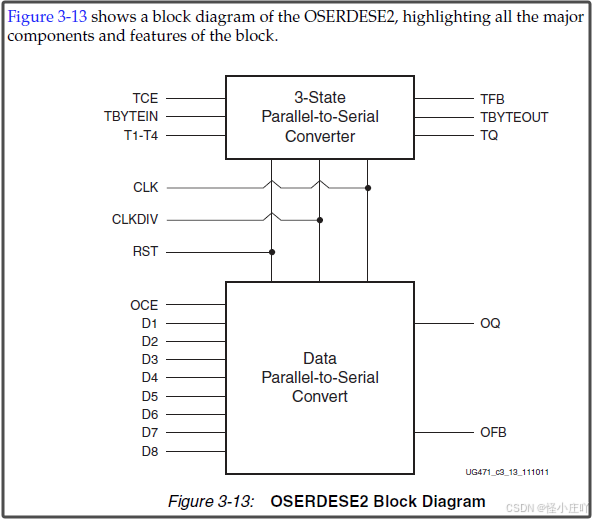

每个 OSERDESE2 模块都包含:

一个专用的数据串行器(a dedicated serializer for data)

和 一个三态控制串行器(3-state control),

可以被配置成SDR和DDR模式。

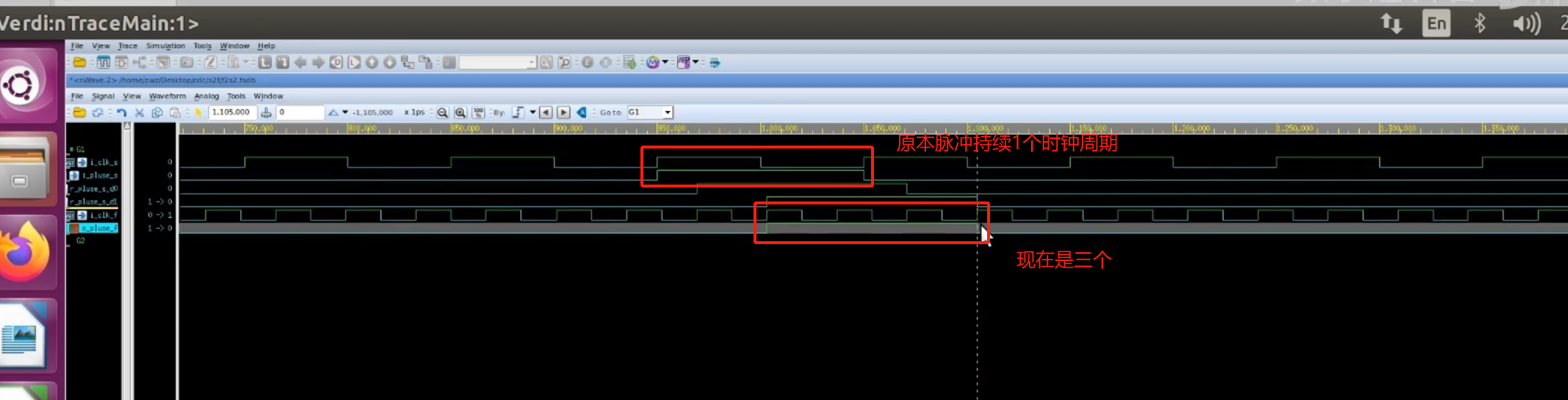

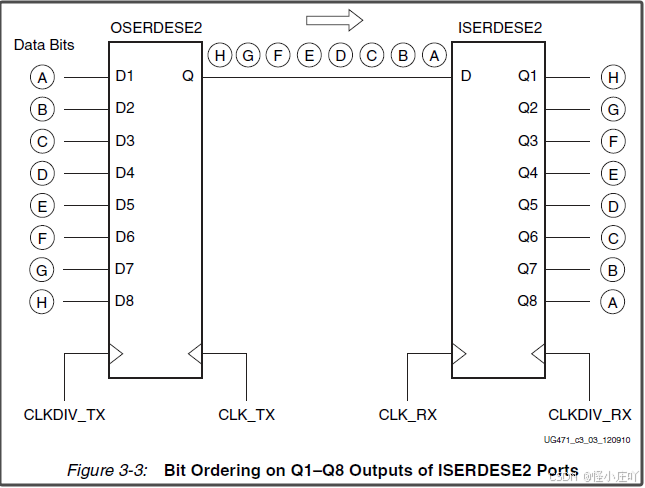

如图 3-3 所示,OSERDESE2 的输入比特顺序与 ISERDESE2 的输出顺序互为镜像。例如:

OSERDESE2的输入:字 FEDCBA 的最低有效位(LSB) A 输入至 D1 端口。

ISERDESE2 的输出:同一比特 A 从 Q8 端口输出。

如果,CLK频率为200 MHz:

SDR模式(8-bit):并串转换速率为 200 MHz × 8 = 1.6 Gbps。

DDR模式(8-bit):并串转换速率为 200 MHz × 8 × 2 = 3.2 Gbps

-

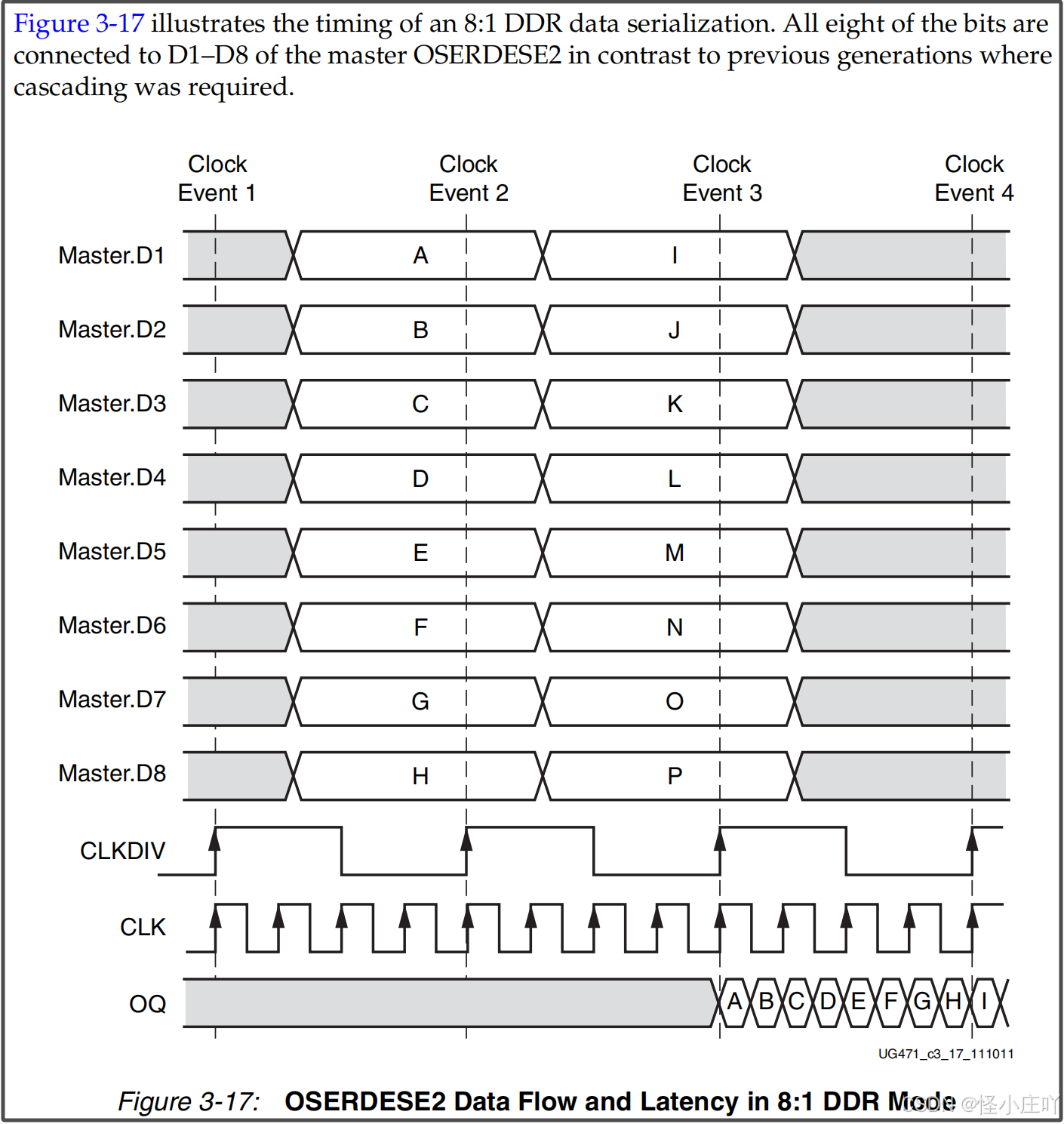

数据串行器:串行化比最高8:1(若使用OSERDESE2位宽扩展,则可达10:1和14:1)。

-

三态控制串行器:支持最高14:1串行化比。

-

OSERDESE2 模块有一个DDR3专用模式,针对高速存储器应用。

1.1、数据并串转换器(Data Parallel-to-Serial Converter)

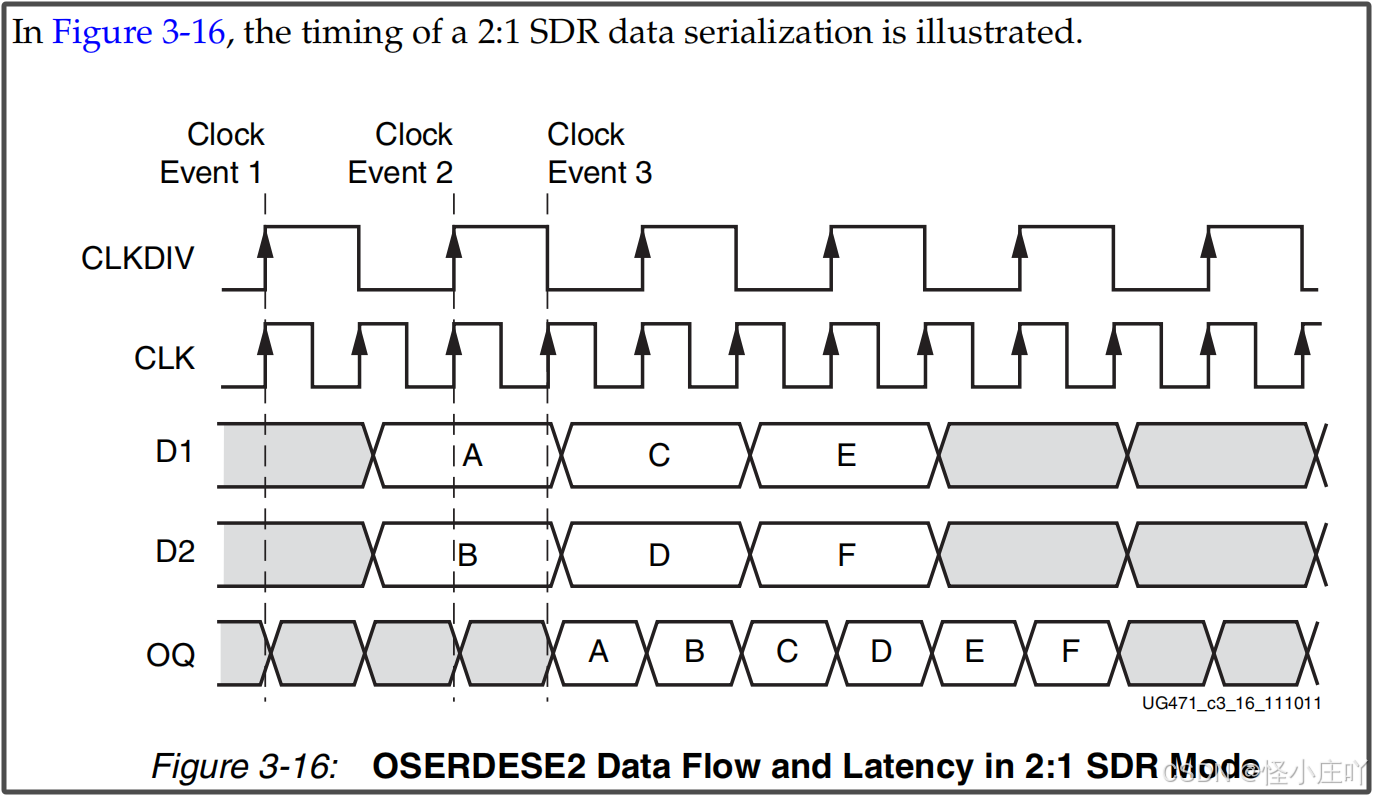

OSERDESE2模块内的数据并串转换器接收来自FPGA逻辑的2至8位并行数据(若启用OSERDESE2位宽扩展,可支持14位),将数据串行化后通过OQ引脚输出至IOB。并行数据从最低位输入引脚(D1)开始串行传输(即D1引脚数据最先从OQ引脚输出)。该转换器支持两种工作模式:single-data rate (SDR) and double-data rate (DDR)。

OSERDESE2 使用 CLK 和 CLKDIV 这两个时钟信号来进行数据速率转换。CLK 是高速串行时钟,CLKDIV 是分频后的并行时钟。CLK 和 CLKDIV 必须相位对齐。

使用前,必须对OSERDESE2施加复位信号。 OSERDESE2 包含一个控制数据流的内部计数器。 如果未将复位信号的释放与 CLKDIV 同步,可能会产生意外输出。

此外OSERDESE2内部还有一个计数器,用来计数当前dout输出的是输入信号的第几位数据了,所以在使用OSERDESE2前,必须对OSERDESE2进行复位,复位信号可以是同步复位,也可以是异步复位,但是复位信号无效边沿必须与CLKDIV同步(即使用异步复位时,要考虑同步释放复位)。(《xilinx原语详解及仿真之OSERDESE2》)

1.2、三态并串转换器(3-State Parallel-to-Serial Conversion)

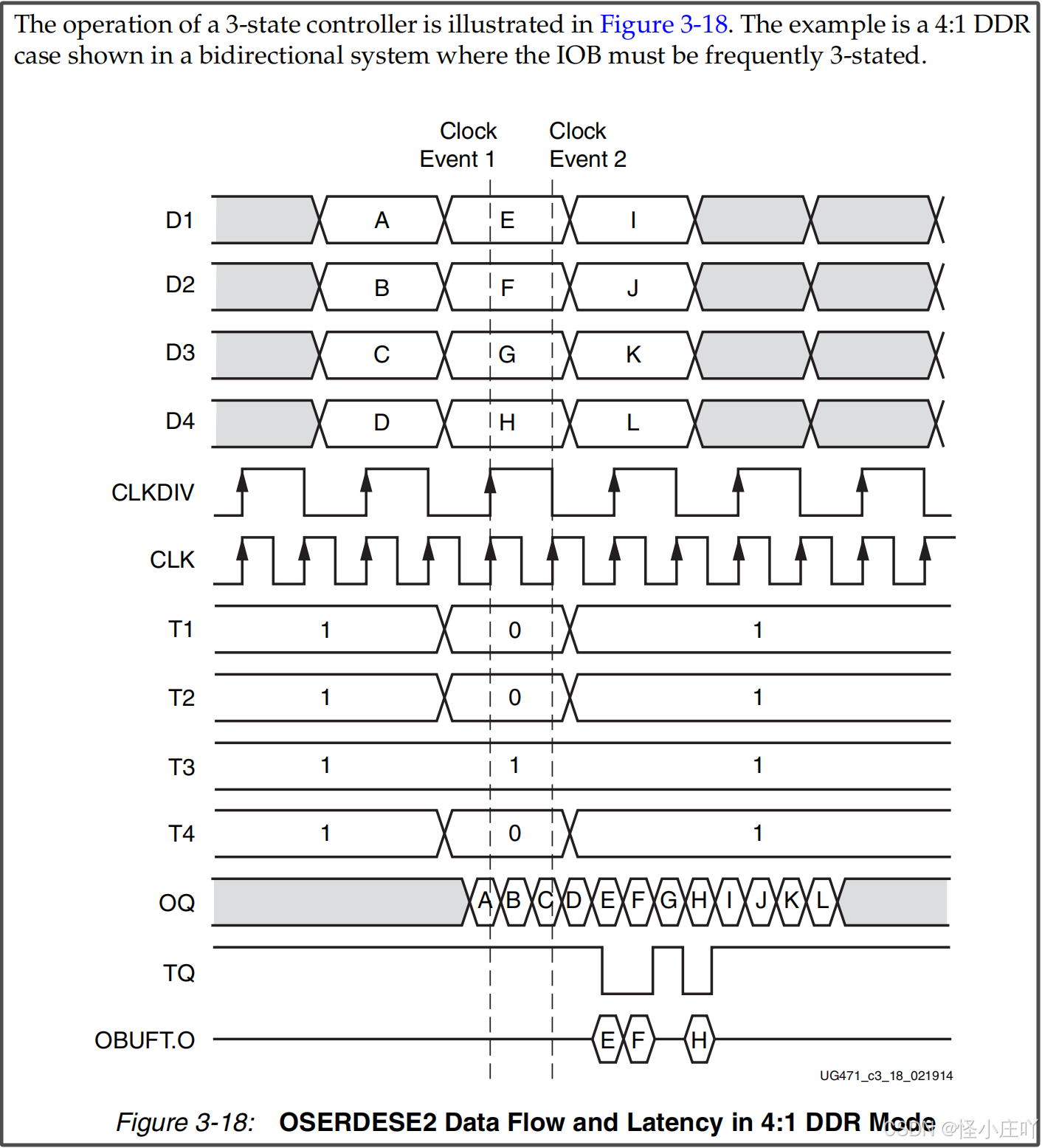

OSERDESE2模块除了具有数据并串转换功能外,还包括三态控制并串转换器,用于IOB的三态信号控制。最大支持4位并行三态信号串行化,不可级联。

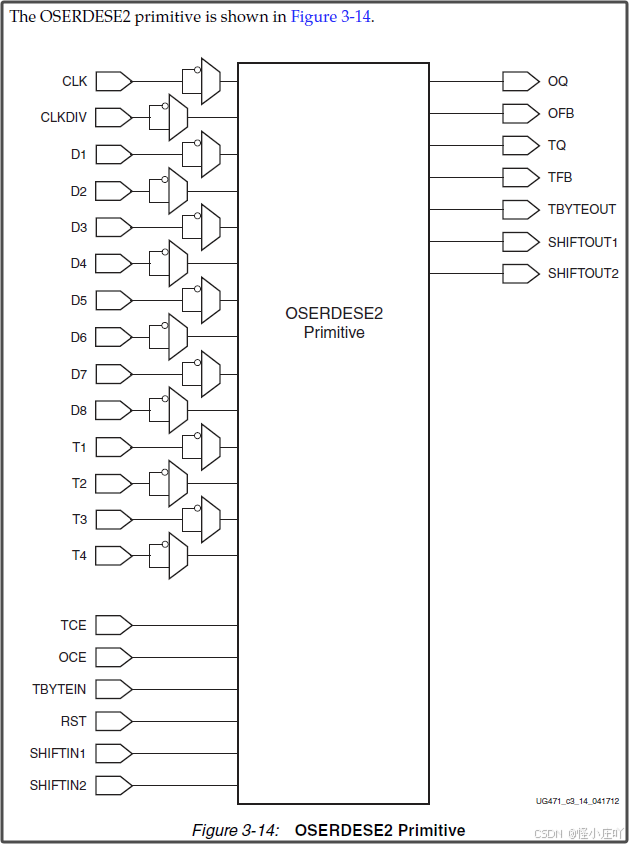

2 ··· OSERDESE2 原语

3 ··· OSERDESE2 端口

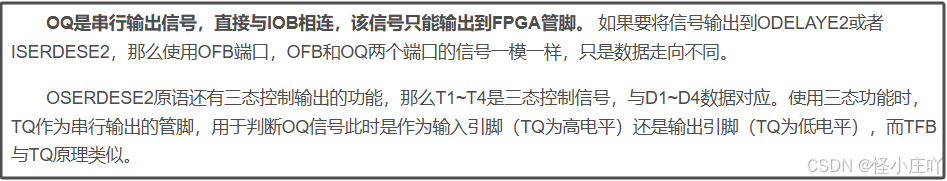

- 1、Data Path Output - OQ

OQ 是 OSERDESE2 模块的数据输出端口。输入端口 D1 的数据将首先出现在 OQ。此端口将数据并串转换器的输出连接至 IOB 的数据输入端口。OQ 不能直接驱动 ODELAYE2,必须通过 OFB 引脚实现延迟控制。

- 2、Output Feedback from OSERDESE2 - OFB

OFB 是 OSERDESE2 的串行(高速)数据反馈端口,用途包括:连接至 ODELAYE2 原语实现输出延迟,或者将串行数据回传至 ISERDESE2。

- 3、3-state Control Output - TQ

TQ 是 OSERDESE2 的三态控制输出端口,用于将三态并串转换器的输出连接至 IOB 的三态控制输入。

- 4、3-state Control Output - TFB

TFB 是 OSERDESE2 的三态状态反馈端口,可向 FPGA 逻辑端反馈当前三态状态(当 IOB 处于高阻态时有效)。

- 5、High-Speed Clock Input - CLK

CLK 是驱动并串转换器串行端的高速时钟信号。

- 6、Divided Clock Input - CLKDIV

CLKDIV 是驱动并串转换器并行端的分频时钟信号,为 CLK 的分频信号且与CLK相位对齐。

- 7、Parallel Data Inputs - D1 to D8

所有并行数据通过 D1-D8 端口输入 OSERDESE2,支持配置为 2 至 8 位(即 8:1 串行化)。通过从模式 OSERDESE2 级联可扩展至 10 或 14 位。

- 8、Reset Input - RST

复位生效(高电平):使 CLK/CLKDIV 域所有数据触发器异步输出低电平。

复位释放(同步要求):需与 CLKDIV 同步释放,内部逻辑在 CLK 第一次上升沿重新同步。

在多比特输出结构中的每个 OSERDESE2 应由相同的复位信号驱动,该信号异步断言,并与 CLKDIV 同步去断言,以确保所有 OSERDESE2 元素同步退出复位。

复位释放时,需确保 CLK/CLKDIV 已稳定。

- 9、Output Data Clock Enable - OCE

OCE 为数据路径的高电平有效时钟使能信号。

- 10、3-state Signal Clock Enable - TCE

TCE 为三态控制路径的高电平有效时钟使能信号。

- 11、Parallel 3-state Inputs - T1 to T4

所有并行三态信号通过 T1 至 T4 端口进入 OSERDESE2 模块。这些端口连接到 FPGA 内部结构。它们可配置为一位、两位或四位,或者直通。DATA_RATE_TQ 和 TRISTATE_WIDTH 属性控制这些端口的行为。

- 在博客《xilinx原语详解及仿真之OSERDESE2》中,看到如下一段话。

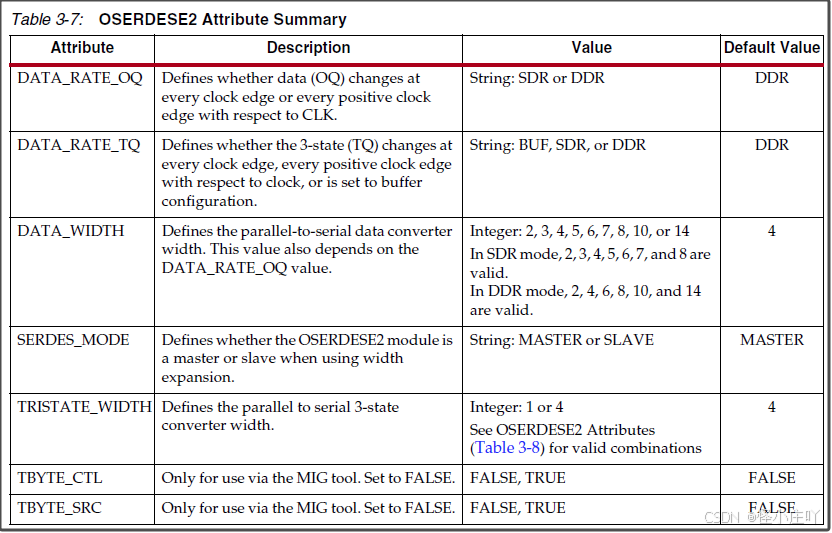

4 ··· OSERDESE2 属性

- 1、DATA_RATE_OQ

此属性定义数据以单数据速率(SDR)或双数据速率(DDR)处理。允许值为 SDR 或 DDR,默认值为 DDR。

- 2、DATA_RATE_TQ

此属性定义三态控制以单数据速率(SDR)、双数据速率(DDR)或直通模式(BUF)处理。允许值为 SDR、DDR 或 BUF,默认值为 DDR。

SDR/DDR 模式下:使用全部四个三态输入(T1-T4),其行为由 TRISTATE_WIDTH 属性配置。

BUF 模式下:

旁路 SDR/DDR 模式寄存器,因此应使用 T1 输入。T1 输入信号与所有其他信号异步,因为它仅通过 OSERDESE2 传递。

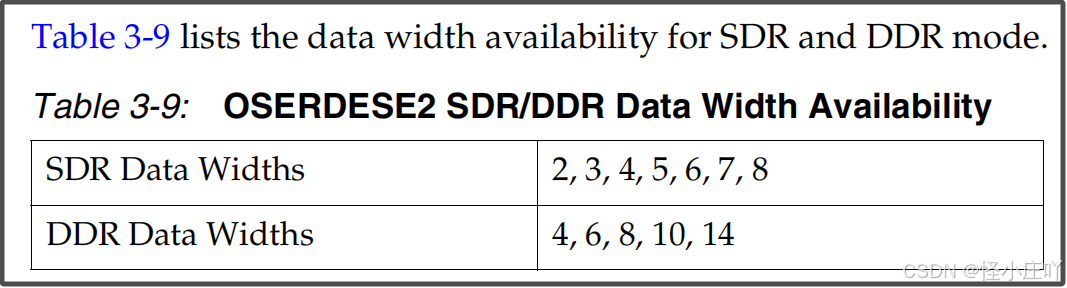

- 3、DATA_WIDTH

DATA_WIDTH 属性定义并行转串行转换器的并行数据输入位宽。

当 DATA_RATE_OQ 设置为 SDR 时,DATA_WIDTH 属性的可能取值为 2、3、4、5、6、7 和 8。当 DATA_RATE_OQ 设置为 DDR 时,DATA_WIDTH 属性的可能取值为 4、6、8、10 和 14。

当 DATA_WIDTH 设置为大于 8 的位宽时,必须将一对 OSERDESE2 配置为主从模式。

- 4、SERDES_MODE

此属性定义位宽扩展时 OSERDESE2 的主从模式,允许值为 MASTER(主)或 SLAVE(从),默认值为 MASTER。

- 5、TRISTATE_WIDTH

此属性定义三态并串转换器的并行输入位宽,其取值范围取决于 DATA_RATE_TQ:

DATA_RATE_TQ=SDR 或 BUF,TRISTATE_WIDTH=1;

DATA_RATE_TQ=DDR,TRISTATE_WIDTH=1或4;

5、OSERDESE2 时钟配置方法

理想情况下,CLK与CLKDIV需保持相位对齐(允许一定容差)。

OSERDESE2模块的有效时钟配置方案仅包含以下两种:

1、由 BUFIO 驱动 CLK , 由 BUFR 驱动 CLKDIV 。

2、CLK和CLKDIV由同一MMCM或PLL的CLKOUT[0:6]驱动。

若使用MMCM驱动OSERDESE2的CLK和CLKDIV,则供给OSERDESE2的缓冲类型不能混用。例如,若CLK由BUFG驱动,则CLKDIV也必须由BUFG驱动。

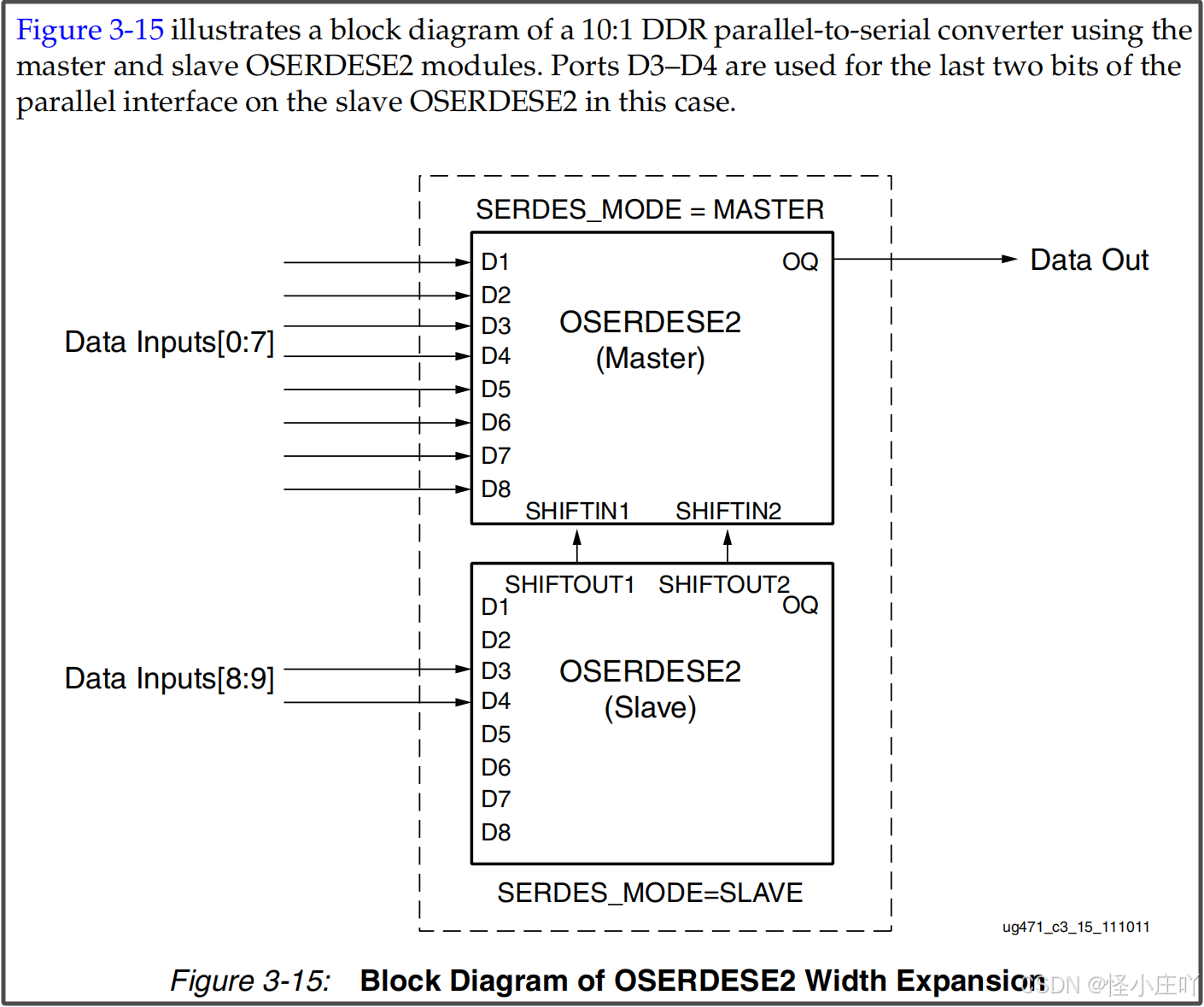

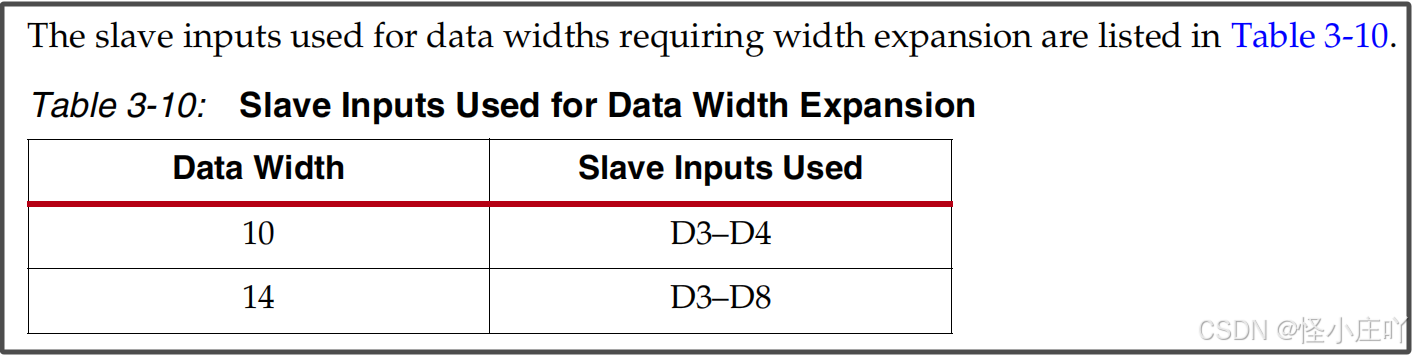

6、OSERDESE2 位宽扩展

每个I/O单元(I/O tile)有两个OSERDESE2模块:一个主模块和一个从模块。

将主OSERDESE2的SHIFTIN端口连接到从OSERDESE2的SHIFTOUT端口,可以把并串转换器扩展到10:1和14:1(仅限DDR模式)。

对于差分输出,主OSERDESE2必须位于差分输出对的正端(_P引脚)。

非差分输出时,与从OSERDESE2相关的输出缓冲区不可用,位宽扩展也无法使用。

使用互补单端标准(例如DIFF_HSTL和DIFF_SSTL)时,可能无法使用位宽扩展。这是因为互补单端标准会使用 I/O单元 内中的两个OLOGICE2/3模块(OLOGICE2/3 blocks)来传输两个互补信号,从而没有可用的OLOGICE2/3模块用于位宽扩展。

- 位宽扩展指南:

-

- 1、两个 OSERDESE2 模块必须是相邻的主从对。

-

- 2、将主 OSERDESE2 的 SERDES_MODE 属性设置为 MASTER,

从 OSERDESE2 的 SERDES_MODE 属性设置为 SLAVE。

- 2、将主 OSERDESE2 的 SERDES_MODE 属性设置为 MASTER,

-

- 3、用户必须将从模块的 SHIFTIN 引脚连接到主模块的 SHIFTOUT 引脚。

-

- 4、从模块使用 Q3 到 Q8 引脚作为输出。

-

- 5、主模块和从模块的DATA_WIDTH相等。

-

- 6、属性INTERFACE_TYPE设置为DEFAULT。

7、输出反馈(Output Feedback)

OSERDESE2引脚OFB具有以下两种功能:

• 作为反馈路径至ISERDESE2的OFB引脚。。

• 与ODELAYE2连接。OSERDESE2的输出可以通过OFB引脚路由至ODELAYE2模块,然后通过ODELAYE2进行延迟。

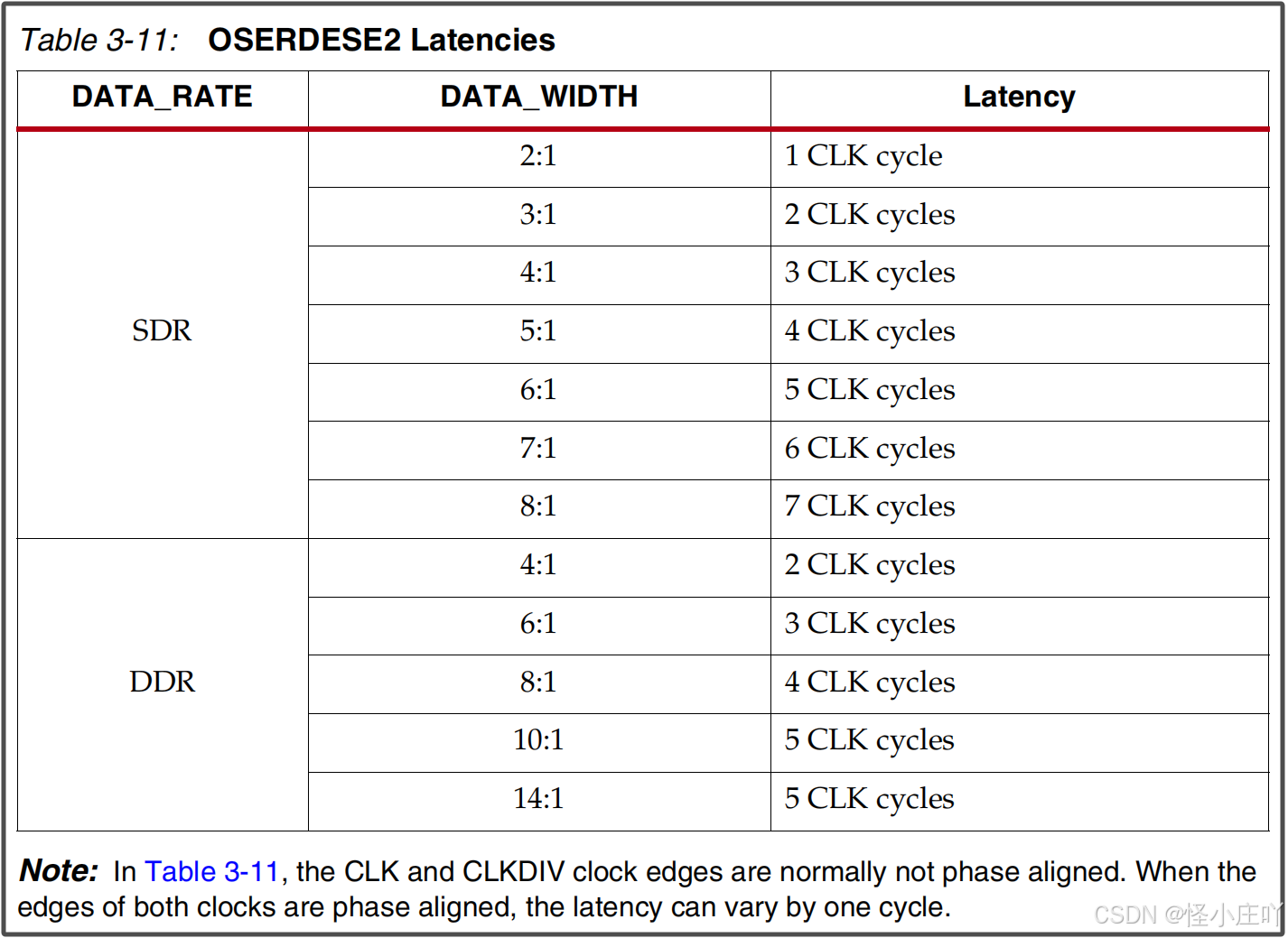

8、OSERDESE2 延迟

- DEFAULT Interface Type Latencies(默认接口类型延迟)

OSERDESE2模块的输入到输出延迟取决于DATA_RATE和DATA_WIDTH属性。

延迟被定义为以下两个事件之间的时间间隔:

事件(a):CLKDIV的上升沿将数据从输入端D1-D8时钟输入到OSERDESE2。

事件(b):串行流的第一位出现在OQ。

表3-11总结了各种OSERDESE2延迟值。

当CLK和CLKDIV的相位对齐时,延迟可能相差一个CLK周期,如果CLK和CLKDIV的相位没有对齐时,延迟的值取决于DATA_RATE和DATA_WIDTH的值。

9、Timing Characteristics

- 2:1 SDR Serialization

- 8:1 DDR Serialization

- 4:1 DDR 3-State Controller Serialization

- 4:1 DDR 3-State Controller Serialization

时钟事件1:

T1、T2和T4被置0以解除三态条件。

T1-T4和D1-D4在OSERDESE2中的串行化路径相同(包括延迟),因此在时钟事件1期间,EFGH位始终与T1-T4引脚上呈现的0010对齐。

时钟事件2:

在EFGH被采入OSERDESE2后的一个时钟周期,数据位E出现在OQ。

此延迟与表3-11中列出的4:1 DDR模式OSERDESE2延迟一个时钟周期一致。

在时钟事件1期间,T1上的三态位0在0010被采入OSERDESE2三态块后的一个时钟周期出现在TQ。此延迟与表3-11中列出的 4:1 DDR模式OSERDESE2延迟一个时钟周期一致。

10、OSERDESE2 原语例化

// OSERDESE2: Output SERial/DESerializer with bitslip

// 7 Series

// Xilinx HDL Libraries Guide, version 13.4

OSERDESE2 #(

.DATA_RATE_OQ("DDR"), // DDR, SDR

.DATA_RATE_TQ("DDR"), // DDR, BUF, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

.SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH(4) // 3-state converter width (1,4)

)OSERDESE2_inst (

.OFB(OFB), // 1-bit output: Feedback path for data

.OQ(OQ), // 1-bit output: Data path output

// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each)

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.TBYTEOUT(TBYTEOUT), // 1-bit output: Byte group tristate

.TFB(TFB), // 1-bit output: 3-state control

.TQ(TQ), // 1-bit output: 3-state control

.CLK(CLK), // 1-bit input: High speed clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each)

.D1(D1),

.D2(D2),

.D3(D3),

.D4(D4),

.D5(D5),

.D6(D6),

.D7(D7),

.D8(D8),

.OCE(OCE), // 1-bit input: Output data clock enable

.RST(RST), // 1-bit input: Reset

// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each)

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2),

// T1 - T4: 1-bit (each) input: Parallel 3-state inputs

.T1(T1),

.T2(T2),

.T3(T3),

.T4(T4),

.TBYTEIN(TBYTEIN), // 1-bit input: Byte group tristate

.TCE(TCE) // 1-bit input: 3-state clock enable

);

// End of OSERDESE2_inst instantiation

11、参考文献

1、《ug471_7Series_SelectIO.pdf》

2、《xilinx原语详解及仿真之OSERDESE2》