Orcad是一个很优秀的原理图工具,orcad支持tcl/tk开发,介绍一下当前本人开发的脚本工具,可用于提高硬件工程师的画图效率。

- 环境准备

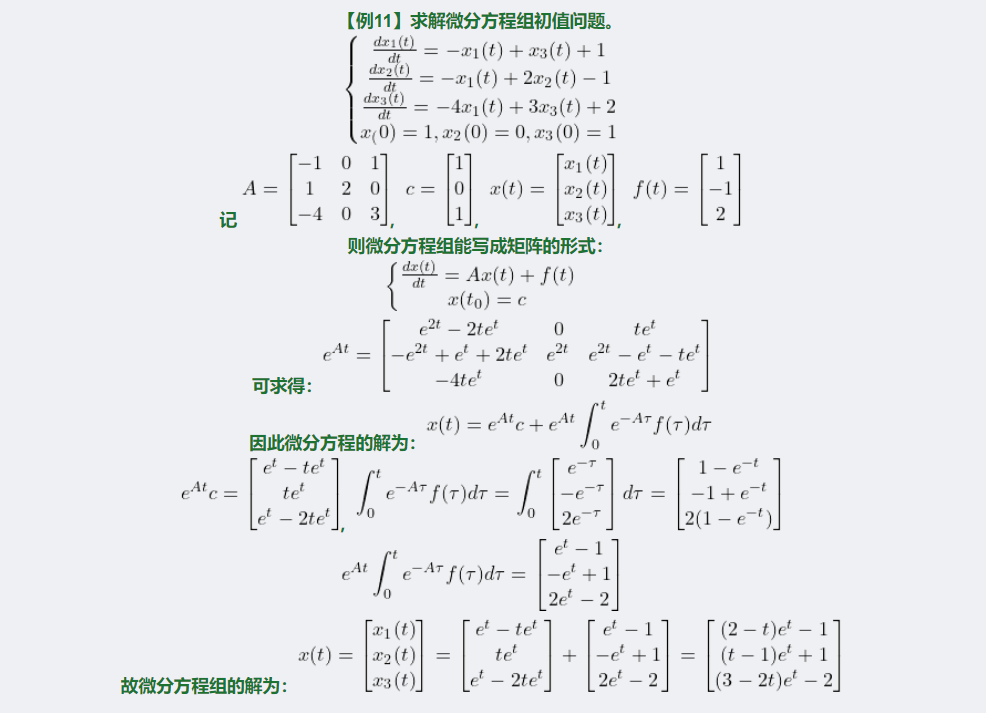

- 将压缩包解压到C盘(注意一定要C盘根目录下),C:\Tcltk。如下图所示

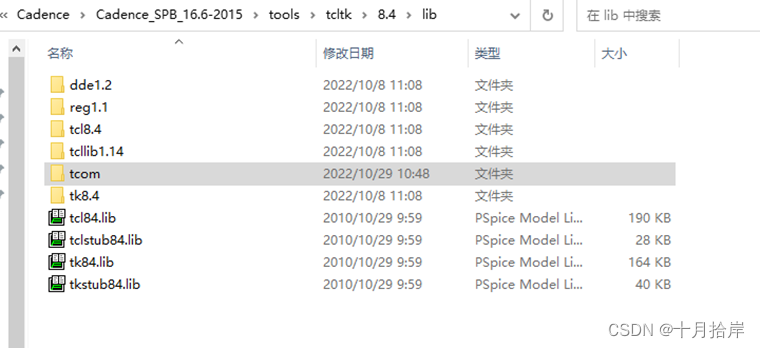

- 将上图中tcom这个文件夹剪切到cadence的安装目录下,例如,我的路径是D:\Cadence\Cadence_SPB_16.6-2015\tools\tcltk\8.4\lib

- 将压缩包中Tcltk.tcl这个文件放到cadence的安装目录下的capAutoLoad

例如我的路径是D:\Cadence\Cadence_SPB_16.6-2015\tools\capture\tclscripts\capAutoLoad

- 适用范围

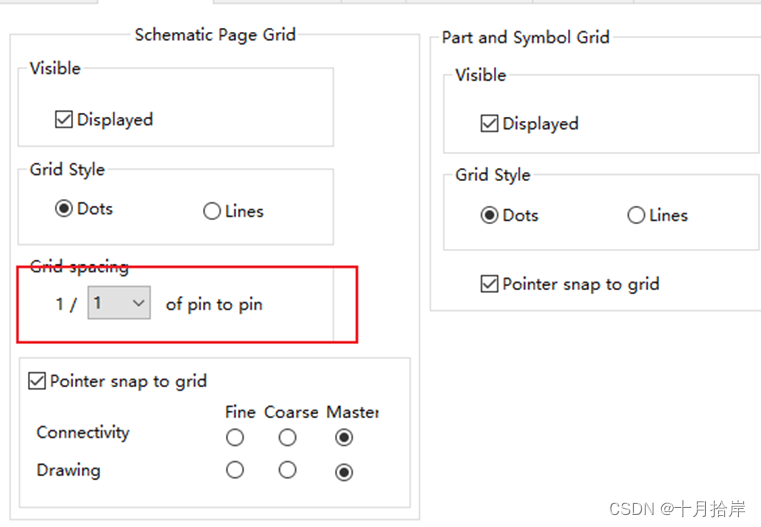

Tcltk脚本主要适用于cadence 16.6(orcad capture cis)版本,原理图图纸且pin to pin的栅格点必须使用1:1,其他关于图纸尺寸大小等配置,保持默认。除了换PIN工具外,其他命令可以适应mm和inch。

- 功能简介

- 准备工作

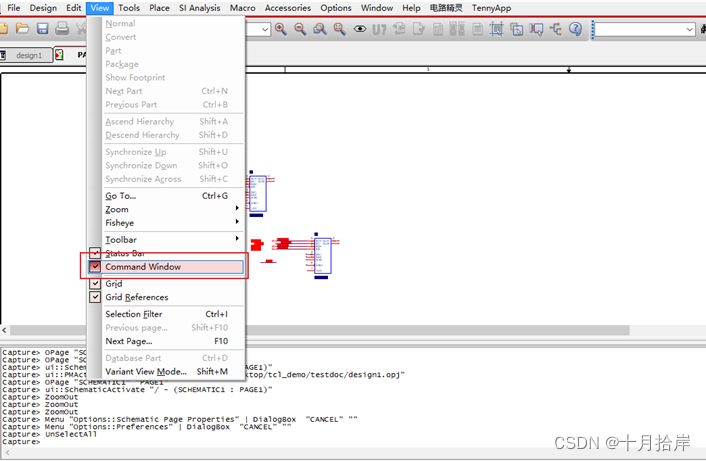

将capture的command窗口调出来

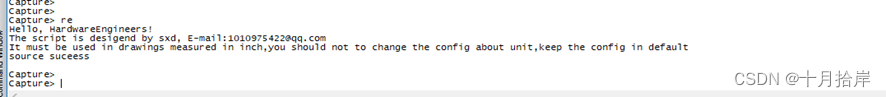

每次打开软件之后需要输入re(表示reload源文件)。

-

- 功能介绍

- Tcltk功能介绍列表

| command命令 | 功能名 | 功能描述 | 操作步骤 |

| help | 帮助 | 显示所有命名列表 | 输入help |

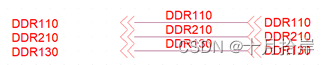

| col cor (create offpage right/left) | 增加页间符 | 给网络标号增加页间符

| 选中网络标号后,在command窗口中输入命令即可 |

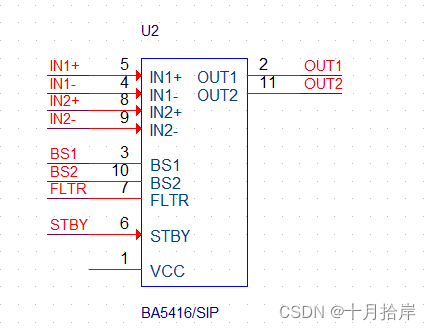

| cw create wire | 创建网络标号 | 根据PIN名称等创建网络标号

| 1.选中器件的pin管脚,输入cw 0,会自动生成pin名称的alias 2. 选中器件的pin管脚,输入cw XX,会自动生成XX_pin名称的alias,如AD9361_IN+ 3. 选中任意一个wire,输入cw XXX,会创建一个网络,CTRL+V可以粘贴 4. 选中任意一个wire,输入cw {XX1 XX2 XX3…},会创建一组网络,CTRL+V可以粘贴 |

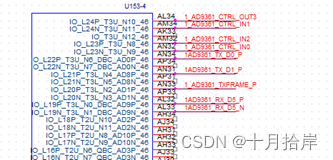

| Dxls3 C:/Users/Administrator/Desktop/1.xlsx 注意此处需要输入的文件路径,用“/”与windows下不同 | 换PIN | PCB换pin完成后,回导回原理图中,此功能比较强大,适应于FPGA换PIN

| 1. 确认PCB输出换pin结果表格数据格式 第一列是FPGA/CLPD的管脚信息,第五列是PCB工程师调整后的新网络名称。 2.选中需要换pin的bank,输入命令,会自动完成换PIN,注意图纸备份。 具体可参考附件A |

| SetOptionBool Journaling TRUE SetOptionBool DisplayCommands TRUE | 显示操作日志 | 打开操作日志 | SetOptionBool Journaling TRUE SetOptionBool DisplayCommands TRUE |

注:所有命令带参数都需要加空格

购买地址如下https://m.tb.cn/h.U6Vdvc9?tk=w5KXdX059kR

![[附源码]java毕业设计社区志愿者服务系统](https://img-blog.csdnimg.cn/b1503ad0153941b7be4ebd4fe1292bf3.png)

![第五届“传智杯”全国大学生计算机大赛(练习赛)[传智杯 #5 练习赛] 时钟](https://img-blog.csdnimg.cn/4a765f370e834973b2c87ccf6f8d60f1.png)