专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

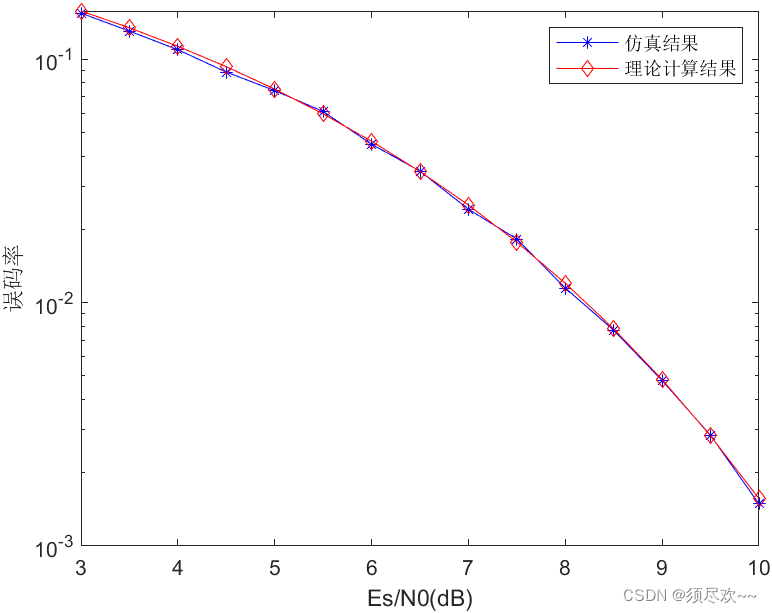

分析

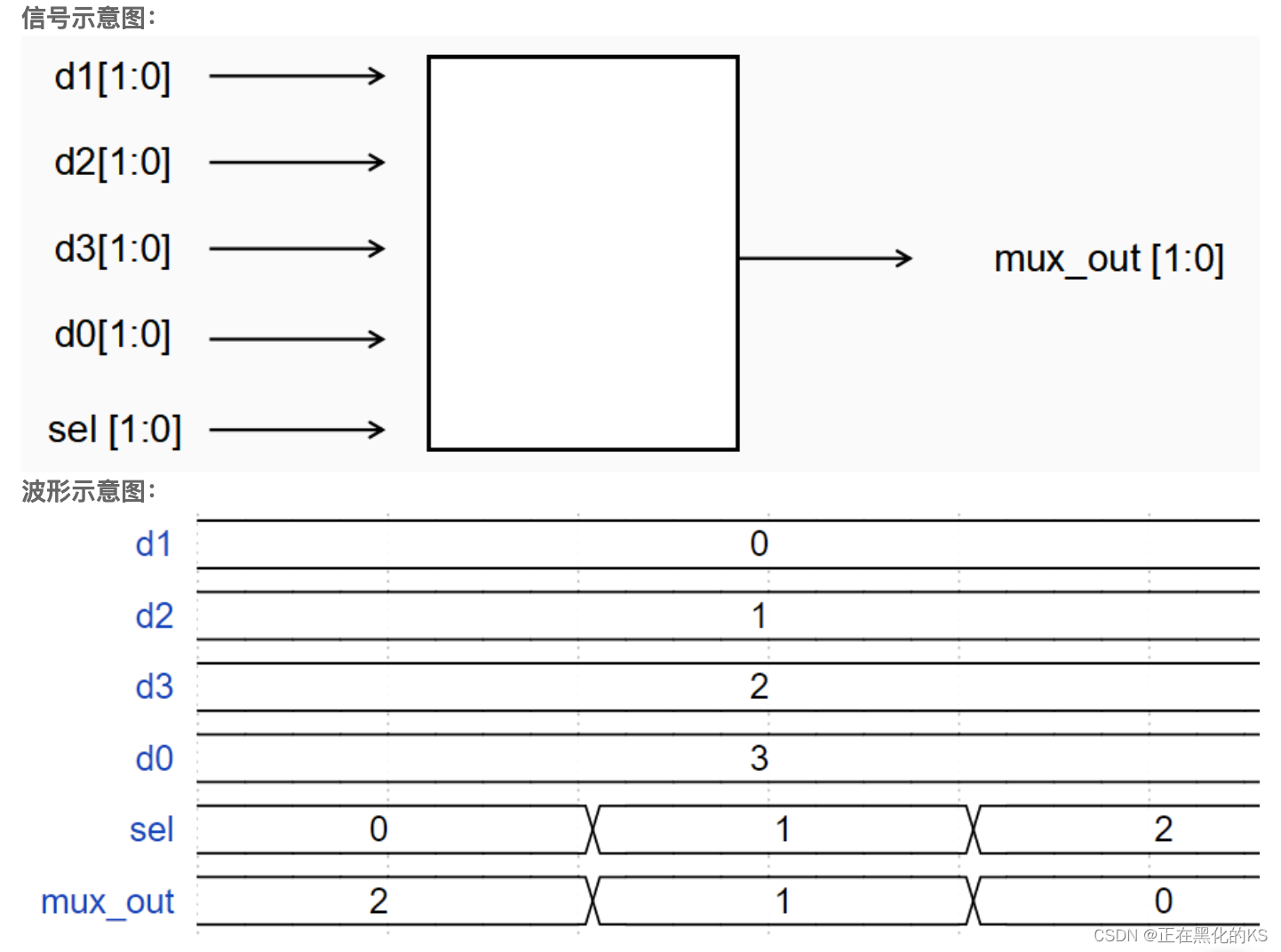

通过波形示意图我们可以发现,当sel为0,1,2时,输出mux_out分别为d3,d2,d1,那么sel=3时,输出一定为d0,因此我们只需要用case语句分别判断输入的四种情况即可。

`timescale 1ns/1ns

module mux4_1(

input [1:0]d1,d2,d3,d0,

input [1:0]sel,

output[1:0]mux_out

);

//*************code***********//

reg [1:0] mux_out_tmp ;

always@(*) begin

case(sel)

2'b00: mux_out_tmp = d3 ;

2'b01: mux_out_tmp = d2 ;

2'b10: mux_out_tmp = d1 ;

2'b11: mux_out_tmp = d0 ;

default: mux_out_tmp = d3 ;

endcase

end

assign mux_out = mux_out_tmp ;

//*************code***********//

endmodule