PLL 端口信号解释

| 信号名 | 含义 |

|---|---|

| PLL_PWD | power down |

| pll_rst | 复位PLL |

| clkin_dsel | 0:clkin1作为参考时钟;1:clkin2作为参考时钟 |

| clkfb | 外部反馈时钟输入 |

| dyn_idiv[5:0] | 动态 input divider(输入分频器) 分频系数 0:64分频;1:63分频;… |

| dyn_fdiv[5:0] | 动态feedback divider(反馈分频器) 0:64分频;1:63分频;… |

| dyn_odiv[5:0] | 动态clkout_0_divider (输出0分频器) 0:128分频;1:120分频;…8为步进 |

| dyn_odiv2/3/4[5:0] | 动态clkout_2/3/4_divider(输出2/3/4分频器) 0:128分频;1:126分频;…2为步进 |

| dyn_phase1/2/3/4[3:0] | clkout_1/2/3/4动态相位:0:0度;1:22.5度;…22.5度为步进 |

| reset_idiv | 复位input divider(输入分频器) |

| reset_odiv | 复位output divider(输出分频器) |

| clkout0/1/2/3/4_gate | gate(门控)对应输出时钟 |

| pll_lock | 锁定 |

| clkout0/1/2/3/4 | 时钟输出 |

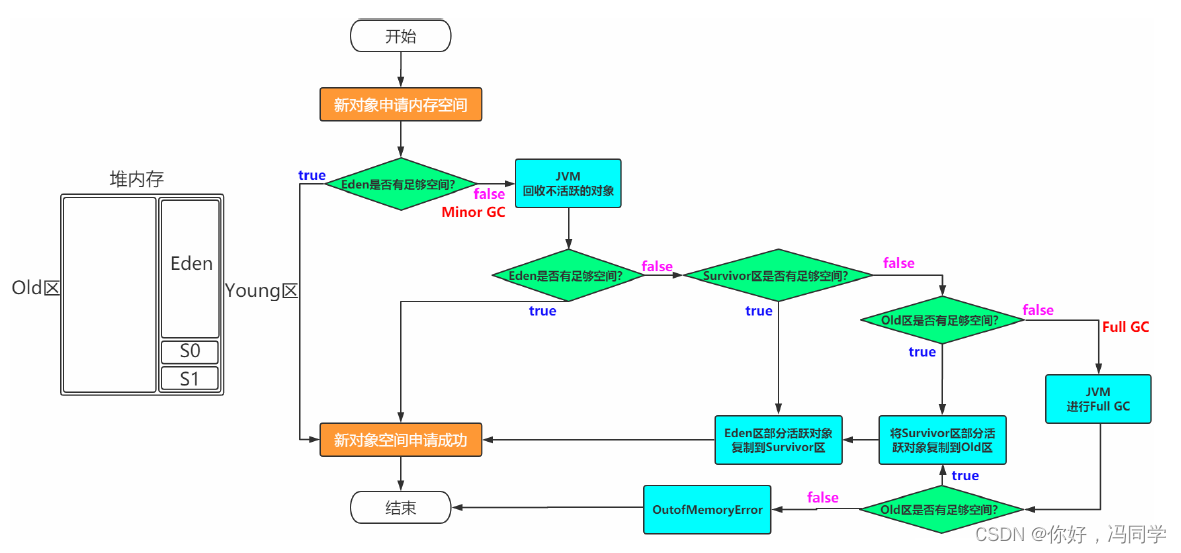

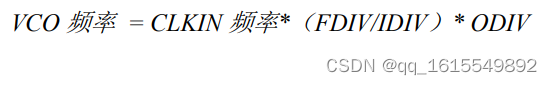

PLL 的输出频点计算

| 只看反馈时钟选择内部CLKOUT[1:0]情况。 |

|---|

| divider模式 :clkout[0] = clkin x fdiv/idiv |

| divider模式 :[1] = 只是clkout[0]的移相 |

| divider模式 :clkout[2]=clkin x fdiv /(idiv x odiv2) |

| divider模式 :clkout[3]= clkin x fdiv /(idiv x odiv3) frac_divider模式:clkout[3]= 0.5 x clkin x fdiv x odiv0 /(idiv x ( clkout3_div125_m+clkout3_div125_n*0.125 ) ); 注:(clkout3_div125_m,clkout3_div125_n) != (1,1) clkout3 m(1~63) + (07)N.125小数分频;(1.0 (63+7x0.125) ) |

| divider模式 :clkout[4]= clkin x fdiv /(idiv x odiv4) cnt_divider模式 :clkout[4]= clkin x fdiv / (idiv x odiv4) x(1/2^33) x clkout4_div32bit_k 保证 : 2^33 / clkout4_div32bit_k是整数 那么 clkout4_div32bit_k必须是2的整数幂;clkout0/clkout4 divider<=50 |

结论:pll能保证clkfb时钟和clkin时钟的相位保持一致。

180H时钟概述

3种时钟类型

GCLK:global clk,基于象限。整个芯片分4象限;每个象限各有14个GCLK网络。

RCLK:regional clk,8个region,每个region各有2个RCLK

IO_CLK:专用于高速接口应用的器件每一侧(左侧除外)各有四个 IO CLK 网络。

2种时钟硬核

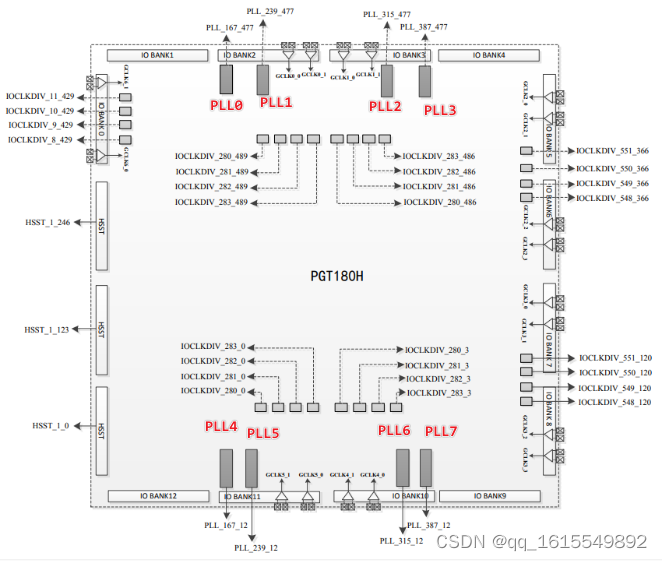

PLL:PGT180H 提供了 8 个 PLL,以 满足用户关于频率变化和相位调整的需求。

DLL:PGT180H 片内提供了 8 个DLL 为高速接口应用提供了延 迟锁相功能。

3种时钟IO类型

a)普通时钟输入管脚(共18个)

b)PLL 参考时钟输入管脚(仅限于 CLKOUT[0]和CLKOUT[1])

c)PLL 反馈输入时钟管脚

下文的时钟输入管脚(IO_CLK)指三者统称。

时钟输入管脚 既可以作为普通IO使用,又可以作为时钟输入使用。

当作为时钟输入使用的优点:避免普通布线资源带来的干扰。

时钟输入管脚可直接接入到内部所有时钟网络,包括 GLOBAL CLK,REGIONAL CLK 或 IO CLK; 从而减少干扰,提高时钟质量。时钟输入管脚可以是一对差分输入端口,也可以是一个单端输入端口; 选择单端输入时,仅仅 PAD T 可直接接入到内部时钟网络。

时钟输入管脚在哪?

BANK1/4/9/12 没有时钟输入管脚,其它 BANK 各有两个时钟输入管脚;整个芯片共有 18 个时钟输入管脚。

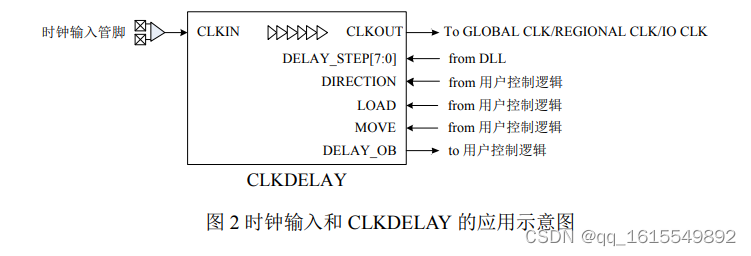

时钟输入管脚是否能调整输入时钟的延时(相位)?

CLKDELAY模块

每个时钟输入管脚都有有 CLKDELAY模块,可以调整范围255 x 25ps的延时。

GCLK

不但时钟可以进入GCLK,而且fanout 较高的信号(如 CE/RS 信号)也可以用GCLK 来实现。

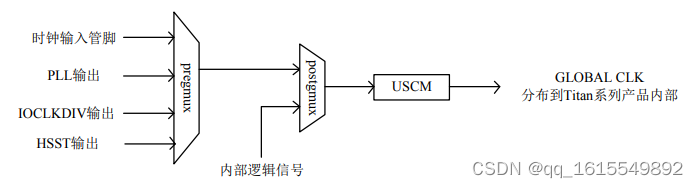

GCLK 的源有哪些?

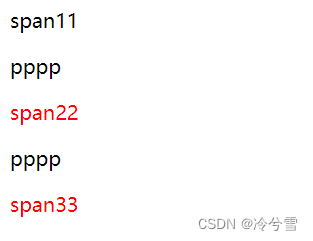

图中可以看到:时钟输入管脚、PLL 输出时钟、IOCLKDIV 输出时钟、HSST的输出时钟和内部逻辑信号都可以作为GCLK的源。

全局时钟输入源之间可能出现冲突。

USCM是什么?

USCM(User Select Clock Mux)为 GLOBAL CLK 提供了 clock gate 和 clock mux 的功能,它支持 CLKBUFG,CLKBUFGCE 以及 CLKBUFGMUX 三种模式。每个 GLOBAL CLK 网络均包含一个 USCM 模块,所以 Titan 系列产品共有 56 个 USCM 模块。

时钟资源在FPGA的位置布局

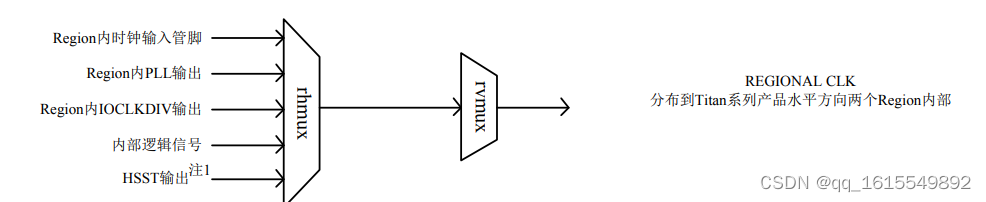

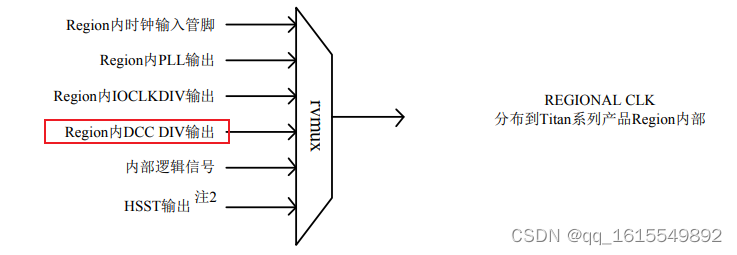

RCLK

REGIONAL CLK 基于 Region 分布,每个 Region 有各自独立的 2 个 REGIONAL CLK 网络。除了驱动本地 Region,也可以通过 rhmux(regional horizontal mux)将水平方向相邻的两个 REGIONAL CLK联在一起作为一个大 Region 使用。

与 GLOBAL CLK 相比,REGIONAL CLK 的优点是延迟小,skew 小,但它分布范围有限;

RCLK的源有哪些?

只在region内部会多一个 DCC DIV 源。

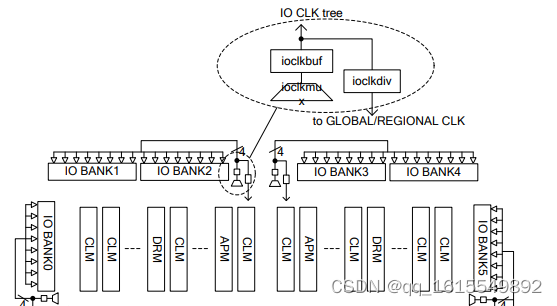

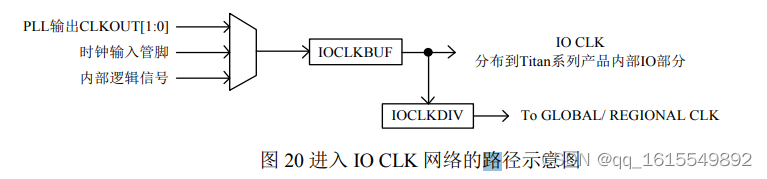

IO_CLK

可以看到有3个模块组成。

ioclkbuf

相当于一个gate

ioclkmux

选择

ioclkdiv

分频比,“2”; “3.5”; “4”; “5”

为什么PLL_CLKOUT[2/3/4]不能连接到IO_CLK?

unknown

DDC(Dedicated DQS Circuit)是每个 IO GROUP 配有一个专用的 DQS 控制电路,主要用于 DDR memory 接口应用。

DCC(Dedicated CDR Circuit),为专用 CDR 电路,可用于高速异步输入接口应用。

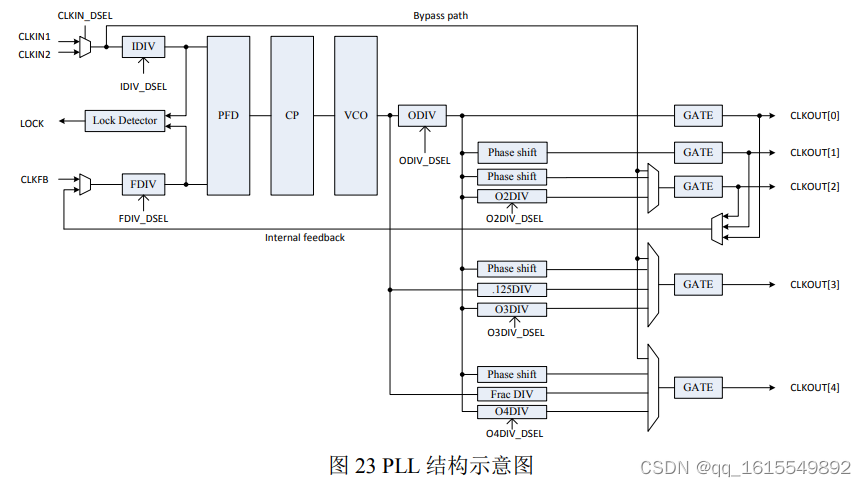

PLL

频率鉴相器(PFD)

CP(Charge Pump)

VCO 频率锁定在 600MHz~1.3GHz 之间。

反馈时钟为CLKOUT[0]时:

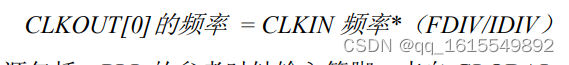

PLL的源有哪些?

时钟源切换后需要对 PLL 复位以便它重新锁定。

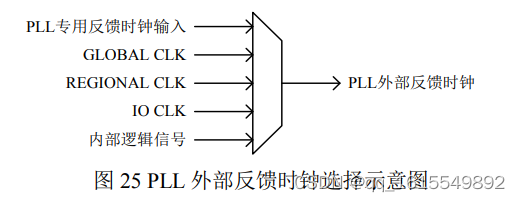

PLL外部 FB的源有哪些?

在 VCO 锁定 LOOP 内的时钟不能被 GATE:例如选择 CLKOUT[0]内部反馈时,该时钟输出不应被动态 GATE。

PLL 时钟输出端口 CLKOUT[1]~CLKOUT[4]均支持可选的相位调节功能,相位调整的粒度为 1/8个时钟周期。

PLL 的 CLKOUT[2]支持输出频率的进一步分频,CLKOUT[2]的分频比由 O2DIV 决定,选中时:

CLKOUT[2]的频率 = CLKOUT[0]的频率/O2DIV

CLKOUT[3]支持输出频率的进一步分频,包括 O3DIV 决定的分频和支持基于 0.125 的简

易小数分频。选择 O3DIV 模式时:

CLKOUT[3]的频率 = CLKOUT[0]的频率/O3DIV

选择基于 0.125 的简易小数分频模式时:

CLKOUT[3]的频率 = (VCO 频率/2)/(M+N*0.125)

其中 M=1,2 . . . 64, N=0,1,…7 (注:当 M=1 时 N!=0)

PLL 的 CLKOUT[4]支持输出频率的进一步分频,包括 O4DIV 决定的分频和支持基于 32bit 计数

器的简易小数分频。选择 O4DIV 模式时:

CLKOUT[4]的频率 = CLKOUT[0]的频率/O4DIV

选择基于 32bit 计数器的简易小数分频时:

CLKOUT[4]的频率 = VCO 的频率/(2^33/Delta)

Delta=1~(2^32-1)

如对 VCO 锁定 LOOP 内的

配置作动态修改后,需要对 PLL 复位。如对其它 output divider 配置作动态修改后,建议使用

RESET_ODIV 端口对分频计数器作复位,并在之后复位 PLL 输出驱动的相关逻辑,以避免死锁。

关键原则

PLL 的端口 CLKIN 和 CLKFB 相位对齐

DLL

PGT180H 芯片有 8 个 DLL,芯片左上角、左下角、右上角和右下角各有两个。DLL 的主要功能是动态锁定输入参考时钟的频率,输出该时钟周期的四分之一等效 delay step 数目。这个 Delay step可实时追踪温度和电压的变化

[1] PGT180H时钟UG

[2] 简述DLL与PLL的区别

![[oeasy]python0020换行字符_feed_line_lf_反斜杠n_B语言_安徒生童话](https://img-blog.csdnimg.cn/img_convert/dd3bb4fa4dae2a240ff8d0840c6293f2.jpeg)

![[足式机器人]Part3机构运动微分几何学分析与综合Ch02-2 平面机构离散运动鞍点综合——【读书笔记】](https://img-blog.csdnimg.cn/d48a229161a04922a30522eecef09cc6.png)