随着比特率继续飙升,光纤编织效应 (FWE) 偏移,也称为玻璃编织偏移 (GWS),正变得越来越成为一个问题。今天的 56GB/s 是高速路由器中最先进的,而 112 GB/s 指日可待。而用于个人计算机和服务器行业的下一代 PCIe 正在迅速转向 64 GT/s。

Skew 可以来自任何对内不对称性,例如: packages;球栅阵列 (BGA) 分线;对内布线长度不匹配;连接器和非对称返回路径过孔,仅举几个例子。其中许多可以通过在设计中指定严格的约束来控制。但是,由于 FWE 本质上是统计的,因此控制它引起的时序偏差可能是最困难的,而且在这些数据速率下,它实际上会毁了你的一天。

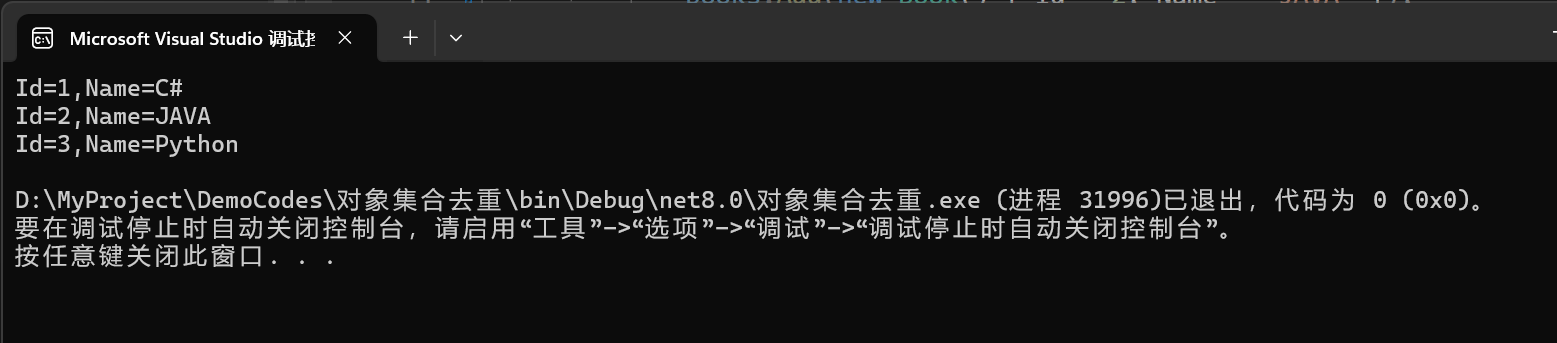

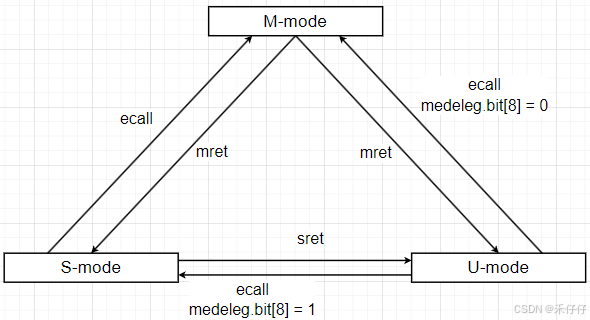

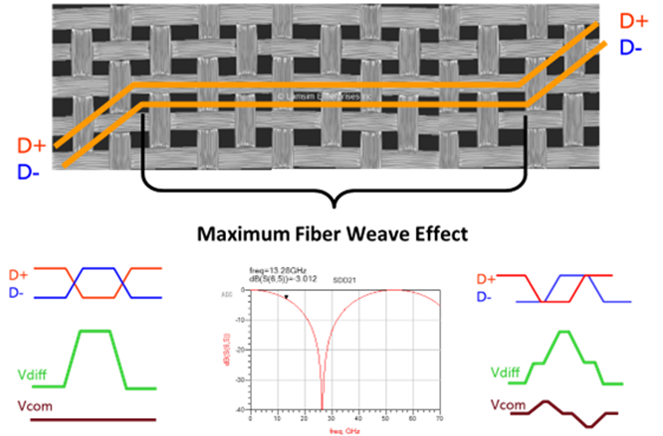

图 1:差分对布线的光纤编织效应示例,显示顶部走线在其部分长度上布线在低树脂填充玻璃纤维束上,而底部走线则主要在较高的树脂填充上布线。正 (D+) 和负 (D-) 信号之间的时序偏移将导致 SDD21 插入损耗中出现谐振零点,并将一些差分信号转换为公共信号分量。

FWE 是玻璃纤维增强电介质基板导致相同长度的对内时序偏斜时常用的术语。由于印刷电路板 (PCB) 制造过程中使用的介电材料由编织成布并浸渍环氧树脂的玻璃纱制成,因此它变得不均匀。

如图 1 所示,当顶部走线在其部分长度的低树脂填充玻璃编织区域上布线时,与在高树脂填充玻璃编织区域上布线的底部走线相比,它将具有不同的传播延迟。delay 的差异称为 timing 或 phase skew。

信号沿传输线传播的速度取决于材料的相对介电常数 (er),也称为介电常数 (Dk)。Dk 越高,信号传播越慢。

由于现代串行链路接口在一对相同长度的传输线上使用差分信号,因此正 (D+) 和负 (D-) 信号之间的任何时序偏移都会将一些差分信号转换为公共信号分量。最终,这会导致接收器的眼闭,并导致电磁干扰 (EMI) 辐射。

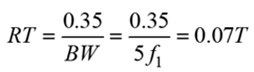

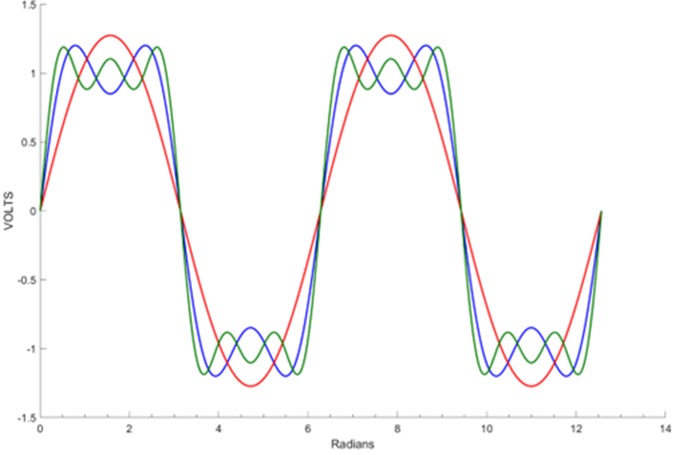

时域中的 timing skew 在频域中表现为谐振零点,如图 1 所示。在此示例中,如果 timing skew 等于波特率的二分之一单位间隔 (UI),则 D+ 和 D- 信号将偏移 90 度,谐振零将出现在波特率的频率处。

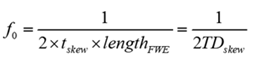

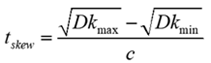

如果您知道对内时序偏斜 (tskew) 和 FEW 长度,则可以使用以下公式预测谐振频率 (fo):

方程 1

哪里:

每单位长度秒数

lengthFWE = 最大 FEW 长度

c = 光速 = 2.998E+8 米/秒(1.18E+10 英寸/秒)

Dkmin 、 Dkmax 是由于玻璃编织而产生的最小和最大有效 Dk。

当 TD偏移等于 1 UI 时,D+ 和 D- 信号将偏移 180 度并彼此同相。谐振零点将出现在奈奎斯特频率处,等于波特率的一半,并且眼图将完全闭合。

根据定义,波特率是每个 UI 传输的符号数。对于不归零 (NRZ),波特率等于符号或比特率。对于脉冲幅度调制 4 级 (PAM-4) 信号,每个 UI 有两个符号,波特率是比特率的一半。因此,对于 56 GB/s PAM-4,波特率为 28 GBd。对于 IEEE802.3bs,以太网 400G 标准,波特率为 26.56 GBd,PAM-4,用于本研究。

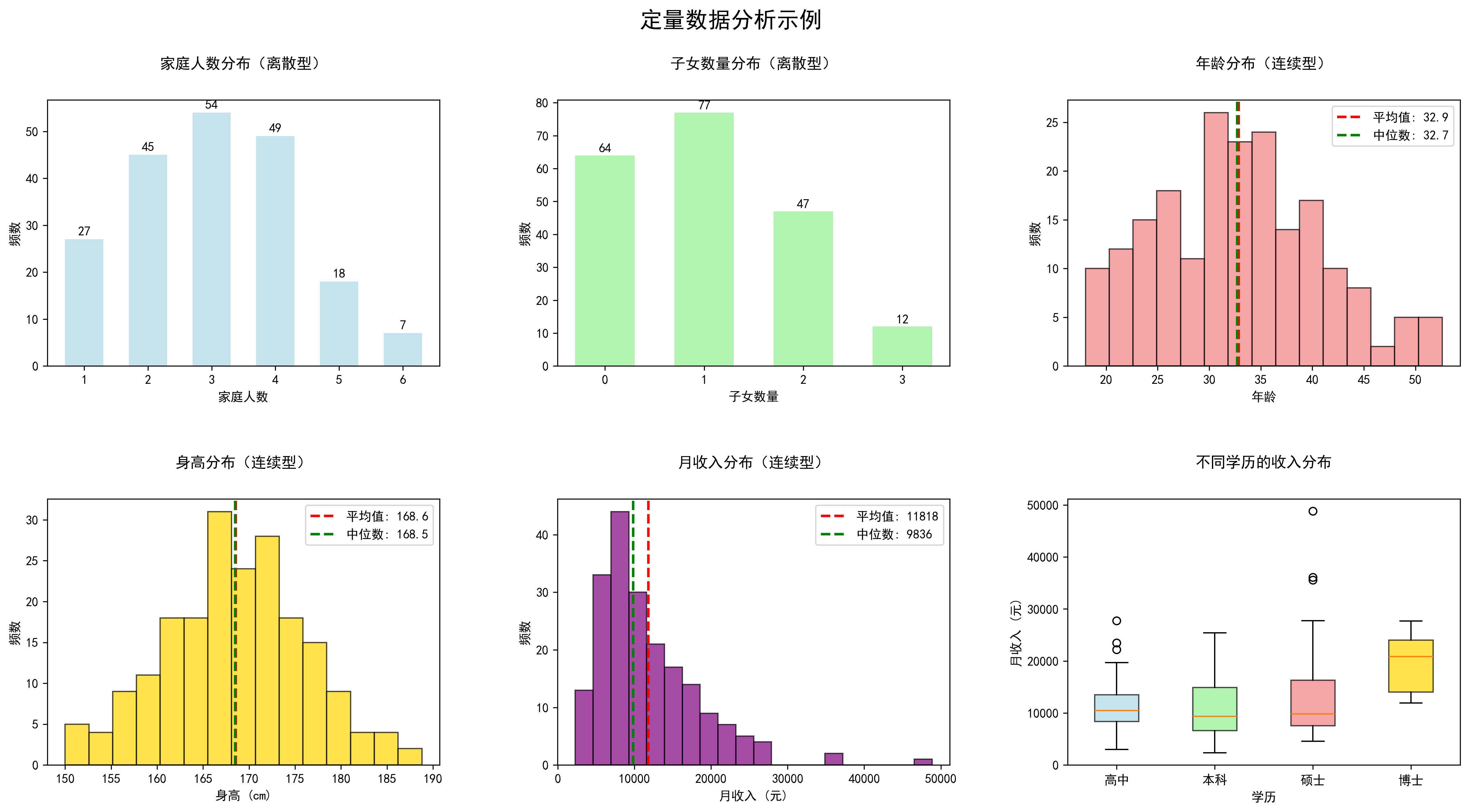

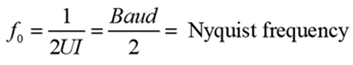

PAM-4 信令的偏斜问题会加剧,如图 2 所示。在这些示例中,模拟无损传输线仅用于显示由于偏斜而导致的眼图闭合效应。当然,没有无损传输线这样的东西,但严格隔离由于偏斜引起的损耗是一种有用的方法。如图 2 (a) 所示,当 0UI 的偏移时,通道损耗是平坦的,眼睛是睁大的。

由于 FWE 偏斜,频域中的谐振零点表现得像陷波滤波器。根据 Q 因子,接近谐振的频率将被衰减。如果谐振零点出现在奈奎斯特频率附近,则眼图将减小。在图 2 (b) 的示例中,当 0.5UI 或 18.8 ps 的偏移时,波特率处存在谐振零点,在 13.28 GHz 奈奎斯特频率下插入损耗为 -3 dB。这会导致眼高 (EH) 降低 153 mV,抖动增加 10 ps。

当偏移为 1UI 或 37.65 ps 时,如图 2 (c) 所示,谐振零点位于奈奎斯特频率,眼图完全闭合。对于有损通道和其他损伤,闭眼只会变得更糟。

图 2 FEW 偏斜对无损传输线的影响示例。

总偏度预算

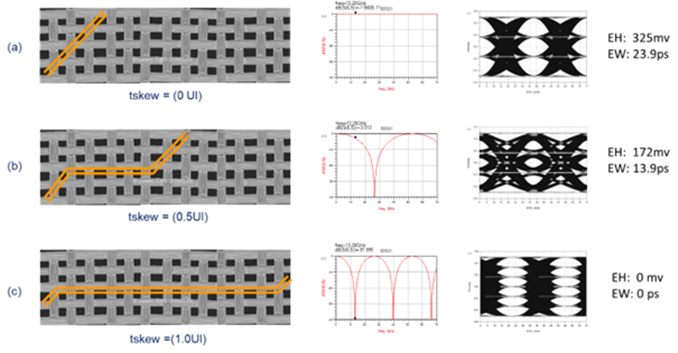

根据经验,我们通常努力使互连带宽 (BW) 为比特率奈奎斯特频率的 5 倍。这遵循许多示波器制造商的上升时间 (RT) 带宽乘积等于 0.35 的规格。

方程 2

RT x BW = 0.35

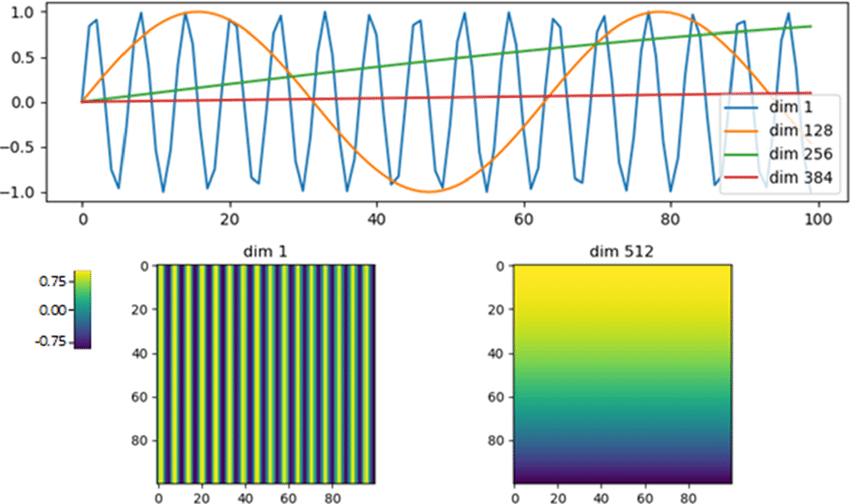

五乘奈奎斯特表示傅里叶级数的 5次谐波正弦分量,如图 3 所示。高达 5次谐波的互连 BW 可将上升时间的完整性保持在基频 (f1) 周期 (T) 的 7% 处。

方程 3

因此,对于奈奎斯特频率为 13.28 GHz 的 26.56 GBd 数据信号,需要 66.4 GHz 的带宽才能保持 5.27 ps 的 RT。

图 3 基频的 5次奇次谐波的傅里叶级数

一些行业标准将通道中所有来源的总倾斜预算限制为 0.2UI。但是,这对于今天的 PAM-4 系统来说足够吗?

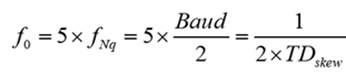

UI 的 20% 将导致频率 (f0) 等于奈奎斯特频率 (fNq) 的 5 倍的谐振零。

如果;

方程 4

然后;

方程 5

在 26.56 GBd 时,只有 7.53ps!

但是 0.2UI 会消除奈奎斯特频率的 5次谐波。从历史上看,对于不归零 (NRZ) 和较低的波特率,有更多的裕量,但对于 PAM-4,信噪比 (S/N) 损失为 -9.5dB,0.2UI 可能会进一步增加通道裕量。

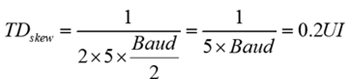

因此,一个好的经验法则是确保第一个零出现在奈奎斯特频率的 7次谐波处;保持 5次谐波频率分量的完整性。这意味着总偏斜预算为 0.14UI:

方程 6

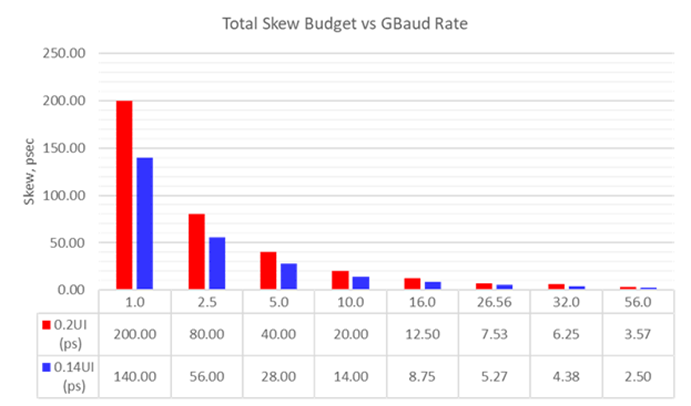

图 4 比较了 0.2UI 和 0.14UI 的总偏斜预算与常见的行业标准波特率。如图所示,随着波特率的增加,偏斜预算呈指数级下降。对于 0.14UI,26.56 GBd 的总偏斜预算为 5.27ps,而 56 GBd 时仅为 2.5ps。由于这是总的偏斜预算,因此留给 FWE 偏斜预算的预算并不多!

图 4 0.2UI(红色)和 0.14UI(蓝色)总偏斜预算与行业标准 Gbaud 速率的比较图。

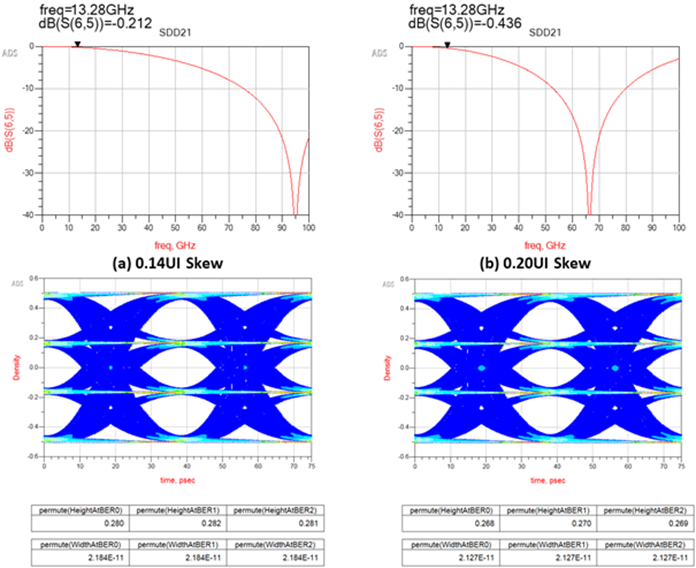

图 5 比较了两个无损差分对仿真,增加了 0.14UI (a) 和 0.20UI (b) 的偏移。眼图显示,在 13.28GHz 奈奎斯特频率处,插入损耗为 0.22dB delta,中心 EH 额外降低 12 mV,抖动增加 0.57ps;由于频率的谐振零点偏移,低至 66.4 GHz (b)。

图 5 添加了 0.14UI (a) 和 0.20UI (b) 偏移的无损差分对仿真。在 13.28GHz 奈奎斯特频率下,插入损耗为 0.22dB 增量,中心磁场损耗额外增加 12 mV,并且由于频率低至 66.4 GHz 的谐振零点偏移 (b),抖动增加了 0.57ps。

现实

对于无损通道,12 mV 似乎无关紧要。但这不是现实。真实通道具有损失和其他损伤,这将进一步侵蚀眼图的张开度。此外,许多规范对总损耗有限制。

IEEE 802.3bs 芯片模块 (C2M) 规范 [3] 在 13.28 GHz 时具有 10.2 dB 的严格插入损耗 (IL) 模板规范。同一文档的表 120E-1 规定,在 TP1a 下,最小差分眼高 (EH) 为 32 mV,眼对称模板宽度 (EW) 为 0.22UI 或 8.23ps。

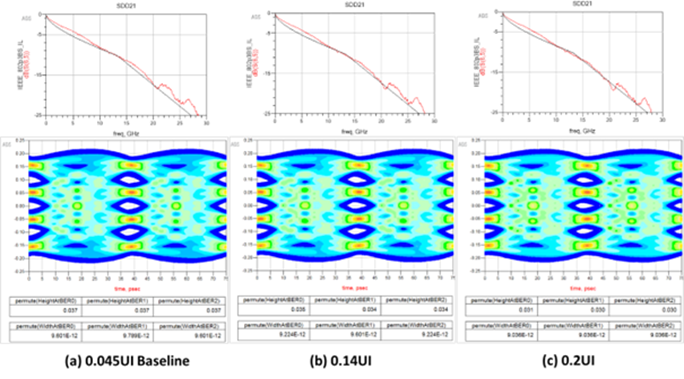

图 6 显示了真实芯片 C2M 通道的 IL 和 PAM-4 眼图的仿真结果。最坏情况下的电源-电压-温度 (PVT) 用于包括封装在内的发射器型号。图 6 (a) 显示了固有通道的结果,包括所有损伤。它以 1.7ps 或 0.045UI 的偏斜为基准。通道损耗刚好满足 IL 模板,眼图满足 IEEE 802.3bs EH 和 EW 并有余量。

图 6 (b) 和 (c) 将总偏斜分别增加到 0.14UI 和 0.2UI 的等效值。随着偏移的增加,IL 会因谐振零点频率降低而降低。在 0.14 UI (b) 时,IL 刚刚开始在奈奎斯特频率断点附近违反 IL 模板,EH 和 EW 仍在规格范围内。但在 0.2UI (c) 时,IL 略差,EH 刚好达不到 32mV 规格;但通过了 EW 规范。

在 10-5 比特率误差比 (BER) 下测得的最小眼图高度和宽度为:

a) 0.045UI (37; 37; 37) mV 和 (9.601; 9.789; 9.601) ps – EH/EW – 通过

b) 0.14UI (35; 34; 34) mV 和 (9.224; 9.601;9.224) ps – EH/EW – 通过

c) 0.20UI (31; 30; 30) mV 和 (9.036; 9.036; 9.036) ps – EH – FAIL / EW – PASS

图 6 当总偏斜从基线 0.045 UI 偏斜增加到 0.14 UI (b) 和 0.20 UI (c) 时,真实芯片 C2M 通道的 IL 和 PAM-4 眼图的模拟结果。

FWE Skew 预算

由于 FWE 是玻璃编织样式、树脂化学成分、痕量几何形状和叠层参数等因素的函数,因此很难从数据表中确定精确的 delta Dk。[1] 的一项实际研究表明,最大 FWE 偏差为 45 ps,超过 7.5 英寸。这表示 6 ps/inch 的 FWE 偏斜。这些板被设计为带状线结构,使用 Megtron-1035 芯和预浸料的双层 6 宽编玻璃。

这是对现代多千兆位设计的现实研究。但是多层叠层的复杂性并不能确保每层的玻璃束在走线的上方和下方完美对齐。事实上,当观察横截面时,每层的玻璃束彼此偏移,这将改善 FWE 偏斜结果。遵循 [2] 中的方法将得到更悲观的 9.46 ps/in,您可能会在单层结构的微带中体验到。

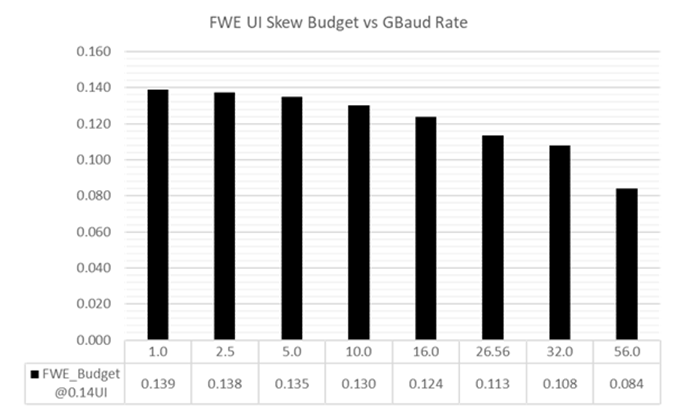

如果我们为所有损伤(如长度匹配、连接器、分线等)预算 1 ps 的偏斜,我们可以为各种波特率建立 FWE 偏斜预算。图 7 绘制了 FWE UI 偏斜预算与波特率的关系,假设总偏斜预算为 0.14 UI。我们观察到高达 10GBd 左右,其他损伤的 1ps 偏差可以忽略不计。但在 10 GBd 之后,它开始影响 FWE 偏斜预算。在 26.56 GBd 和 32 GBd 时,它大约是 0.11 UI,而在 56 GBd 时,它只有大约 0.08 UI!

图 7:假设总偏斜预算为 0.14 UI,则 FWE UI 偏斜预算与波特率的关系

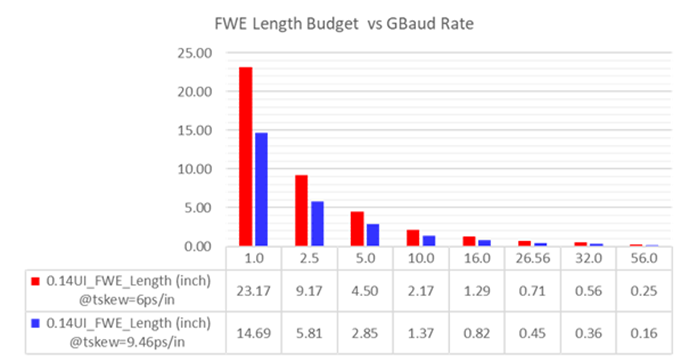

在 6 ps/inch 的 FWE 偏斜 [1] 下,计算出 FWE 长度以满足 0.14UI 的总偏斜预算,并绘制与 Gbaud 速率的关系图,如图 8 中的红色所示。如果使用 9.46 ps/in,按照 [2] 中的方法,FWE 长度显示为蓝色。

正如我们所看到的,当 Gbaud 速率呈指数级上升时,FWE 长度呈指数级下降。超过 10 GBd,如果不采取进一步的缓解技术,FWE 将变得越来越难以控制。在 26.56 GBd 和 6 ps/in 的倾斜时,最大长度为 0.7 英寸;在 56 GBd 时,它只有 0.25 英寸。但是对于 9.46 ps/in 的偏移,长度在 26.56 GBd 时减少到大约 0.5 英寸,在 56 GBd 时减少到大约 0.2 英寸!

流行的 FWE 偏差缓解技术包括:

·选择一种玻璃样式,其中玻璃条以机械方式展开以填充富含树脂的窗户。

·差分对的 Zig-zag 或随机布线。

·选择差分对间距以与玻璃式间距对齐。然而,这并不总是可行的,因为不同玻璃样式的经纱和填充纱可能具有不同的螺距。

·在 PCB 面板上将图稿旋转 7-10 度。

有时需要不止一种这些技术。

图 8:FWE 长度预算与 GBaud 速率的关系,假设总偏斜预算为 0.14 UI,t偏斜为 6 ps/in(红色)和 9.46 ps/in(蓝色)。

总结和结论

当比特率高于 25 GB/s 时,0.2 UI 总偏移预算已被证明不足以满足某些行业标准的 PAM-4 信令。为了减轻偏斜对眼高和宽的影响,建议将 0.14 UI 用于总偏斜预算,以将信道带宽保持在波特率奈奎斯特频率的至少 7 倍。

高达 10GBd 左右,将其他损伤的非 FWE 偏斜限制为 1 ps,对 0.14 UI 总偏斜预算的影响可以忽略不计。但在 10 GBd 之后,它开始减少 FWE 偏斜预算。在 26.56 GBd 和 32 GBd 时,它大约是 0.1 UI,在 56 GBd 时,它只有大约 0.08 UI!

随着越来越大的开关专用集成电路 (ASIC) 封装和越来越紧密的球栅阵列 (BGA) 间距封装,意味着减少了阻抗控制的线宽和跳出 BGA 引脚区域的空间。同样,用于通过小间距背板连接器进行布线。BGA 逃逸长度约为 0.25 英寸或更长的情况并不少见。在大多数情况下,这些分线点平行于面板的 X-Y 轴。在 56 GBd 时,这就是整个偏斜预算!如果没有进一步的 FWE 偏差缓解技术,这将变得无法管理。

当然,这种分析是基于最坏的情况,并不意味着如果你违反了这个偏斜预算,你的系统就坏了。但它表明,需要对信道进行更详细的建模和仿真,并且可能更多地考虑在信道模型中包括 FWE 偏度预算。这将给设计下一代 112 Gb/s 系统和选择 PCB 介电材料带来严峻挑战。