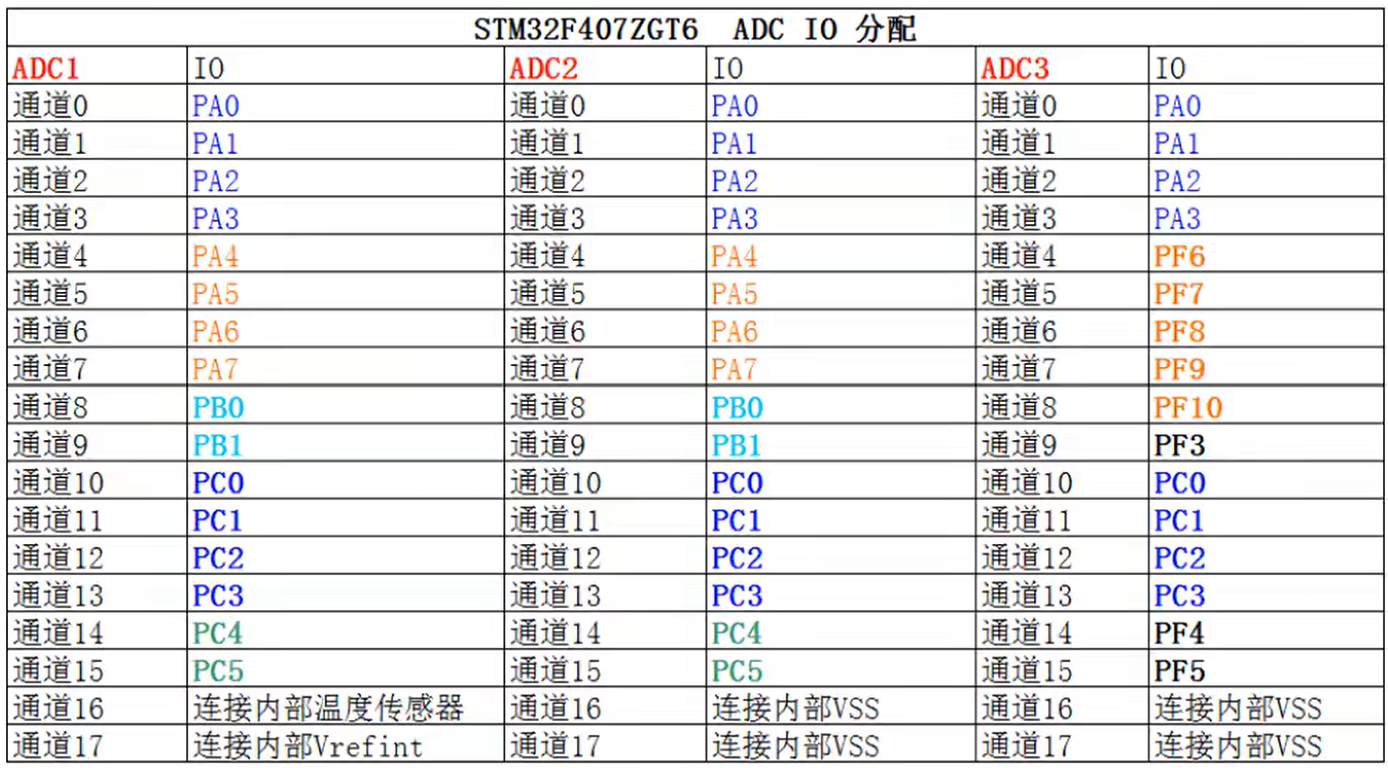

一 多个ADC器件,多重转换速率

每个型号MCU通常由多个ADC器件,比如STM32F4有三个ADC器件,每个ADC器件有一个最大转换速率,一般为2.4Mhz,即一个ADC器件每秒最多转换2.4M次,两次转换之间需要有时间间隔,但是不同ADC器件之间没有转换间隔要求,即一个ADC器件转换完成,可以立即开始下一个ADC转换器件,这也叫做多重转换,这时相当于转换速率提升到2.4*3=7.2M。

二 内部参考电压 VREFINT

①内部参考电压的大小以及连接通道:

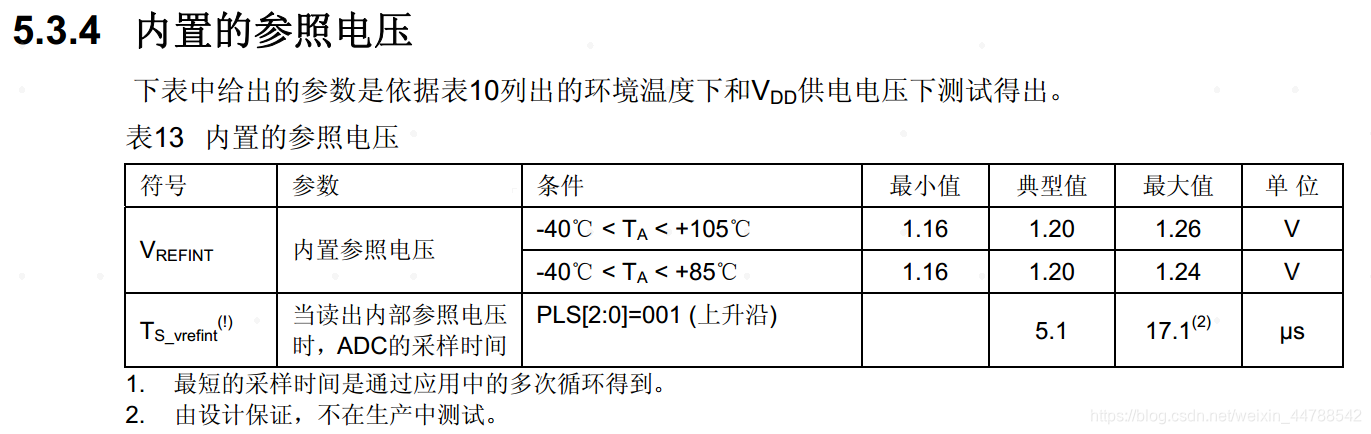

STM32内部有一个参考电压,Vrefint, 这个参照电压的典型值是1.20V,最小值是1.16V,最大值是1.24V(-40~85度)。这个参考电压不随外部供电电压的变化而变化。

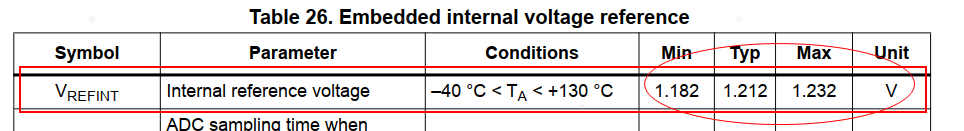

不同的芯片这个参考电压的范围不一样,如下面这个(STM32L475 datasheet):

STM32 的这个内部参考电压 VREFINT 通常接入到 ADC 内部的通道17。

②内部参考电压的作用:

通常情况下STM32的ADC模块采用Vref作为参考电压,Vref内部连接到Vdda,其实也就是供电电压vdd,假如采用的ADC是12位的,那么测得的电压值为:

Vchx=Vdd*(ADchx/4096)

但是在某些情况下,这个供电电压是不稳定的,有可能随外部一些其他用电器工作使用的大电流而导致电压不稳定,还有可能MCU供电LDO转换的精度个别偏差较大。这时候依然用vdd=3.3V的定值做参考电压计算,显然得出的值就会出现与实际电压偏差较大的问题。

而Vrefint的主要作用就是提供一个内部稳定的电压,这个电压不随外部供电电压的变化而变化,推测内部存在稳压二极管器件或者类似电路用来提供此参考电压,我们就可以用它来校正测量电压值从而提高准确性。首先采集并转换17通道ADC值ADrefint,然后采集实际所测量通道ADC值ADchx,那么通过公式

Vchx=VREFINT×(ADchx/ADrefint)

获得实际所测量电压值。

三 过采样

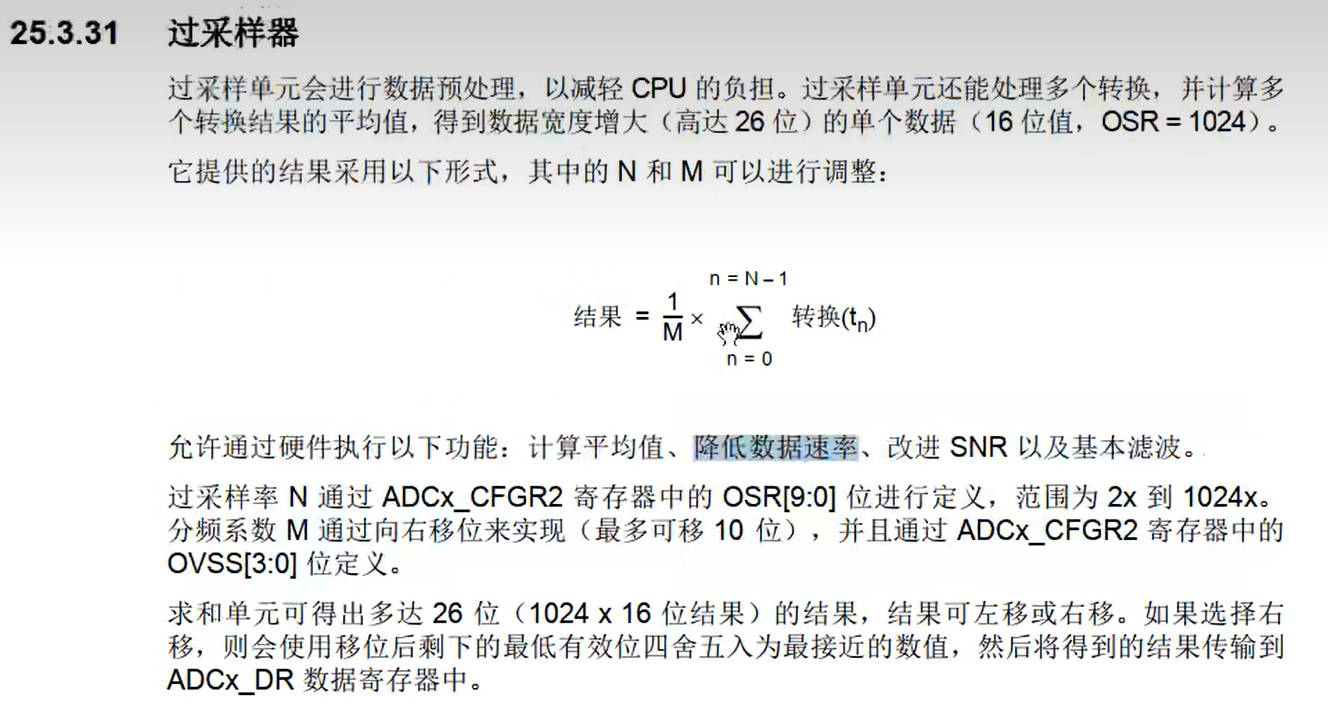

以下为STM32参考手册中对过采样器的描述

过采样提高采样分辨率的原理:

对于12位的STM32,其所能分辨的最小电压(即最小刻度)为3.3V / 2^12 = 0.0008V。在不改进硬件的情况下,可以通过过采样和求均值的方式提高ADC分辨率。

根据增加的分辨率位数计算过采样分辨率频率的方程:

fos = 4^w * fs,fos是过采样频率,w是希望增加的分辨率位数,fs是初始采样频率要求(产品所需实际采样频率)。

比如从12位提升ADC分辨率到16位分辨率,采样频率就要提高256(4^(16-12))倍。将采样结果求和,再将求和结果右移N位(N为用户想提升的位数,本例中为4),就能得到提高分辨率的结果了,这个过程称为抽取.

个人对于过采样的理解,过采样针对的是ADC模块的动态性能,因为ADC模块采集转换的过程本来就是一个动态循环的过程,12位逐次比较要比较4096次,那么只要是动态采集就会有误差,过采样就是消除误差的一种方式。比如12位ADC最高分辨率0.0008,测量一个Vtaget=0.00095的电压,过采样器能输出0.00095的电压,未加过采样器可能仅仅能输出0.0008的电压结果,也就是说ADC的过采样体现在求取0.0008或者说0.00095的过程中。

以下是deepseek对过采样动态性能的回答:

过采样技术的主要应用场景与信号处理的动态性能优化相关,而非直接针对广义的“动态检测”任务。其核心作用体现在以下方面:

过采样的核心功能与应用

-

提升ADC动态性能指标

过采样通过增加采样率(远高于奈奎斯特频率)可显著改善模数转换器(ADC)的信噪比(SNR)、有效位数(ENOB)和动态范围13。例如,4倍过采样可将动态范围增加6 dB(相当于1位分辨率提升)4。 -

抑制噪声与失真

结合噪声整形技术(如叠加白噪声或三角波扰动),过采样能将量化噪声能量分布到高频区域,再通过数字滤波消除带外噪声,从而优化信号重建质量16。 -

扩展系统适用场景

在光谱分析、MRI成像等需要高动态范围的应用中,过采样能够更精确地捕获传感器输出的微弱信号与大动态范围信号3。

与动态检测的关联性辨析

-

间接支持动态信号分析

在环境监测等动态检测场景中,过采样通过提高采样数据的信噪比和分辨率,可为后续的动态信号分析(如污染物扩散追踪、趋势预测等)提供更可靠的底层数据支撑2。 -

技术范畴差异

目标检测等领域提及的“采样”(如平衡正负样本)属于数据增强策略,与信号处理领域的过采样属于不同技术体系,后者侧重于物理信号采集过程的优化7。

结论

过采样本质是针对信号采集环节的动态性能优化技术,而非直接服务于动态检测任务。其价值体现在为动态检测系统提供高质量的基础数据输入,但两者属于不同层级的技术实现。

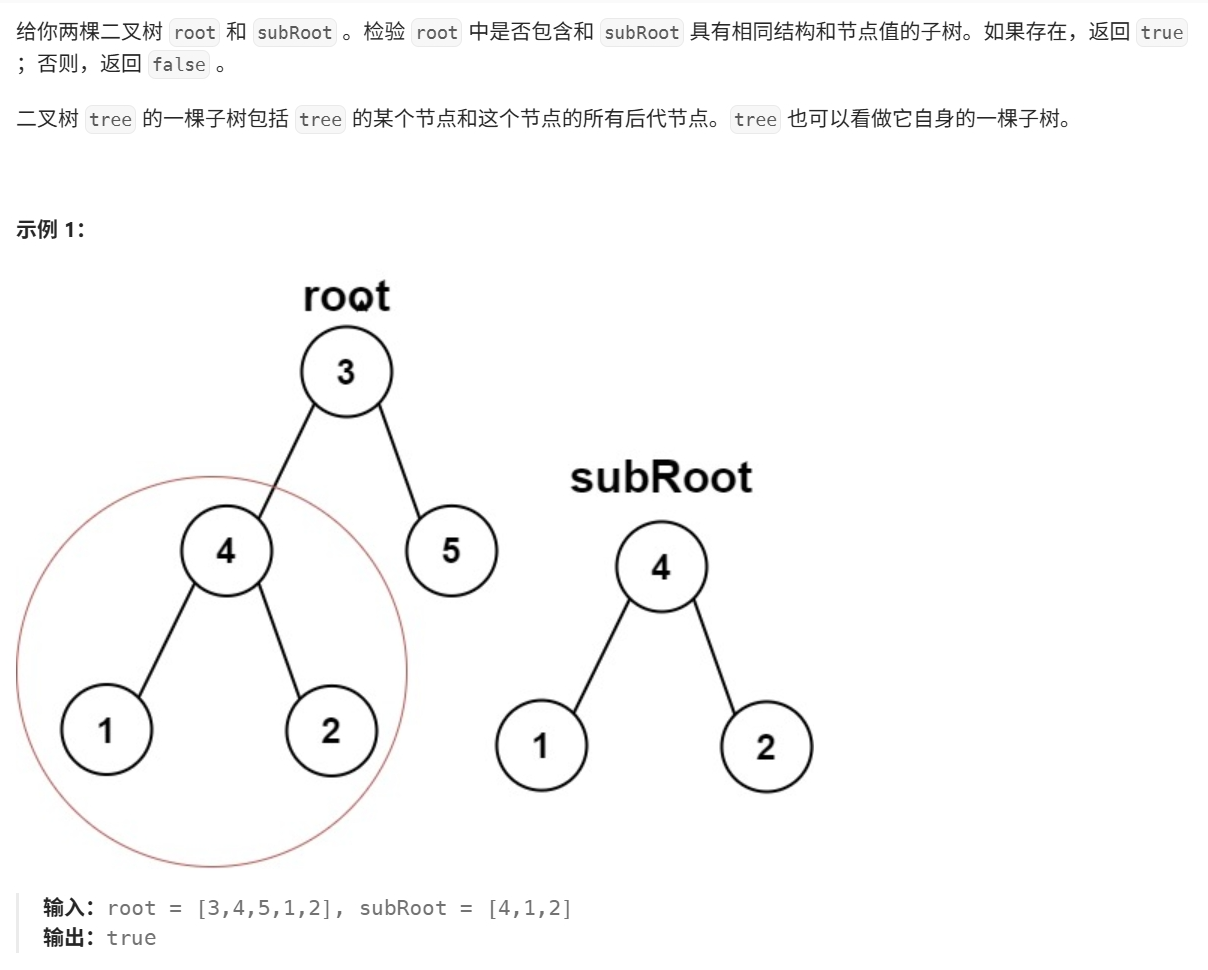

四. ADC内部结构(逐次逼近型内部电路原理机制)

本部分内容转自 ADC采样内部原理及ADC实现高分辨率采样_adc采样原理-CSDN博客

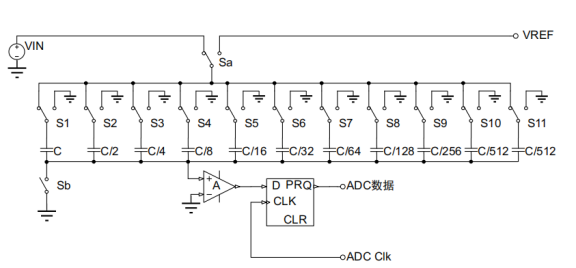

STM32微控制器中内置的ADC使用SAR(逐次逼近)原则,分多步执行转换。转换步骤数等 于ADC转换器中的位数。每个步骤均由ADC时钟驱动。每个ADC时钟从结果到输出产生一 位。ADC的内部设计基于切换电容技术。

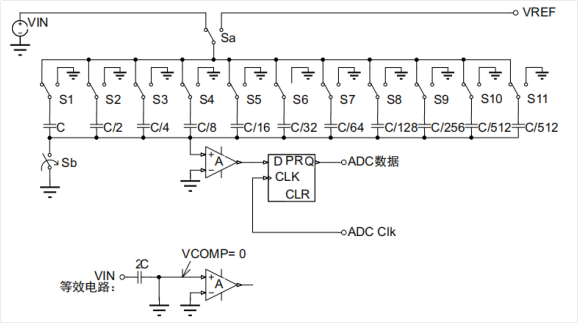

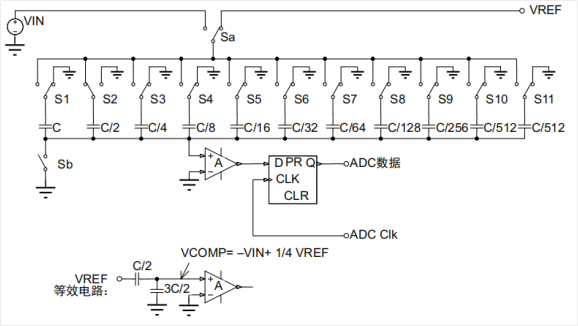

下面的图介绍了ADC的工作原理。下面的示例仅显示了逼近的前面几步,但是该过程会持续到LSB为止

SAR切换电容ADC的基本原理(10位ADC示例)

带数字输出的ADC基本原理图

采样状态

采样状态:电容充电至电压VIN。Sa切换至VIN,采样期间Sb开关闭合

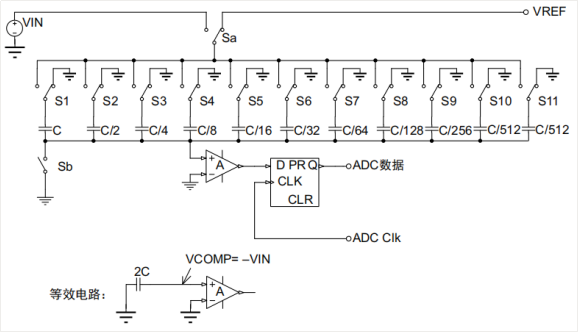

2、保持状态

保持状态:输入断开,电容保持输入电压。Sb开关打开,然后S1-S11切换至接地且Sa切换至VREF。

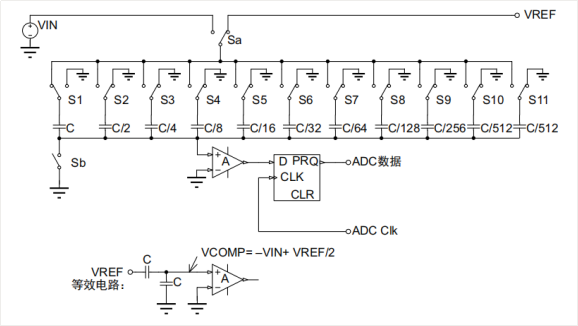

3、逐次逼近

1、第一个逼近步骤。S1切换至VREF。VIN与VREF/2比较

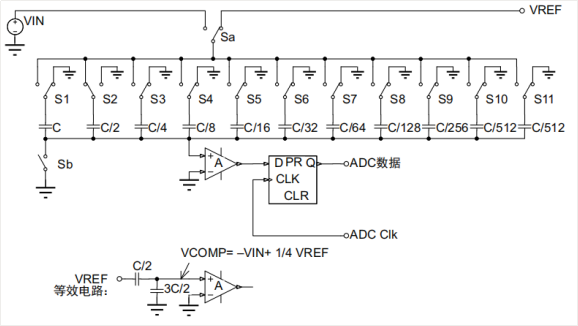

2、如果MSB = 0,则与¼VREF进行比较,S1切换回接地。S2切换至VREF。

3、如果MSB = 1,则与¾VREF进行比较,S1保持接地。S2切换至VREF。

重复如上步骤,直到LSB为止。可以简单理解为二分法逐次进行输入电压与参考电压的比较。首次于VREF/2比较,下次比较根据上次比较结果决定,如果MSB=1则与¾VREF比较。如果MSB=0则与¼VREF比较。后面决定与1/8VREF 3/8VREF、 5/8VREF、 7/8VREF之一做比较。循环直到输出LSB为止。

五, 采样时间

ADC转换时间=采样时间+数据转换时间(跟ADC位数相关,位数越大这个数据转换时间越大)

采样时间:数据手册中定义为最低1.5CLK,即最低1.5个时钟周期,其实这里可以理解为前后两次ADC转换最低间隔时间,也就是给ADC内部电容留出足够的充电时间。

数据转换时间:跟ADC位数相关,位数越大这个数据转换时间越大,比如数据手册中指明12为ADC转换时间需要12.5个时钟周期