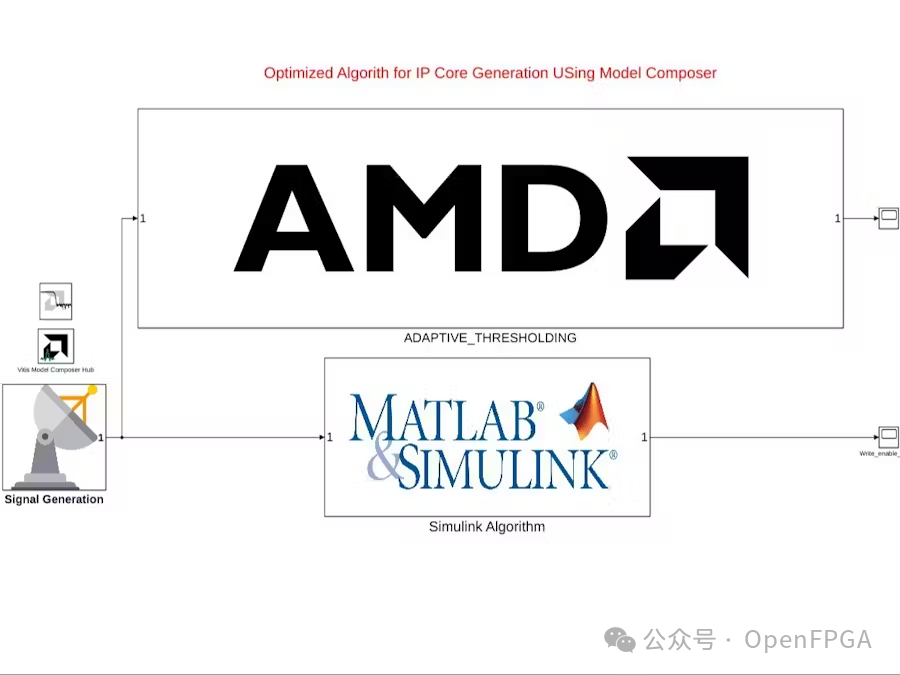

本文将逐步介绍如何使用 Vitis Model Composer 生成 FPGA IP 核,从建模到部署。

在当今快节奏的世界里,技术正以前所未有的速度发展,FPGA 设计也不例外。高级工具层出不穷,加速着开发进程。传统上,FPGA 设计需要使用硬件描述语言 (HDL) 编写代码,并使用综合工具来映射设计。虽然这些传统方法仍然必不可少,但 Vitis Model Composer 和 HDL Coder 等工具已显著简化了开发流程,尤其对于 SDR 和基于 FPGA 的系统而言。正如 BAE 系统公司的一位管理者(David Haessig博士)所说:“一位拥有多年 HDL 编码经验的工程师,使用我们传统的设计流程,手工编写一个功能齐全的 SDR ,需要 645 个小时。而另一位经验有限的工程师,使用 Simulink 和 Xilinx System Generator,在不到 46 小时内就完成了同样的项目。”

今天的教程提供了创建自定义 IP 的分步指南,从算法开发到准备 IP 生成的模型,包括资源和时序分析,最后将其添加到 Vivado IP 目录。

介绍

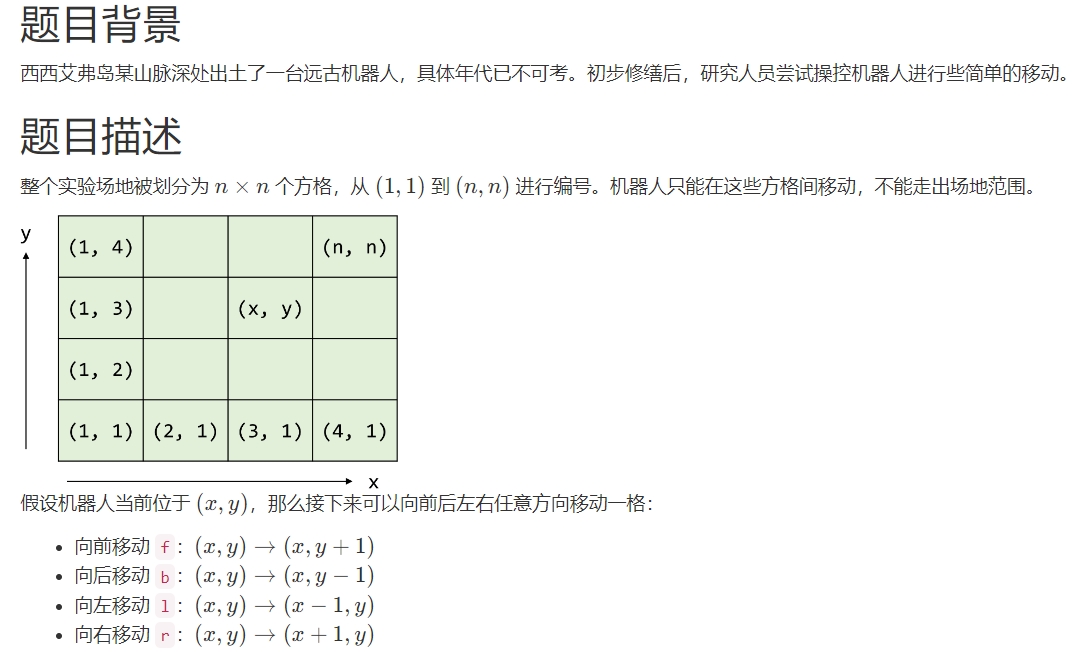

在所有信号处理应用中,在噪声中检测信号至关重要,因为噪声几乎是所有数字系统的固有组成部分。准确的检测是确保可靠通信和数据处理的关键。在今天的教程中,我们将开发一种算法,用于确定未知频率信号中是否存在脉冲。这种检测在处理噪声信号时尤其重要,因为区分脉冲和背景噪声可能非常困难。我们将逐步介绍创建一种高鲁棒算法所需的步骤,该算法可以在噪声环境中有效识别脉冲的存在,无论信号频率如何。

环境设置

Vitis Model Composer 是 Vitis 套件的一部分,该套件为基于 FPGA 的加速提供了高级设计环境。首先设置环境变量:

source /installationDirectory/Vitis/version/settings64.sh获取 Vitis 后,可以通过在终端中执行以下命令来启动 Vitis Model Composer:

model_composer这将打开启用了 AMD 工具箱的 MATLAB。在 MATLAB 中打开 Simulink,现在就可以开始使用 Vitis Model Composer 设计和仿真模型了。

信号生成

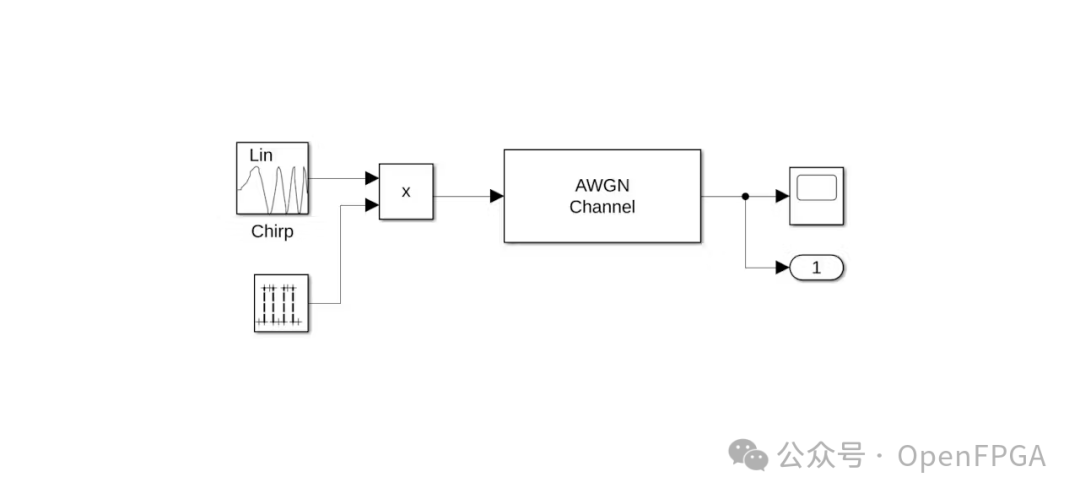

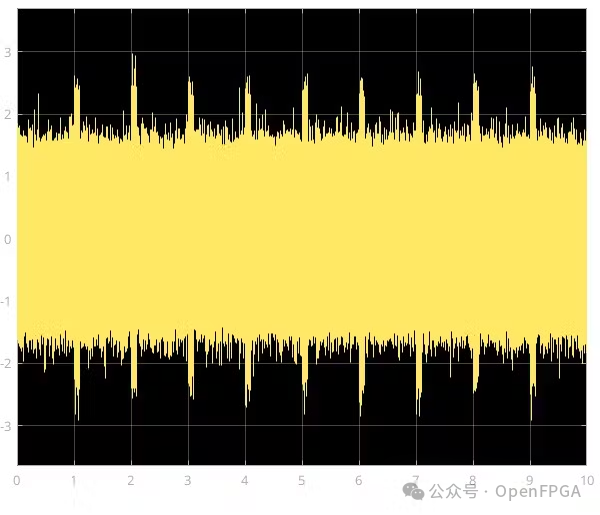

在 Simulink 中,尝试模拟一个chirped pulse信号进行分析。为此,使用 Chirp 模块生成一个调频信号,然后将其与 Pulse Generator 模块相乘,形成不同的脉冲。为了使模拟结果更贴近真实世界,我们在信号中引入了高斯白噪声。这一添加模拟了实际系统中不可避免的噪声,使我们能够分析在噪声条件下信号检测和处理的效果。

生成chirped pulse信号

生成chirped pulse信号

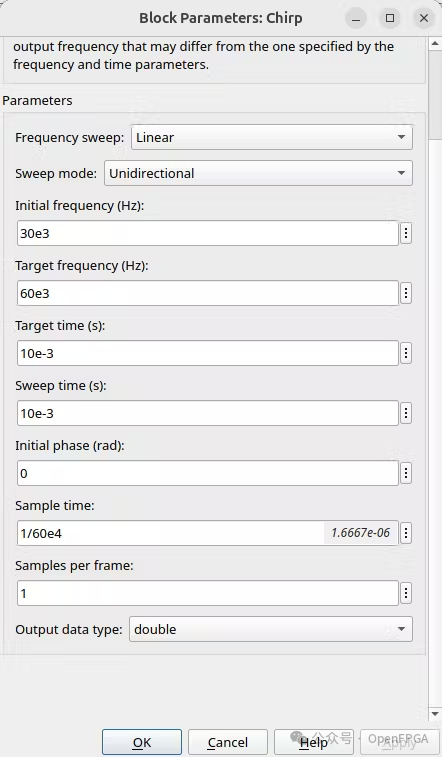

Chirp 模块设置

Chirp 模块设置

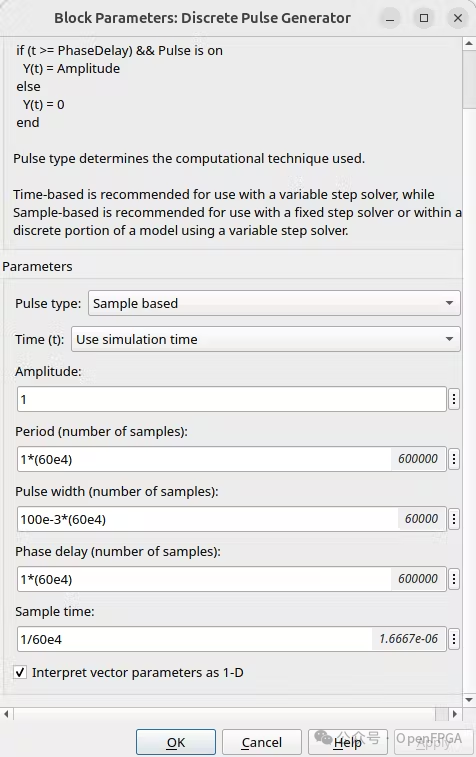

Pulse Generator 模块设置

Pulse Generator 模块设置

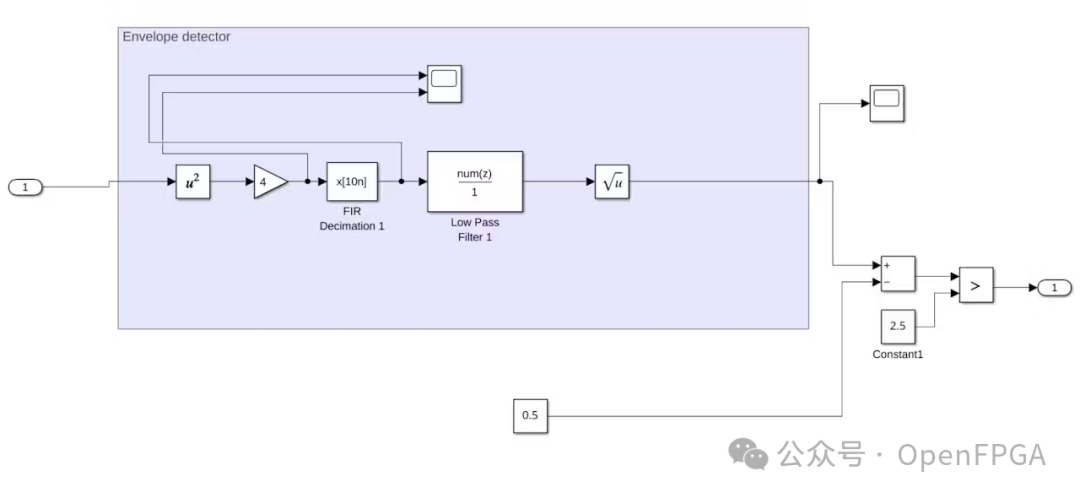

包络检测

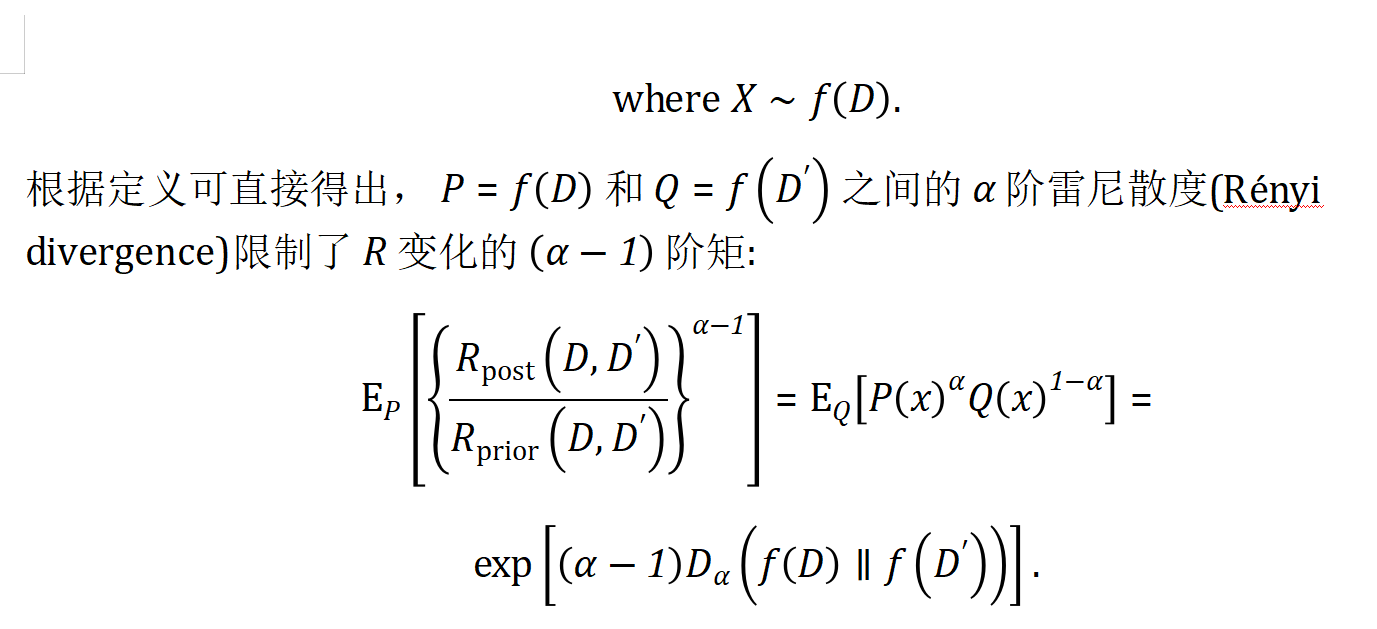

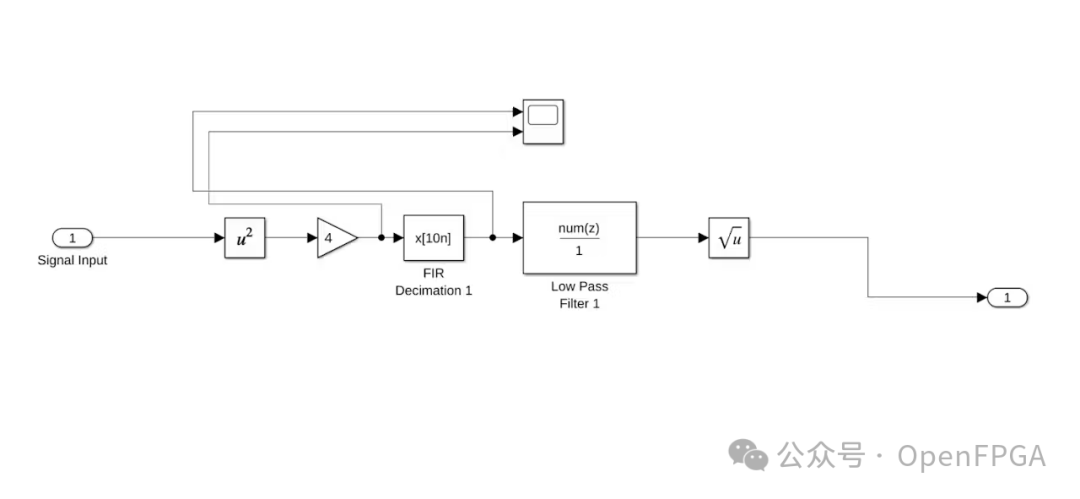

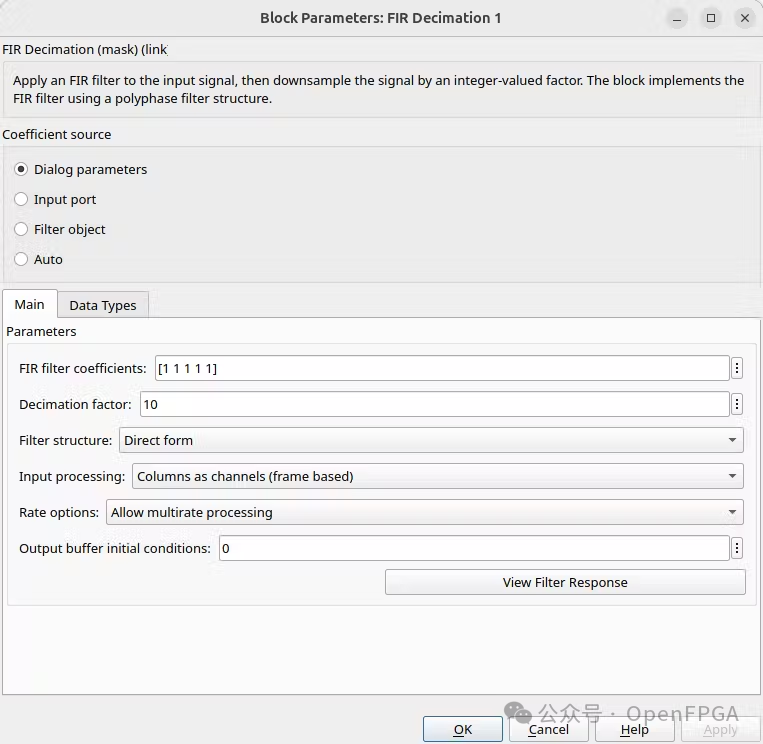

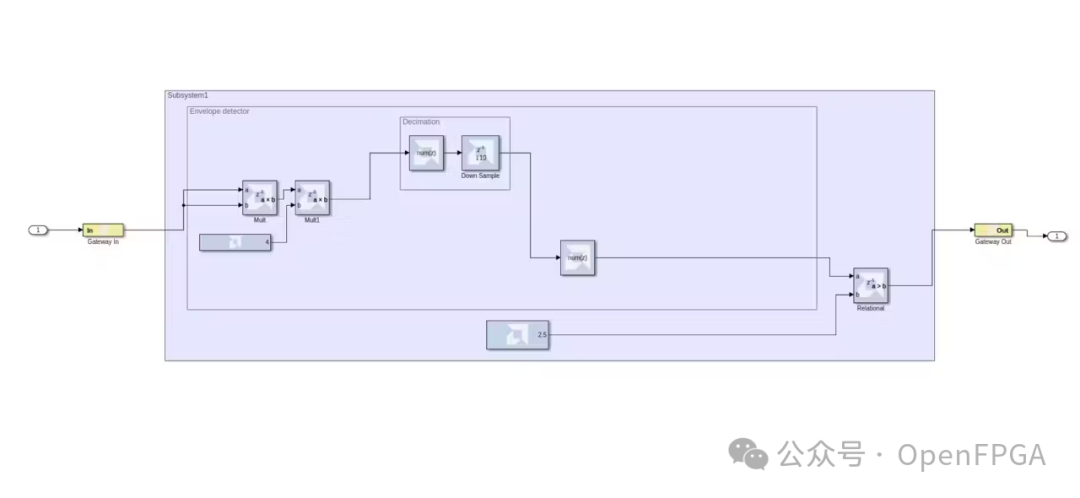

信号生成后,为了实现脉冲检测,我们首先对信号进行平方运算以去除负值,然后进行FIR抽取,最后进行低通滤波。Simulink模块设计如图所示。

FIR 模块设置

FIR 模块设置

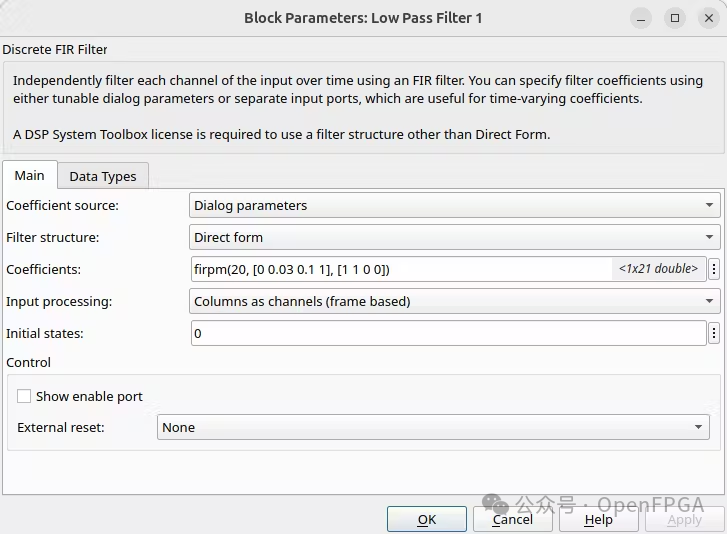

低通滤波模块设置

低通滤波模块设置

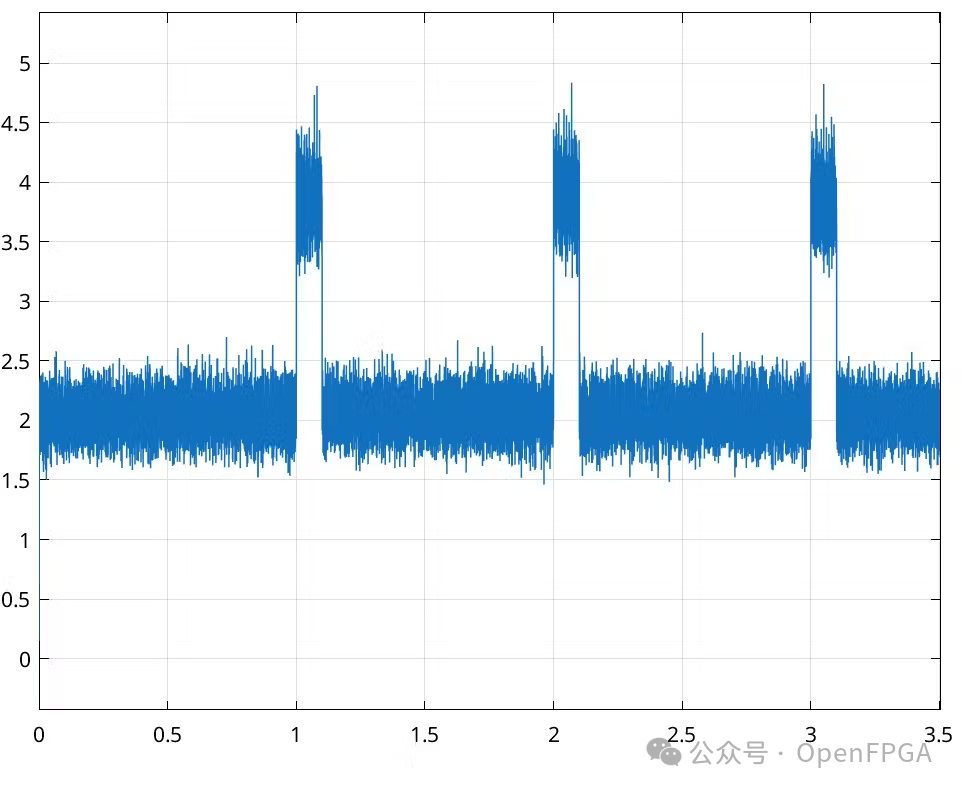

包络提取后的信号如图所示。

如上图所示,在应用包络检测算法后,信号幅度显著增大,有效地将其与噪声区分开来。在噪声区域内,不存在不需要的跳变情况,这使得将脉冲与背景区分开来变得更加容易。这种改进提高了我们准确判断信号中是否存在脉冲的能力,从而实现更可靠的检测。

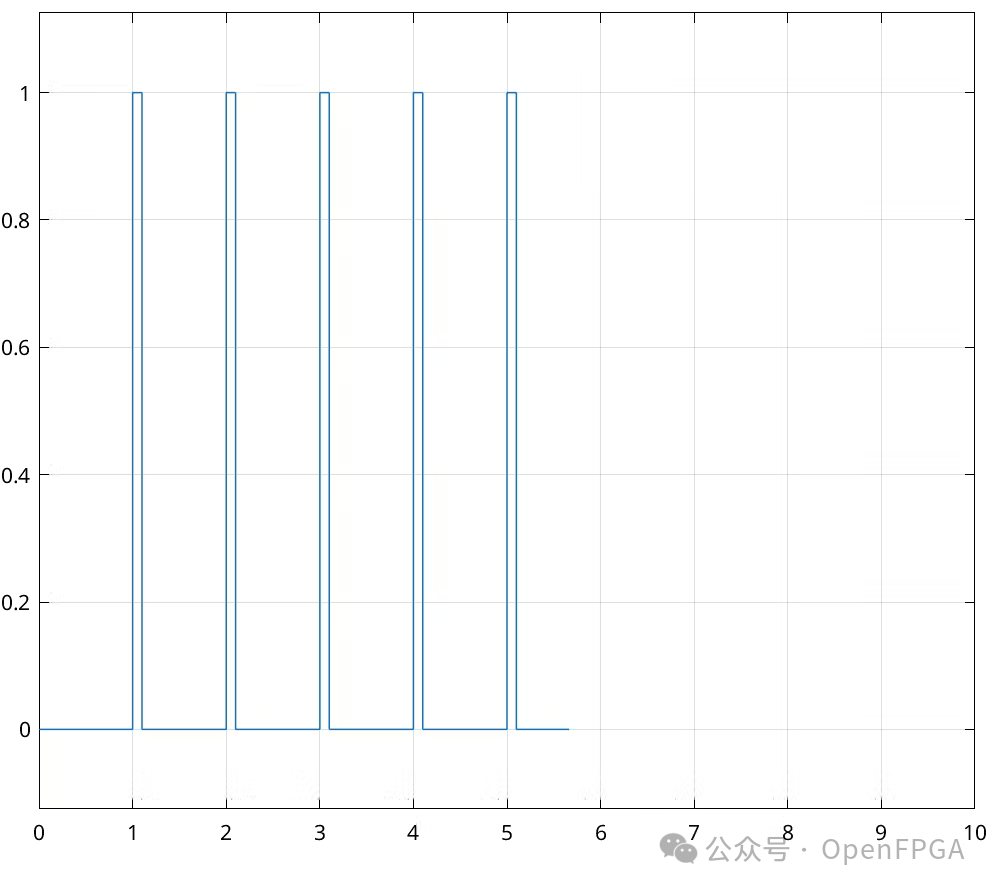

基于信号的后处理,选择一个恒定阈值来确定脉冲的存在变得更加容易。该模块输出“1”或“0”,指示是否检测到脉冲。然而,除了使用固定阈值外,还可以通过使用基于标准差的分析等方法使阈值自适应,进一步改进检测算法。这种方法允许系统根据噪声变化动态调整阈值,提高不同信号条件下的检测精度。最终的 Simulink 模型如下图所示。

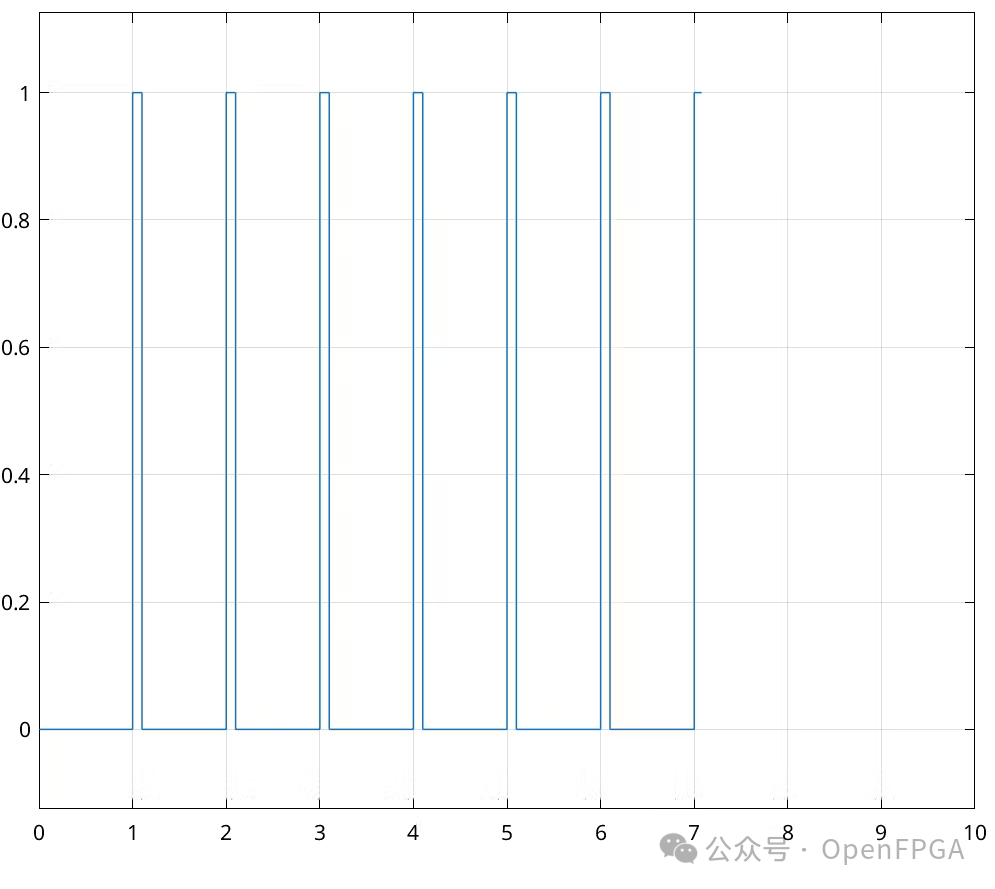

最终结果

检测结果如下:

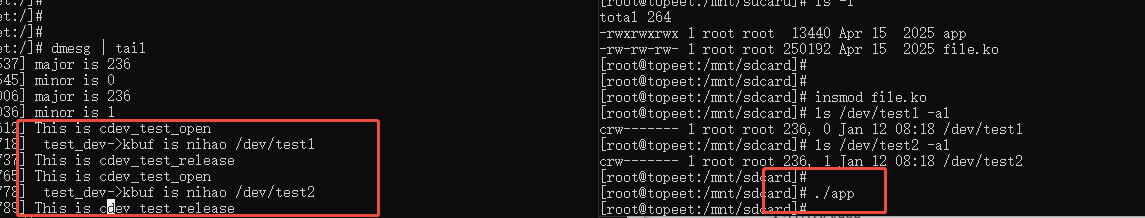

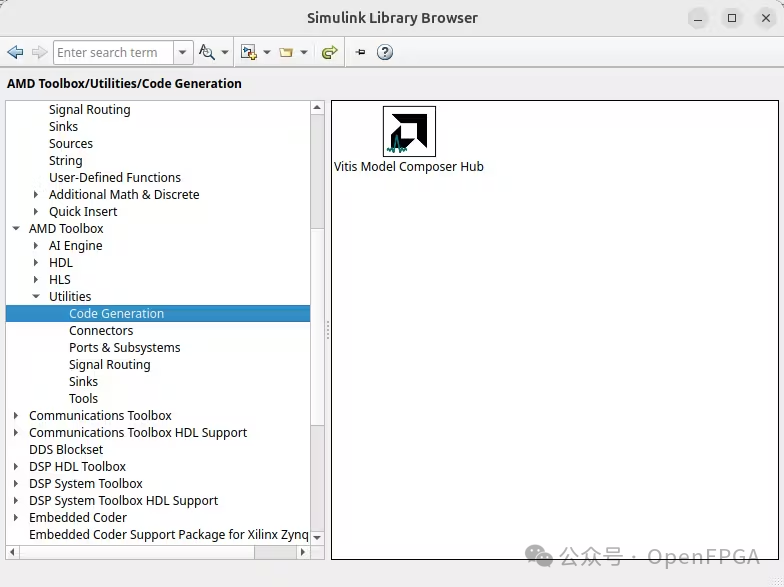

Vitis Model Composer

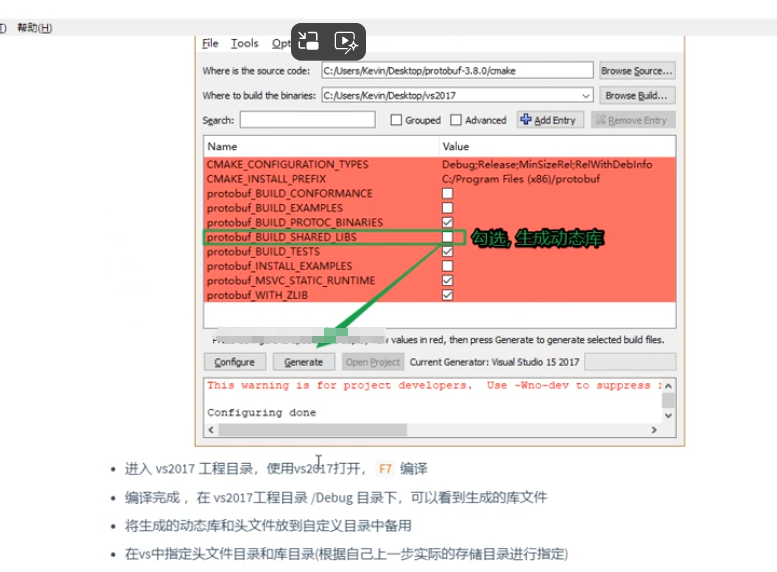

在成功验证多个测试用例的算法后,下一步是使用 Vitis Model Composer 复现类似的结果。要生成 IP 并执行其他相关功能,首先需要从 Simulink 库中插入Vitis Model Composer Hub模块。该模块位于:

Simulink Library Browser → AMD Toolbox → Utilities → Code Generation → Vitis Model Composer HubVitis Model Composer Hub作为中央流程顾问,指导从设计到代码生成的整个过程,确保与 Vitis 工具链无缝集成。

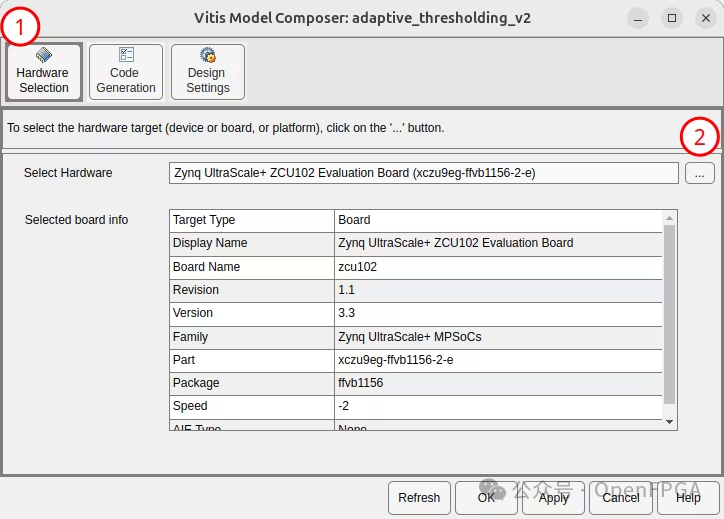

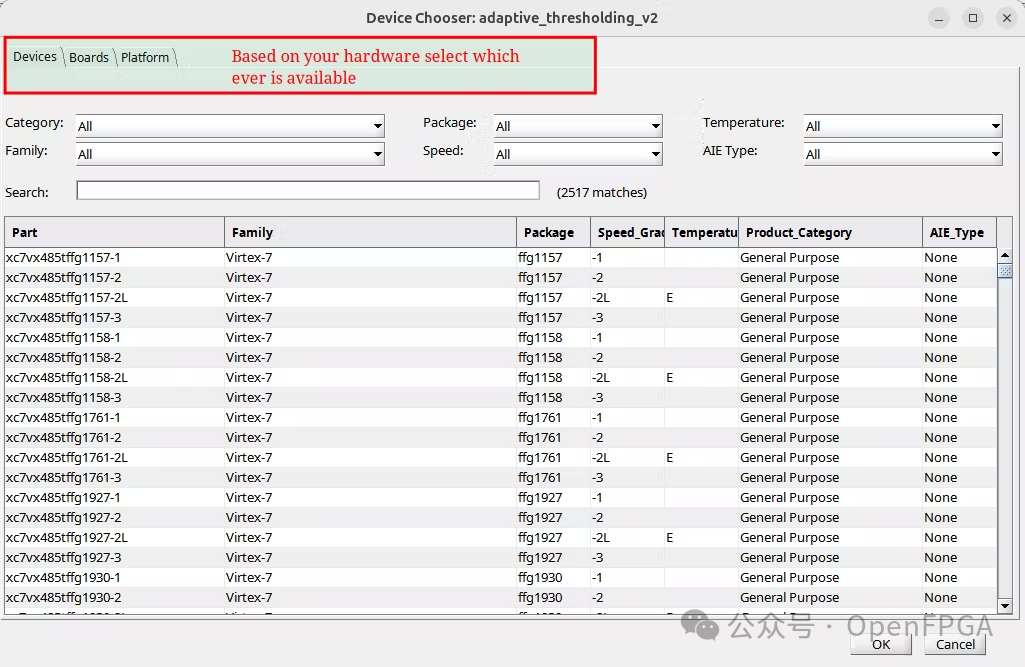

开发板选择

在本文中,使用的是Zynq UltraScale+ MPSoC ZCU102开发板。当然,也可以选择任何Xilinx的开发板。

要选择开发板,请打开Vitis Model Composer Hub并按照下图所示的步骤操作。开发板选择流程可确保生成的 IP 和设计配置与硬件平台兼容。

模型创建

AMD-Xilinx 针对 IP 核生成给出了一些具体的指导原则。要遵循本教程,请牢记以下几点。

Gateway In/Out被视为输入/输出

这些端口之间的任何东西都会被 Vitis Model Composer Hub自动识别,并可以转换为 IP。

为了让Vitis Model Composer Hub能够识别执行待转换为子系统功能的所需模块,AMD 提供了 IP 核生成的具体指南——当然,硬件设计本身还不够复杂!为了成功完成本教程,请记住以下几点:

Gateway In/Out被视为输入/输出。可以将它们视为数据的 VIP 入口和出口。

Vitis Model Composer Hub会自动检测这些端口之间的任何内容,并将其转换为 IP.

为了识别正确,任何执行功能的块都必须转换为subsystems。如果不这样做,Vitis 可能会识别不到他们。

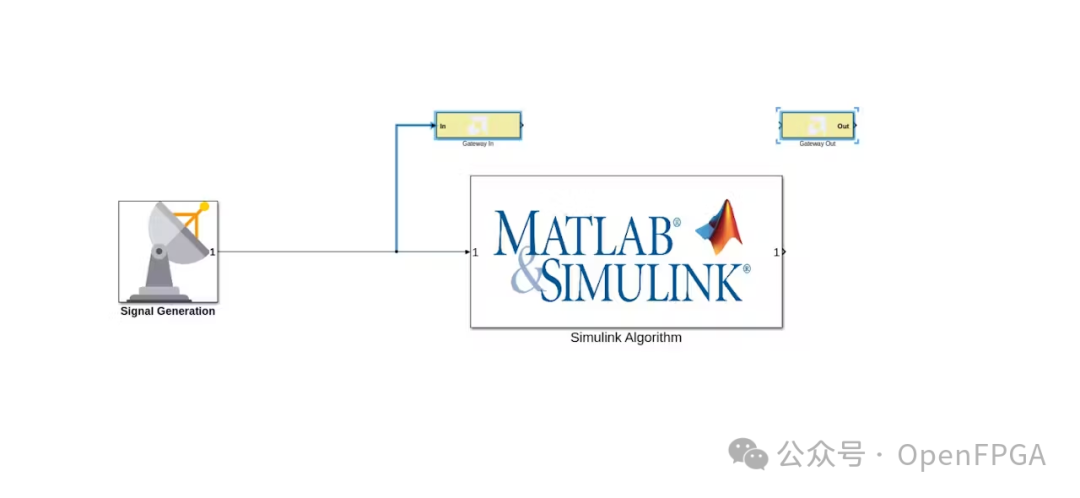

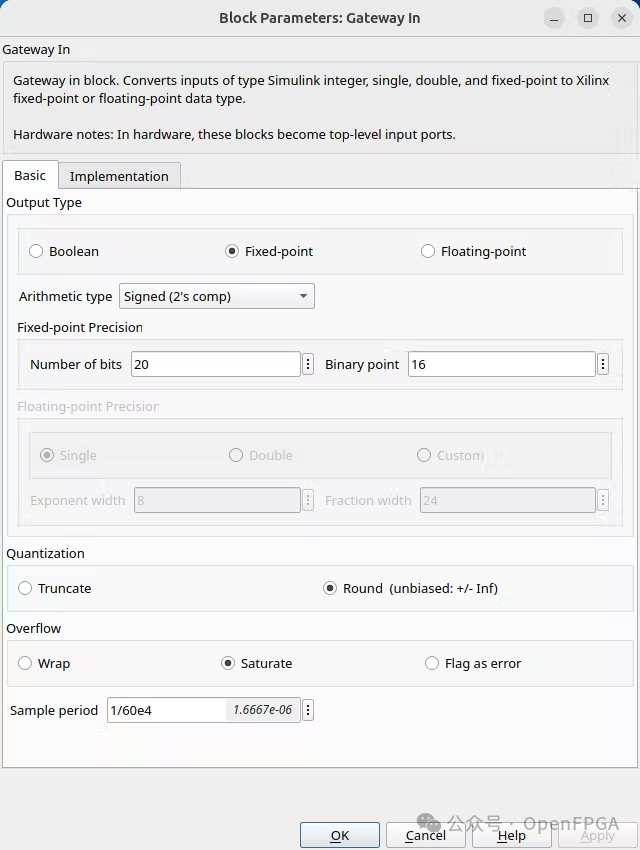

Gateway In/Out

在模块设计中插入Gateway In和Gateway Out模块。

将信号生成子系统的输出连接到Gateway In 的输入。这可以确保你精心制作的信号有一个正确的入口点。

为包络检测算法创建一个子系统,确保它只包含通用的 Simulink 模块。

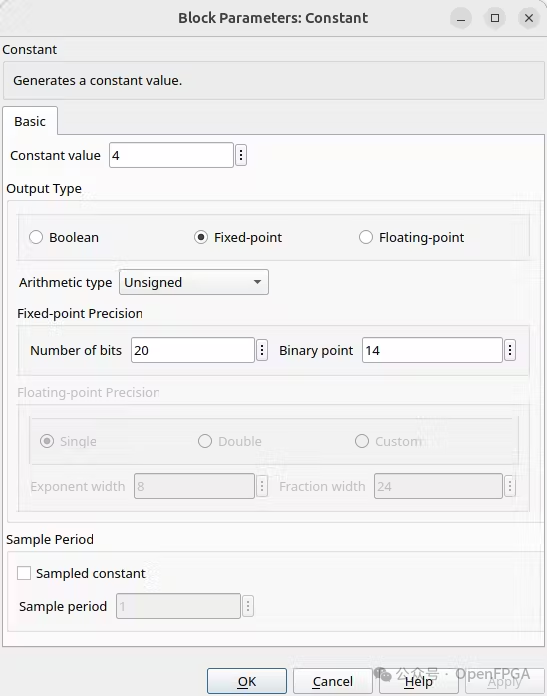

根据下图所示的设置修改Gateway In模块的参数。同时,不要改动Gateway Out模块。

IP 生成的算法复制

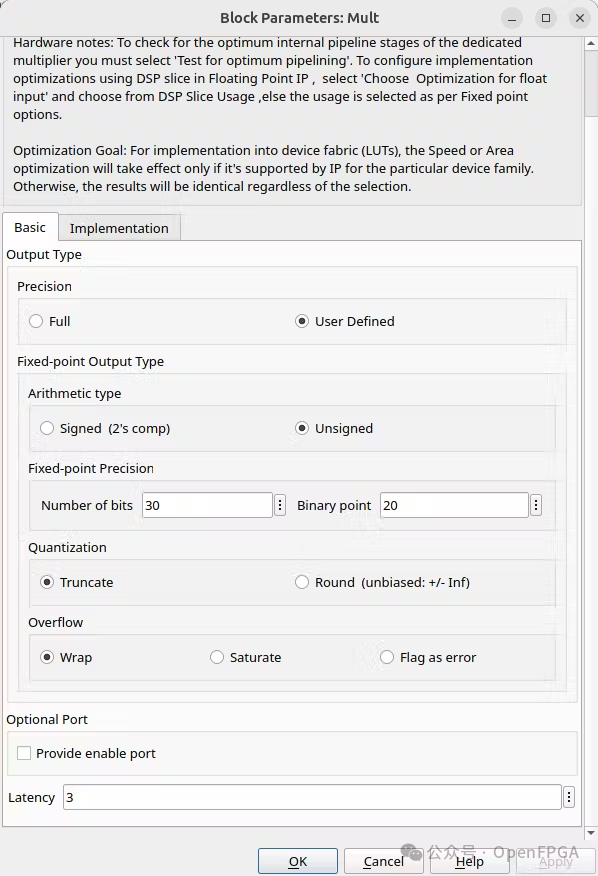

在Gateway In模块的输出端,连接一个乘法模块来计算样本的平方——因为显然 Vitis Model Composer 识别不了内置的平方函数。

由于没有直接的平方运算模块,因此解决方法如下:

将输入馈送到第一个乘法模块的两个端口。这样就可以用传统方法计算了平方值。

为了进行额外的数学运算,取另一个乘法块并将其输出添加到前一个乘法器的结果中。

最后,将第二个输入附加到值为4的Constant 模块,有效地提高振幅水平。

这些模块块参数如下:

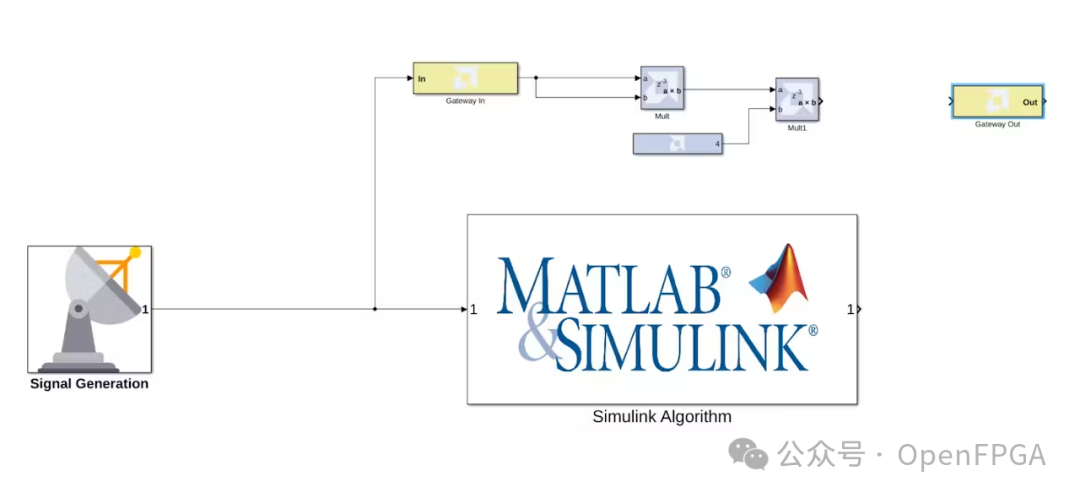

此时,模型应该看起来像下图所示。

对于抽取,虽然 Simulink 的通用库中提供了预建的抽取模块,但它并不包含在 AMD 工具箱中。不过,我们可以使用低通滤波器和下采样器来实现相同的功能,这两个工具都可以在AMD 工具箱中找到。

要实现这一点:

在第二个乘法器的输出端,添加一个数字 FIR 滤波器,以便在下采样之前平滑信号。

然后使用AMD 工具箱中的Downsample 模块来降低采样率。

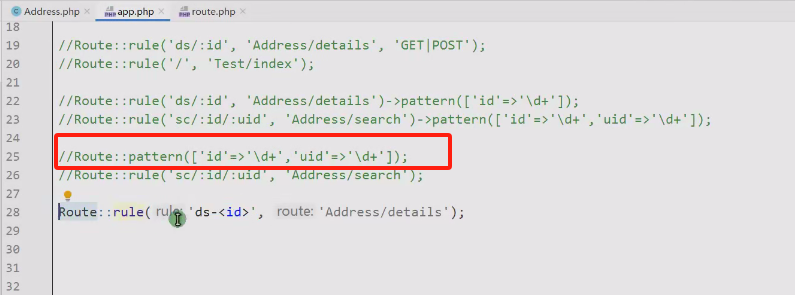

注意:请将FDA 工具放置在设计的根级别(更高级别,而不是子系统内)。可以在以下位置找到它:

Simulink Library Browser → AMD Toolbox → Utilities → Tools → FDAToolFDAToolPulse 检测输出模型编写流程

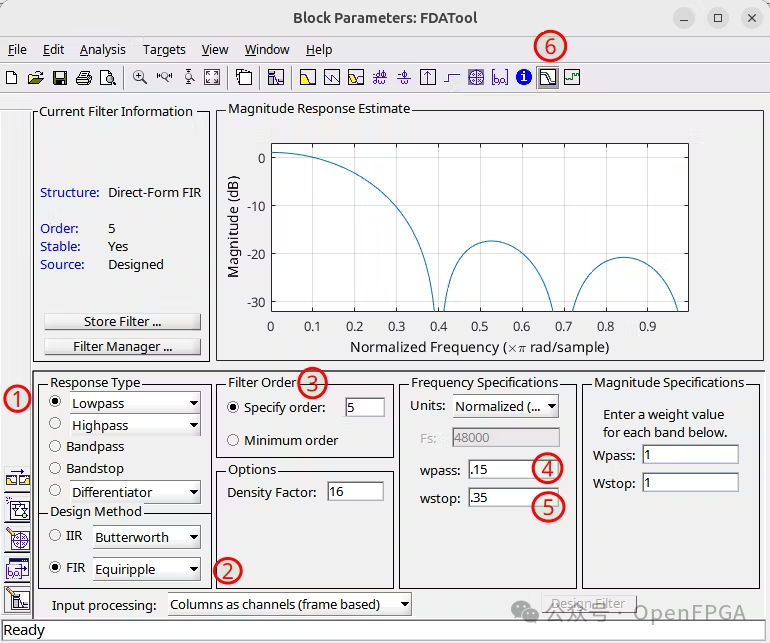

双击 FDA 工具模块以打开其配置窗口。修改下图所示的参数,以确保精确复制结果。这些设置将定义正确信号处理所需的滤波器特性。

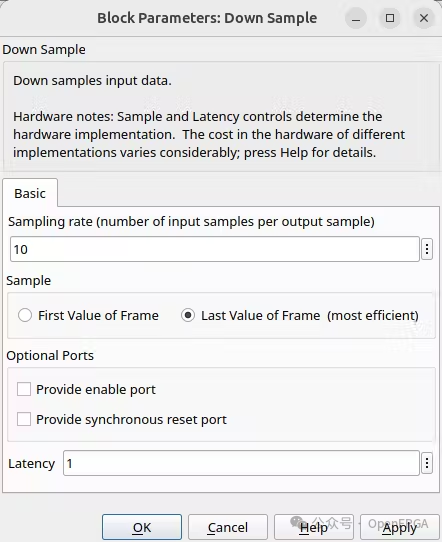

抽取

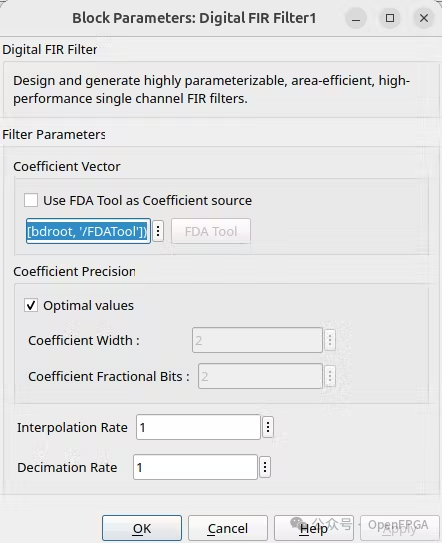

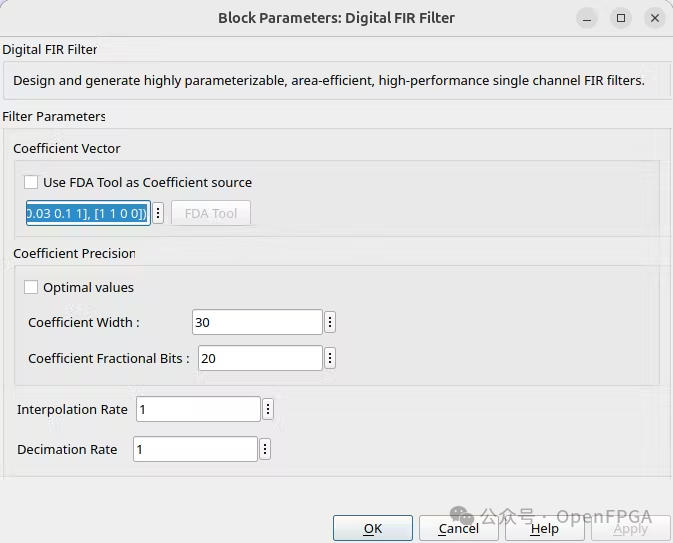

要在模型中使用设计的滤波器,打开我们之前插入的FIR 滤波器的模块参数。在“系数向量”字段下,输入以下行:

xlfda_numerator([bdroot, '/FDATool'])这将FIR滤波器与FDA工具生成的系数关联起来,确保设计的滤波器能够正确应用。该模块的具体配置如下图所示。

应用更改后,请验证滤波器是否按预期运行,然后再继续执行后续步骤。同样,打开Downsample模块的模块参数,并根据下图修改其设置,确保功能正常。这些调整将配置下采样过程,使其符合设计要求。

Filtering

完成抽取步骤后,添加另一个低通滤波器以进一步细化信号。在滤波器模块参数的“系数向量”字段中,输入以下代码:

firpm(20, [0 0.03 0.1 1], [1 1 0 0])此代码使用Parks-McClellan 算法定义滤波器,并指定所需的频率响应。根据下图配置其余参数,确保正确实现。

最终框图

最终的Simulink 框图如下图所示。在滤波器的输出端,使用关系运算符模块将滤波后的信号与恒定阈值2.5进行比较。该模块输出1或0 ,指示信号是否超过阈值,从而有效地做出脉冲检测的决策。

设计完成后,我们就可以进行代码生成了。在进行下一步之前,请确保所有配置都已正确设置。

最终结果(模型编写流程)

此时,如果 Simulink 的常规流程和 Model Composer 的流程输出相似,则表示已成功复制该算法。

代码/IP 生成

再次打开Vitis Model Composer Hub。如果所有步骤都正确执行,系统现在应该列在“Code Generation”选项卡下,并带有绿色复选标记,表示它已准备好进行进一步处理。

此外,在同一选项卡下,将看到四个不同的部分:

Settings设置:包含与时钟配置和目标语言选择相关的常规设置。

Analyze分析:用于时序和资源分析,确保设计满足硬件约束。

Validate on Hardware硬件验证:此选项允许在实际硬件上测试设计,以验证其实际性能。

Export导出:支持导出生成的 IP ,以便将其集成到 Vivado 或其他工具中。

按照下图所示的步骤配置所有这些设置。

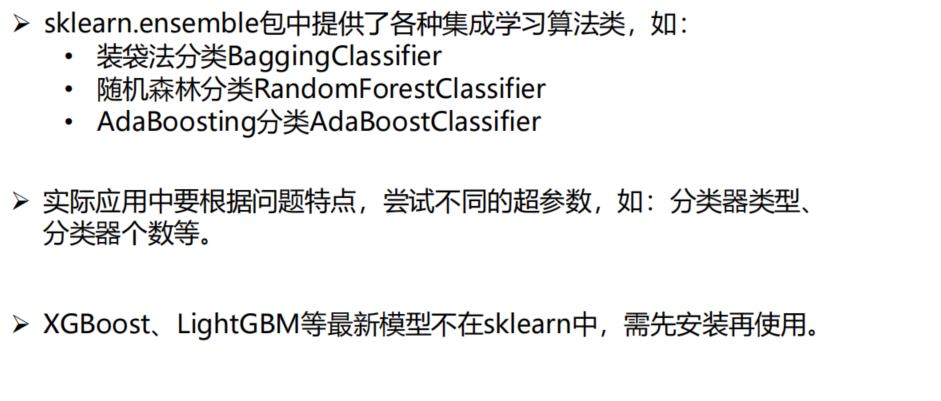

Analyze

Analyze分析部分是一个非常实用的程序,可在综合和实现后执行时序和资源分析。这有助于做出明智的设计决策,优化资源利用率,并微调算法以获得更好的性能。

要执行分析,请按照下图所示的步骤进行这将提供对时间限制、资源消耗和整体系统效率的深入了解,从而允许最终部署之前根据需要改进设计。

单击“Analyze”后,Vitis Model Composer将花一些时间来处理设计并根据选择生成时序和资源分析报告。

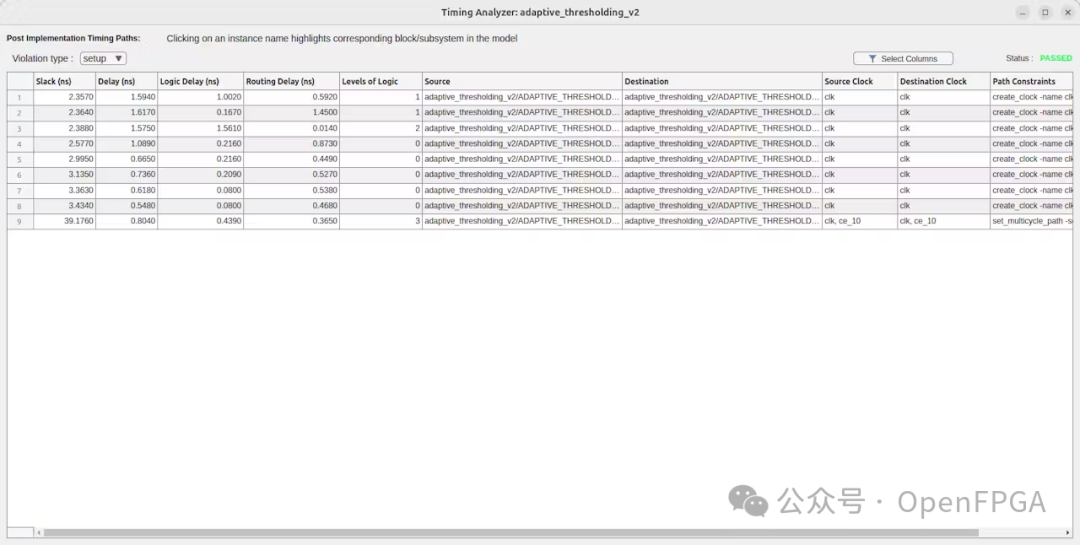

时序分析报告提供有关时钟频率、延迟和建立/保持违规的详细信息,有助于确保设计满足时序约束。

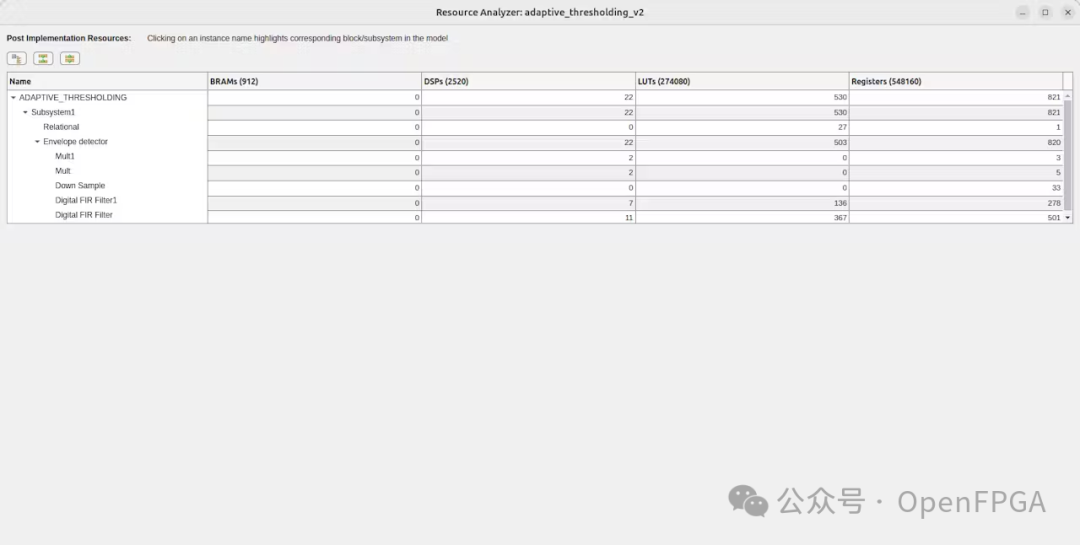

资源分析报告细分了LUT、DSP、BRAM 和 FF 的使用情况,深入了解了硬件利用率和优化机会。

本次设计的时序和资源分析报告分别如下图所示。在继续下一步之前,请查看这些报告,确认设计符合所需的性能和资源限制。

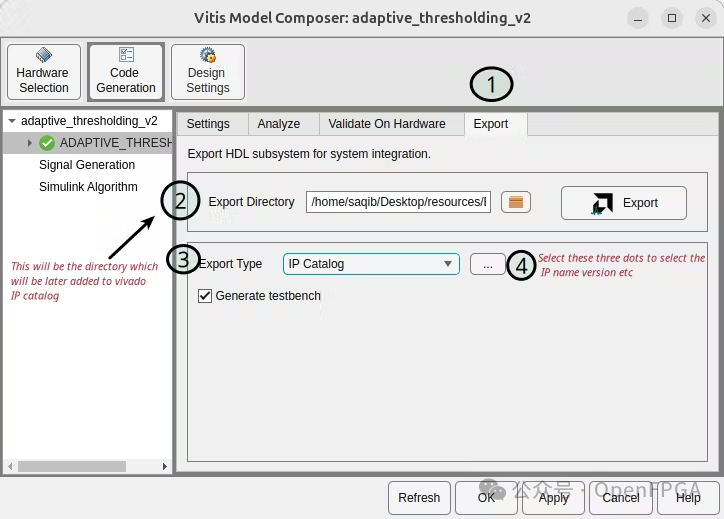

Export

在“Export”部分,将完成并导出Vivado 的 IP 。为了确保顺利集成,请按照下图所示配置设置,然后单击“Export” 。

这将需要一些时间,并且会出现类似于下图所示的消息。

此过程将生成必要的IP 文件,使其可在Vivado 的 IP 目录中使用。导出后,可以轻松地将自定义 IP 集成到Vivado 设计流程中,可以进一步处理和实现。

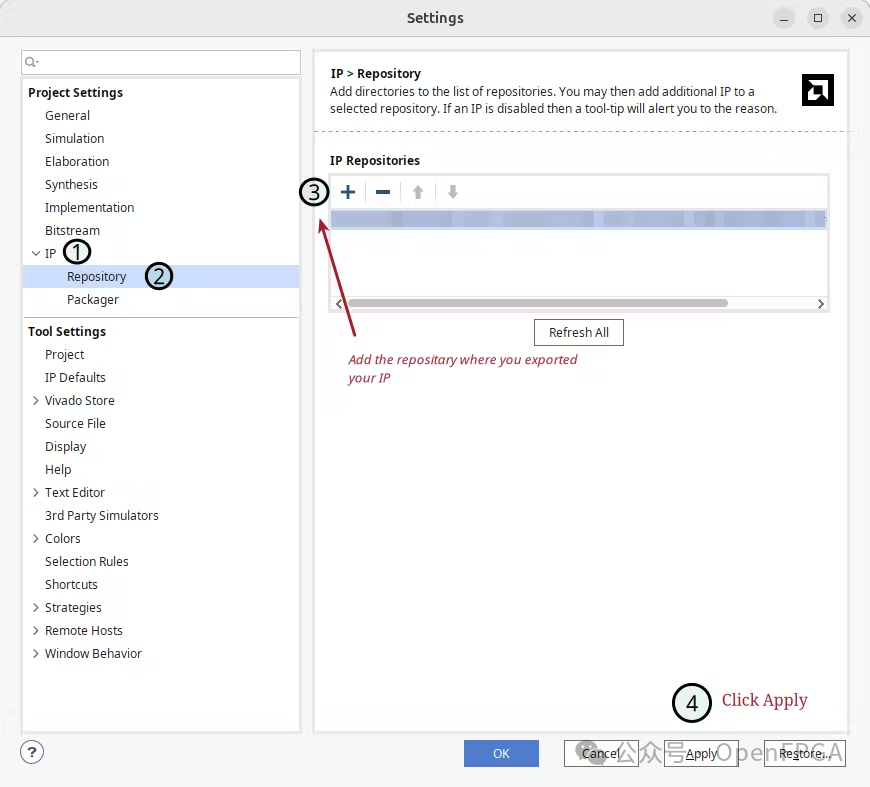

向 Vivado 添加自定义IP

打开Vivado并创建一个新项目。项目设置完成后,导航到顶部栏,点击“工具” ,然后选择“设置” 。

按照下图所示的步骤配置即可。

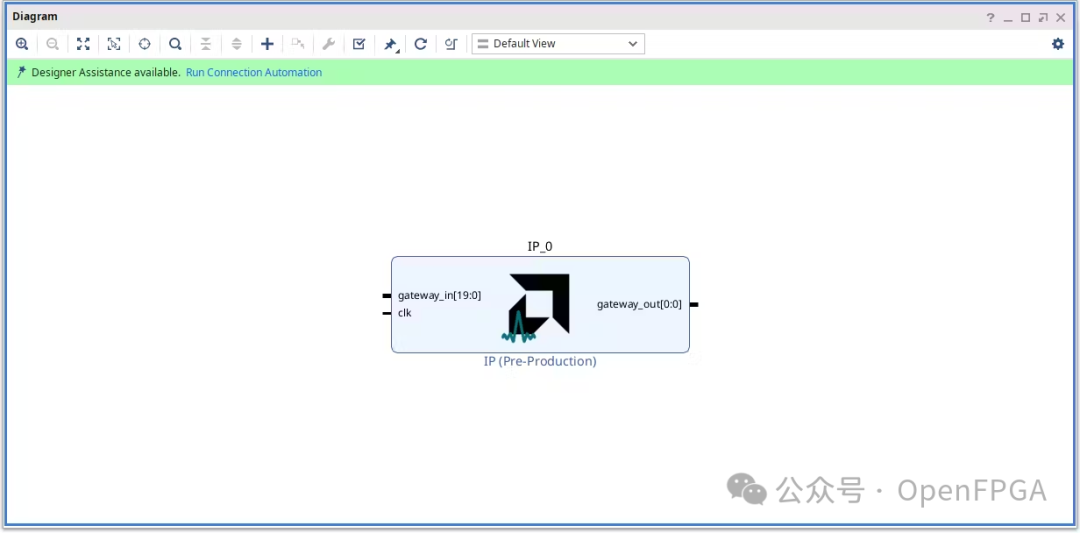

所有步骤成功完成后,自定义 IP 即可集成到Vivado中。此 IP 可在IP 集成器和模块设计中无缝使用。

完整框图如下:

https://github.com/suisuisi/FPGATechnologyGroup/tree/main/VitisModelComposer

总结

成功创建并集成自定义 IP 后,就已完成 FPGA 开发的关键一步。此工作流程不仅简化了IP 设计流程,还提升了未来项目的效率、模块化和可扩展性。通过利用Vitis Model Composer和Vivado ,确保了从算法开发到硬件实现的无缝过渡。

整个开发流程非常简单,将算法的开发时间花在了“算法本身”,而无需太多时间去编写HDL代码、封装IP、验证IP。

虽然Vitis Model Composer并不万能,但是在特定领域的应用也大大简化了FPGA的开发难度,关于Vitis Model Composer大家有什么想法,可以在评论区聊聊。