目录

(1)ALU(Arithmetic Logical Unit)

(2)半加器(Half adder)

(3)全加器(Full Adder)

(5)二进制数的加法电路

(6)二进制数的减法电路

(7)可控反相器及加法、减法电路

(1)ALU(Arithmetic Logical Unit)

算数逻辑单元ALU既能进行二进制的四则运算,也能进行布尔代数的逻辑运算。

ALU符号

(1)二进制数的相加

例1:两个二进制数相加的几个算式:如果有进位就需要多一个进位位来保持,根据它设计电路

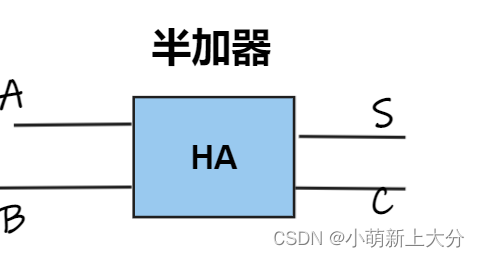

(2)半加器(Half adder)

仅考虑加数和被加数而不考虑低位进位的加法运算即为半加。

能实现半加逻辑功能的电路即为半加器

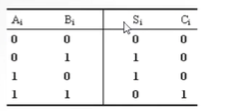

如果Ai,Bi是两个相加的1位二进制数,Si是半加和,Ci是半加进位。根据半加器的功能可以列出如下真值表

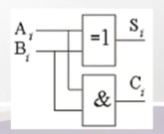

可见Si是由Ai和Bi做异或运算

Ci是由Ai和Bi做与运算

所以半加的电路就为

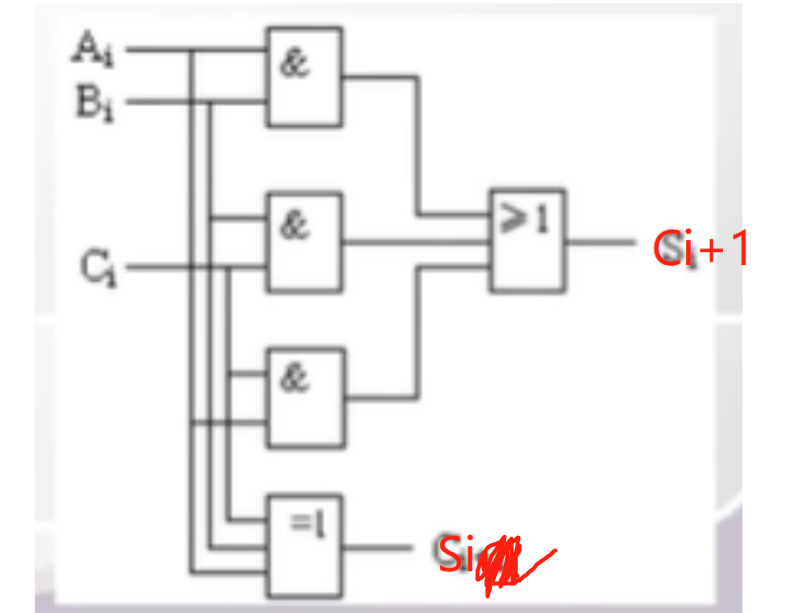

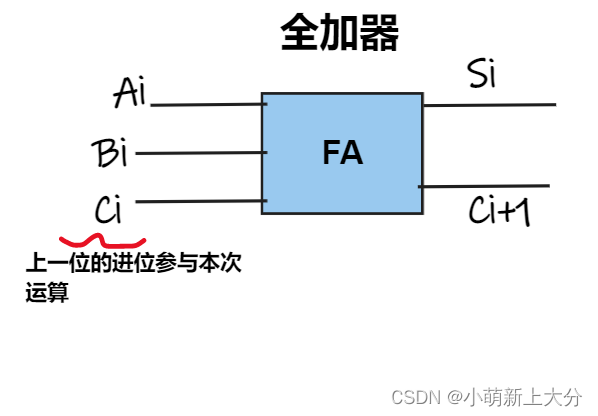

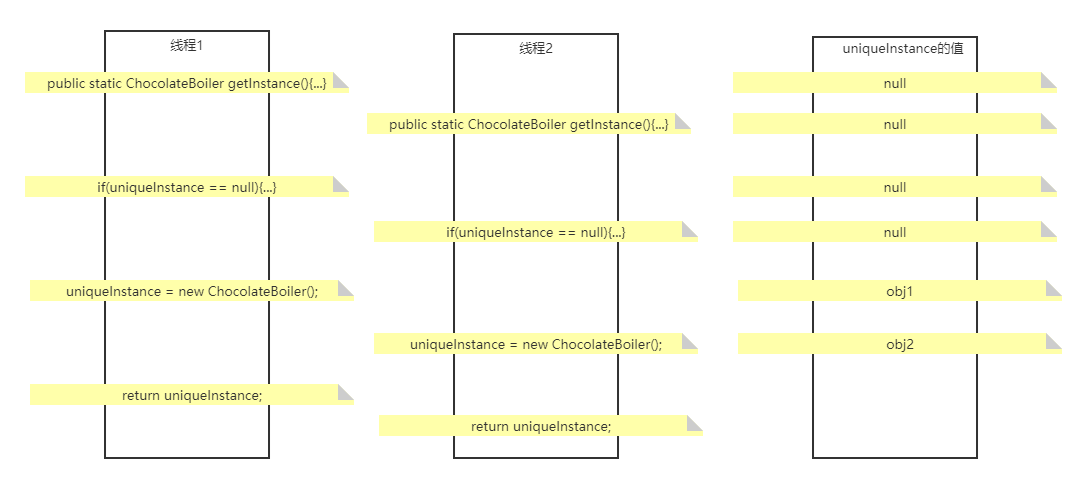

(3)全加器(Full Adder)

不仅考虑加数和被加数,而且考虑低位进位的加法运算即为全加。

能实现全加逻辑功能的电路即为全加器。

加数,被加数数和来自低位的进位三者中

三个输入,两个输出

| Ai | Bi | Ci(上一次运算的进位) | Si | Ci+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

可以看出Si的结果为:Ai异或Bi异或Ci,也就是奇数个1就出1

Ci+1的结果为:Ai&Bi+Ai&Ci+Bi&Ci 也就是1的个数>=2,进位就为1

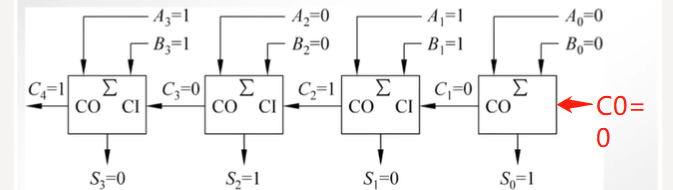

(5)二进制数的加法电路

A=1010

B=1011

这个图,你图里面写FA也可以。

结果就位 10101

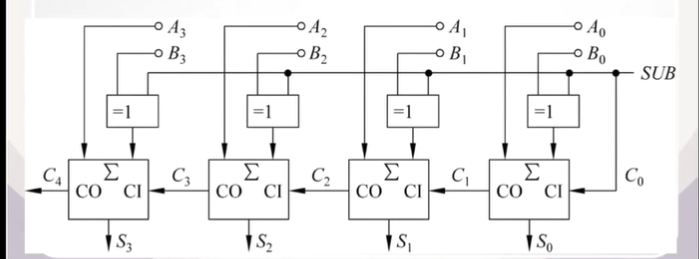

(6)二进制数的减法电路

在微型计算机中,没有专门的减法器,而是将减法运算改变为加法运算。器原理是:将减号以及减数B视为负数,再与被减数A相加,即A-B=A+(-B)这里是补码运算。其和如果有进位的话,则舍去进位)就是两数之差。当符号数采用补码表示时,就可以将减法运算转换为加法运算。

知道Y补 求(-y)补,全部取反+1。 注意和知道原码求补码区分开

由SUB决定是加法还是减法。看不懂这个图先看(7)可控反向器加法,减法电路

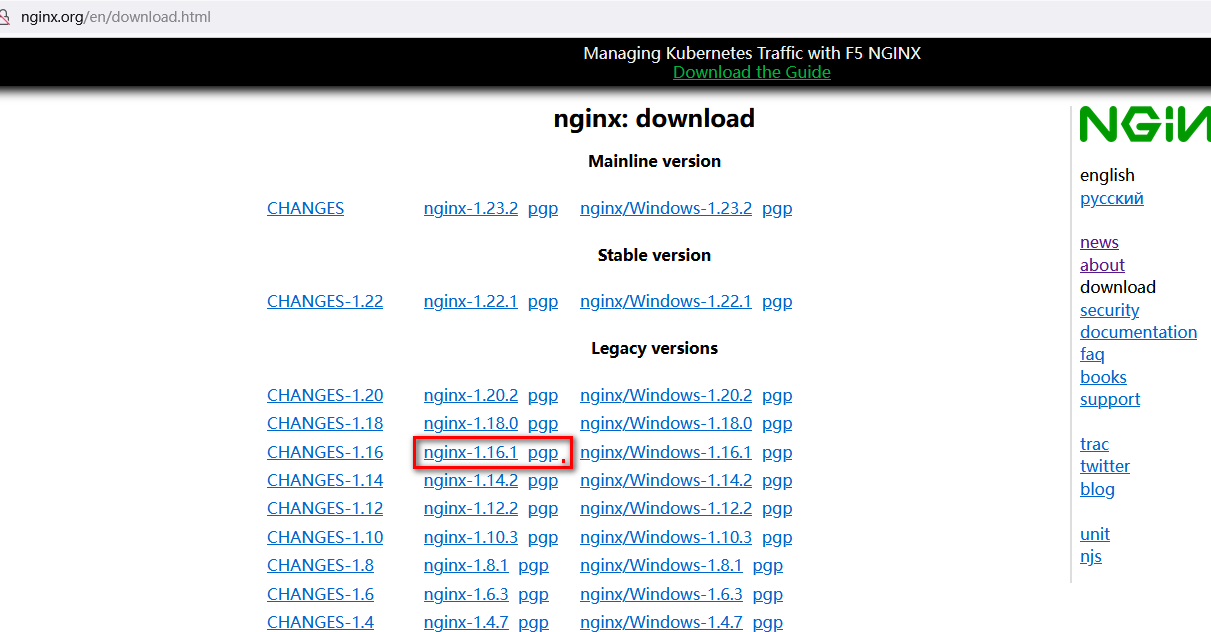

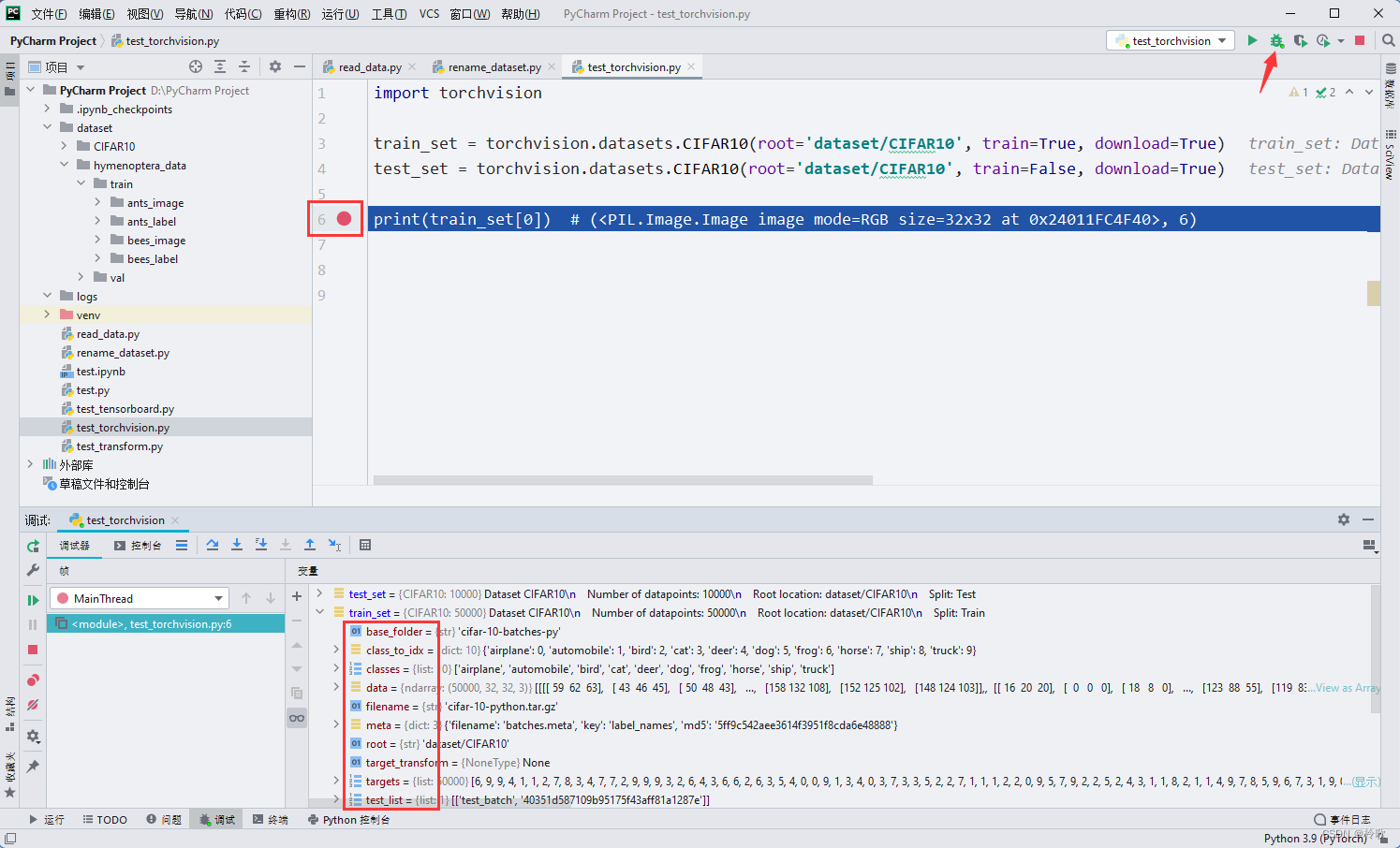

(7)可控反相器及加法、减法电路

利用补码可以将减法运算变为加法运算,因此需要这么一个电路。它能执行取反并使其最低位加1

sub给出0,无效信号 。经过异或门, 你B0是多少,Y还是输出多少。

但是当SUB给出1,经过异或门,刚好完成了取反操作

![[附源码]Python计算机毕业设计高校创新学分申报管理系统](https://img-blog.csdnimg.cn/1a19b496a06943838db3834eda729e6b.png)