目录

组合逻辑

VL11 4位数值比较器电路

VL12 4bit超前进位加法器电路

VL13 优先编码器电路①

VL14 用优先编码器①实现键盘编码电路

VL15 优先编码器Ⅰ

VL16 使用8线-3线优先编码器Ⅰ

VL17 用3-8译码器实现全减器

VL18 实现3-8译码器①

VL19 使用3-8译码器①实现逻辑函数L

VL20 数据选择器实现逻辑电路

工程源码

GitHub - ningbo99128/verilog: 牛客网练习题工程

组合逻辑

VL11 4位数值比较器电路

至于为什么不选择更底层的题解?原因有,刷题是为了走数字ic设计,用这种门级电路搭出来的功能,其实没必要,面试也不会考。在代码上,底层到&、|、!、<<等位操作就可以了,没必要用xnor、or、and、not等描述。下面这个解题思路不错,还可以练习一下“例化”的for循环调用,挺好的。

4位数值比较器电路_牛客题霸_牛客网

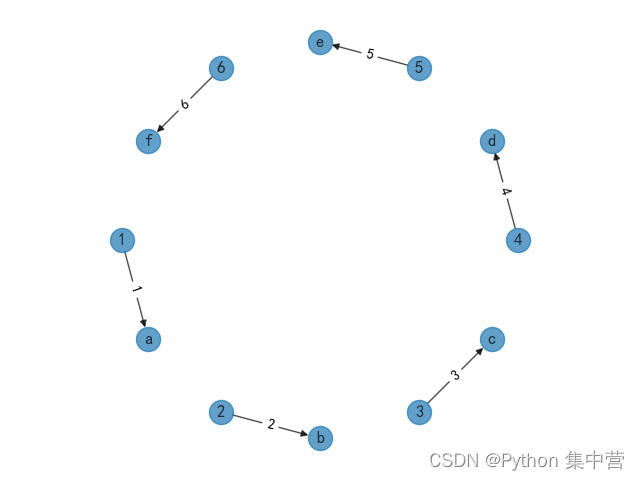

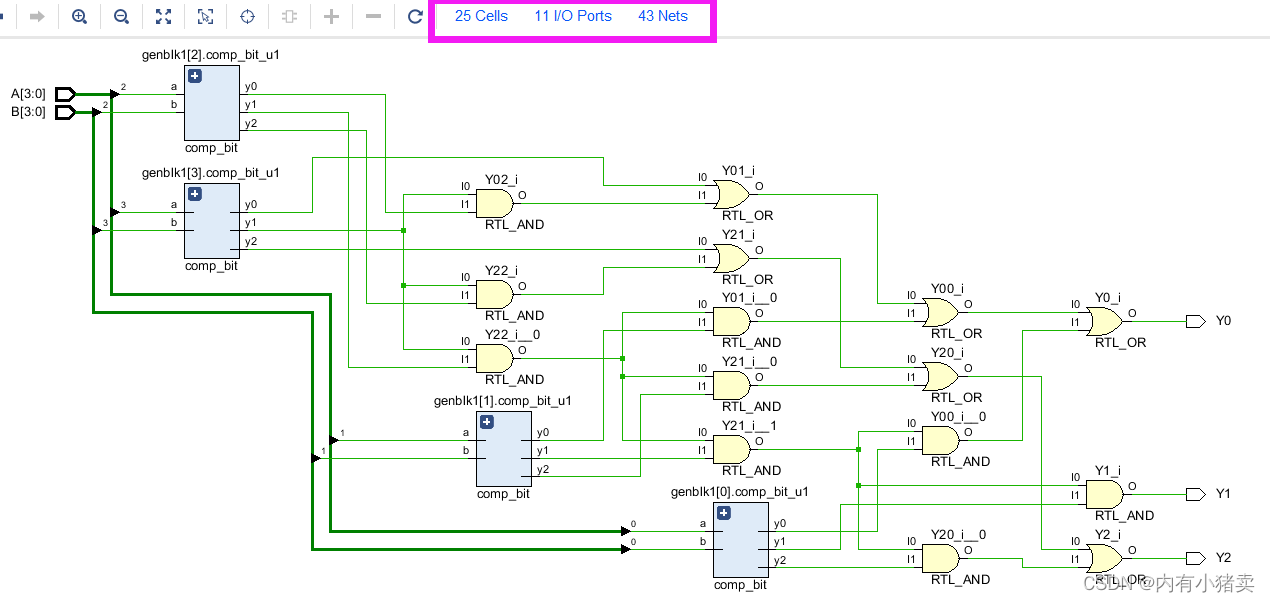

从RTL图中,可以看出代码的逻辑是先计算A[3]、B[3]和A[2]、B[2]和A[1]、B[1]和A[0]、B[0]等2位比较的结果,再通过真值表写出对应的逻辑表达式即可。

//根据题目的真值表

assign Y2 = result_y2[3]|(result_y1[3]&result_y2[2])|

(result_y1[3]& result_y1[2]&result_y2[1])|

(result_y1[3]& result_y1[2]&result_y1[1]&result_y2[0]);

assign Y1 = result_y1[3]&result_y1[2]&result_y1[1]&result_y1[0];

assign Y0 = result_y0[3]|(result_y1[3]&result_y0[2])|

(result_y1[3]& result_y1[2]&result_y0[1])|

(result_y1[3]& result_y1[2]&result_y1[1]&result_y0[0]); for循环例化

VL12 4bit超前进位加法器电路

VL13 优先编码器电路①

VL14 用优先编码器①实现键盘编码电路

VL15 优先编码器Ⅰ

VL16 使用8线-3线优先编码器Ⅰ

VL17 用3-8译码器实现全减器

VL18 实现3-8译码器①

VL19 使用3-8译码器①实现逻辑函数L

请使用3-8译码器①和必要的逻辑门实现函数L=(~A)·C+A·B

![[附源码]Python计算机毕业设计高校创新学分申报管理系统](https://img-blog.csdnimg.cn/1a19b496a06943838db3834eda729e6b.png)