SystemC在CPU/GPU验证中的应用(六)

摘要:下面分享50个逐步升级SystemC编程能力的示例及建议的学习路线图。您可以一次一批地完成它们——从前五个基础的例子开始,然后转向channels, TLM, bus models, simple CPU/GPU kernels等等。在每个阶段掌握之后,再进行下一组的学习。

50个代表性的SystemC例子

- Hello, SystemC! (module + sc_main)

- Simple clock generator

- 4-bit up/down counter

- Blocking FIFO channel

- Non-blocking handshake channel

- Combinational AND/OR modules

- D-flip‐flop with async reset

- 8×1 multiplexer

- Simple RAM model (blocking accesses)

- Simple ROM model

- Dual-port RAM

- Bus arbiter (round-robin)

- TLM2.0 blocking transport (initiator)

- TLM2.0 blocking transport (target)

- TLM2.0 non-blocking transport

- TLM2.0 analysis port / export

- Simple AXI-Lite bus model

- AXI-Lite master + slave example

- Quantum keeper & time annotation

- tlm_utils::simple_initiator_socket

- tlm_utils::simple_target_socket

- Hierarchical module instantiation

- Dynamic process spawn & kill

- Event notification & sc_event_queue

- Reset synchronization circuit

- Clock domain crossing FIFO

- Bus monitor / tracer (TLM analysis)

- Memory-mapped register file

- Interrupt controller model

- Pipeline stage model (fetch/decode/execute)

- Simple 4-stage CPU datapath

- Cache model (direct-mapped)

- DMA engine model

- GPGPU kernel launcher skeleton

- GPU shader core (vector add)

- Barrier synchronization (sc_barrier emulation)

- Producer-consumer with sc_mutex

- sc_semaphore example

- SystemC-AMS basic RC filter

- Fixed-point arithmetic with sc_fixed

- Power‐aware sc_trace (VCD generation)

- Cross-trade-off analysis (timing vs. power)

- SystemC assertions (SC_ASSERT)

- UVM-SystemC basic use case

- Co-simulation stub (Verilog DPI)

- SystemC Python binding stub

- Parameterized module (SC_MODULE_T)

- TLM-2.0 generic payload extensions

- Simple NoC router model

- Full mini‐SOC: CPU + L2 cache + memory + interconnect

Sixth Batch: Examples 41–50

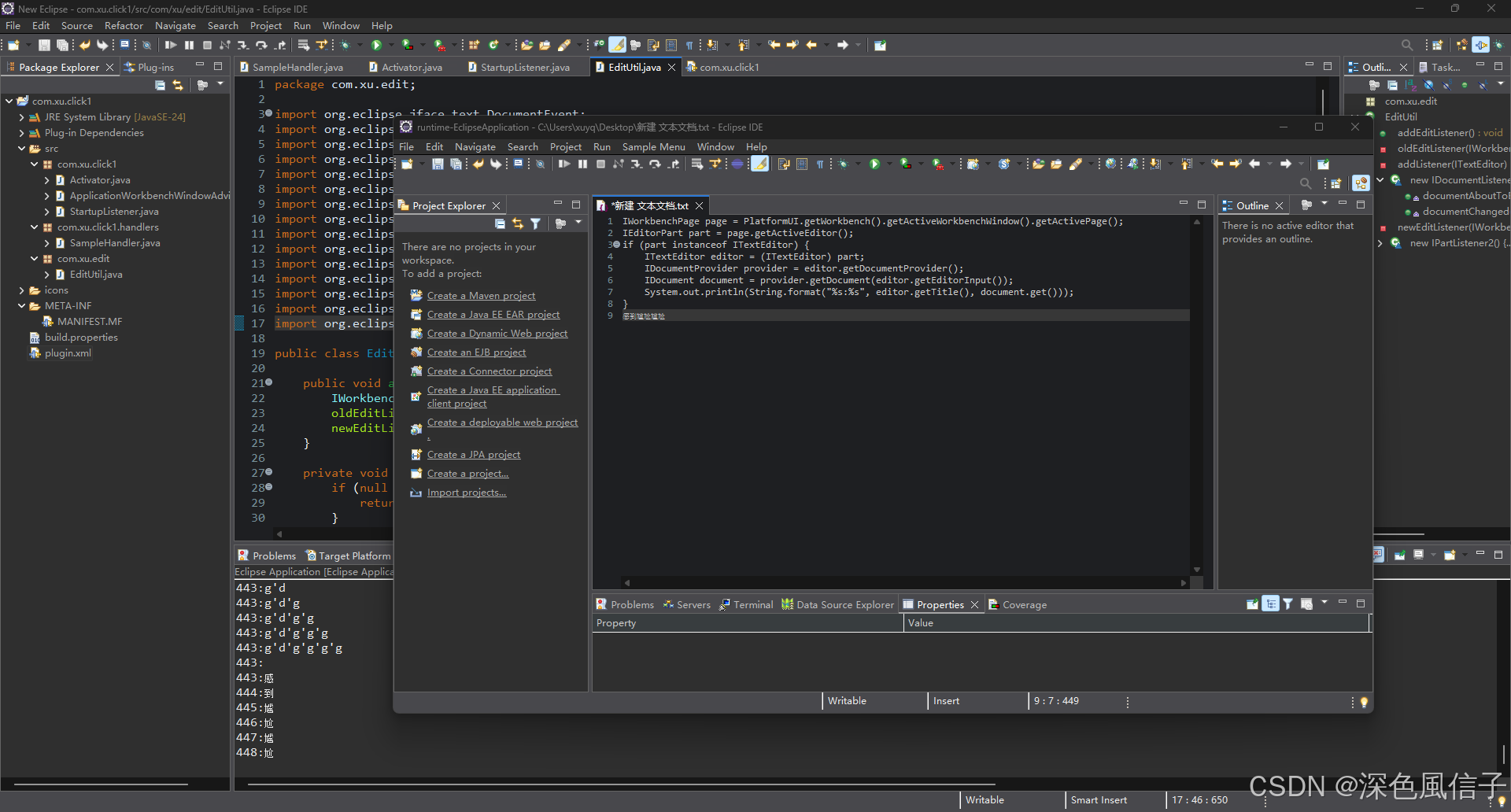

Below are the first five examples with complete code + detailed comments.

41. Power‐aware sc_trace (VCD 生成)

文件名:trace_example.cpp

#include <systemc.h>

// 简单的 4-bit 计数器模块,每个时钟周期递增

SC_MODULE(Counter) {

sc_in<bool> clk;

sc_out<sc_uint<4>> count;

SC_CTOR(Counter) {

SC_METHOD(proc);

sensitive << clk.pos();

count.initialize(0);

}

void proc() {

count.write( count.read() + 1 );

}

};

int sc_main(int, char*[]) {

sc_clock clk("clk", 10, SC_NS);

sc_signal<sc_uint<4>> cnt_sig;

Counter cnt("cnt");

cnt.clk(clk);

cnt.count(cnt_sig);

// 打开 VCD 波形文件

sc_trace_file* tf = sc_create_vcd_trace_file("wave");

// 跟踪时钟和计数值

sc_trace(tf, clk, "clk");

sc_trace(tf, cnt_sig,"count");

// run 200ns

sc_start(200, SC_NS);

sc_close_vcd_trace_file(tf);

return 0;

}

运行后会生成 wave.vcd,可以在 GTKWave 等工具中查看。

42. Cross‐trade‐off Analysis (Timing vs. Power 简易模型)

文件名:power_analysis.cpp

#include <systemc.h>

// 统计翻转次数并估算功耗的模块

SC_MODULE(Gate) {

sc_in<bool> in;

sc_out<bool> out;

unsigned long toggle_count;

SC_CTOR(Gate): toggle_count(0) {

SC_METHOD(proc);

sensitive << in;

dont_initialize();

}

void proc() {

bool new_v = !in.read(); // 反相

if (out.read() != new_v) {

toggle_count++;

out.write(new_v);

}

}

};

// 顶层 Testbench:记录仿真时间、开关次数并估算能耗

int sc_main(int, char*[]) {

sc_clock clk("clk", 10, SC_NS);

sc_signal<bool> sig_in, sig_out;

Gate gate("gate");

gate.in(sig_in);

gate.out(sig_out);

// 产生输入信号——一个 4 周期高电平,4 周期低电平循环

SC_THREAD([&]() {

while (true) {

for (int i = 0; i < 4; ++i) { sig_in.write(true); wait(clk.posedge_event()); }

for (int i = 0; i < 4; ++i) { sig_in.write(false); wait(clk.posedge_event()); }

}

});

// 在仿真结束时打印结果

sc_start(200, SC_NS);

unsigned long toggles = gate.toggle_count;

double sim_time_ns = sc_time_stamp().to_seconds() * 1e9;

d

![题海拾贝:P8598 [蓝桥杯 2013 省 AB] 错误票据](https://i-blog.csdnimg.cn/direct/6848721f37aa40ca84322a78517857ab.png)