第1-2周:基础项目 - 4位加法器和计数器

目标:掌握Verilog基本语法和模块设计。

-

第1周:

- 学习Verilog的基本语法和结构(模块、端口、数据类型)。

- 设计并实现一个4位加法器。

- 编写测试平台(Testbench)对4位加法器进行功能仿真。

-

第2周:

- 学习组合逻辑设计的最佳实践。

- 设计并实现一个4位同步计数器。

- 编写测试平台,对计数器进行仿真和验证。

第3-4周:进阶项目 - 多路选择器和译码器

目标:深入理解组合逻辑电路和Verilog语法。

-

第3周:

- 学习多路选择器的工作原理。

- 设计并实现一个4:1多路选择器。

- 编写测试平台,对多路选择器进行仿真和验证。

-

第4周:

- 学习译码器的工作原理。

- 设计并实现一个3:8译码器。

- 编写测试平台,对译码器进行仿真和验证。

第5-6周:时序逻辑设计 - 寄存器和FIFO

目标:掌握时序逻辑电路设计方法。

-

第5周:

- 学习寄存器的基本概念和设计方法。

- 设计并实现一个8位移位寄存器。

- 编写测试平台,对移位寄存器进行仿真和验证。

-

第6周:

- 学习FIFO(先进先出队列)的工作原理。

- 设计并实现一个简单的FIFO。

- 编写测试平台,对FIFO进行仿真和验证。

第7-8周:状态机设计 - 简单UART模块

目标:理解和设计有限状态机(FSM)。

-

第7周:

- 学习有限状态机的概念和设计方法。

- 设计并实现一个简单的UART发送器。

- 编写测试平台,对UART发送器进行仿真和验证。

-

第8周:

- 设计并实现一个简单的UART接收器。

- 编写测试平台,对UART接收器进行仿真和验证。

第9-10周:项目整合 - UART通信系统

目标:将多个模块整合成一个完整的系统。

-

第9周:

- 将UART发送器和接收器整合成一个完整的通信系统。

- 设计并实现UART通信系统的顶层模块。

- 编写测试平台,对整个系统进行仿真和验证。

-

第10周:

- 在FPGA开发板上实现UART通信系统。

- 测试系统在实际硬件上的性能和功能。

- 进行调试和优化。

第11-12周:高级项目 - 简单CPU设计

目标:综合应用所学知识设计一个简单的CPU。

- 第11周:

- 学习CPU的基本工作原理和结构。

- 设计并实现一个简单的CPU数据路径。

- 编写测试平台,对数据路径进行仿真和验证。

- 第12周:

- 设计并实现CPU的控制单元。

- 整合数据路径和控制单元,完成CPU设计。

- 编写测试平台,对整个CPU进行仿真和验证。

- 在FPGA开发板上实现并测试CPU。

资源推荐

-

书籍:

- 《Verilog HDL》 by Samir Palnitkar

- 《FPGA Prototyping by Verilog Examples》 by Pong P. Chu

-

在线课程:

- Coursera上的“FPGA Design for Embedded Systems”

- edX上的“Digital Design using Verilog”

-

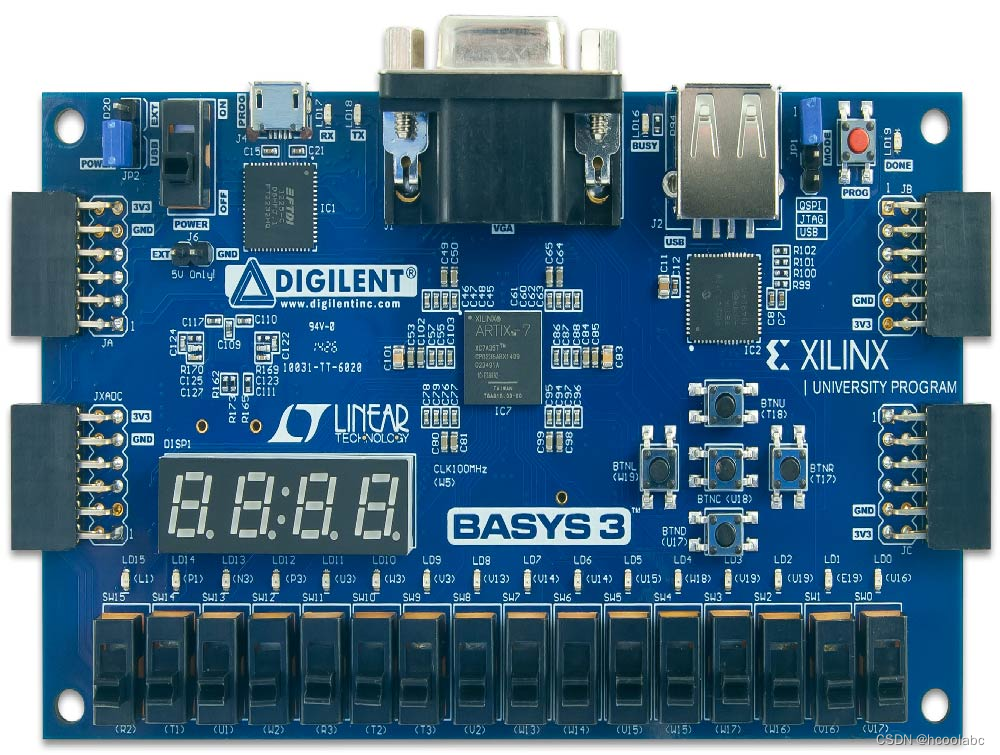

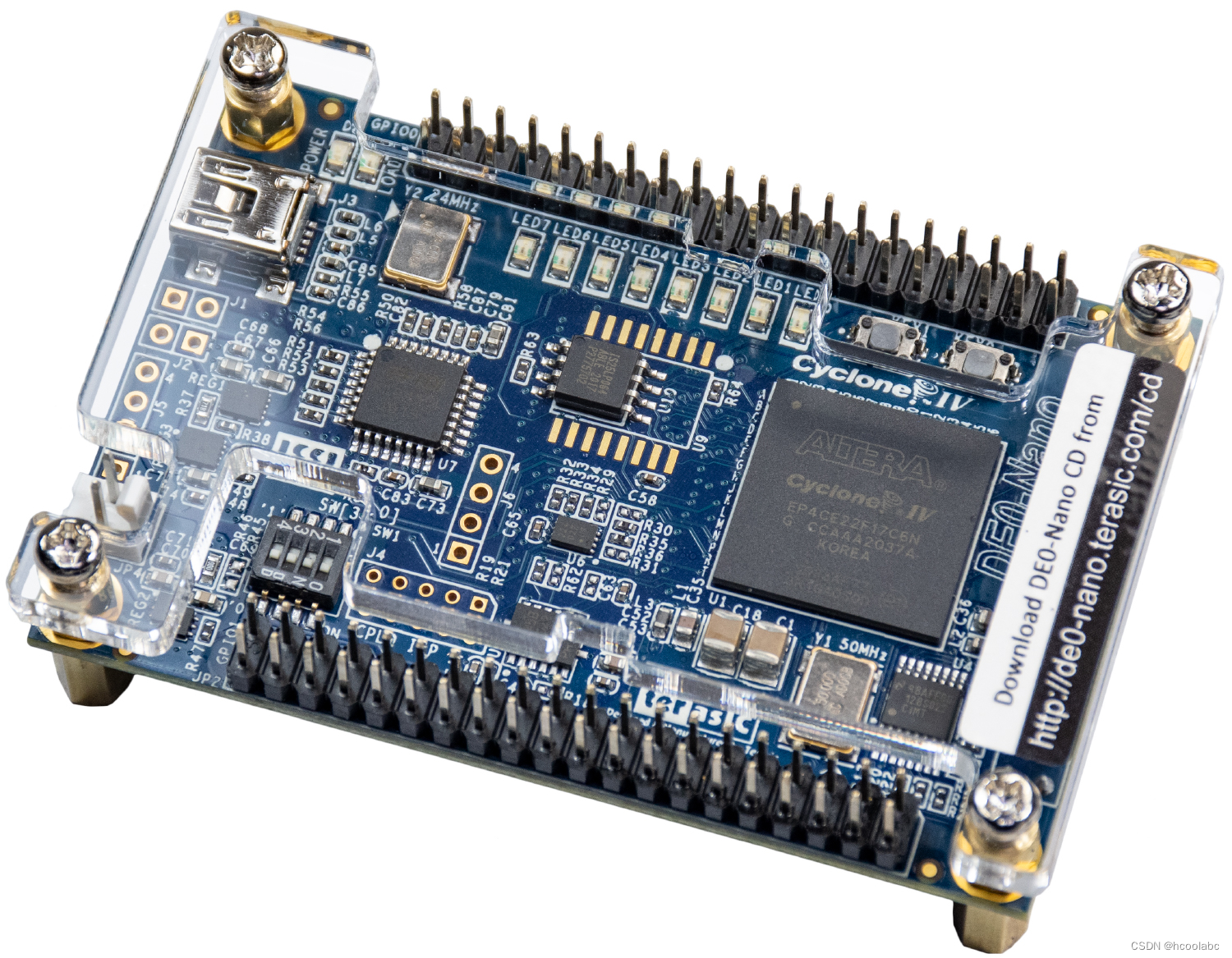

开发板:

-

Xilinx的开发板

-

Intel的开发板

-

-

通过严格按照周计划进行学习和实践,可以有效地掌握FPGA设计的基本技能和方法,为更复杂的项目打下坚实的基础。