REVIEW

| 关于TFT显示屏,之前已经做过彩条显示: TFT显示屏驱动_tft驱动-CSDN博客 |

| 关于ROM IP核,以及coe文件生成: FPGA寄存器 Vivado IP核_fpga寄存器资源-CSDN博客 |

1. TFT屏幕+ROM显示正弦波

①生成coe文件 |

| %% sin-cos wave data write in coe file width = 12;%与幅值有关 |

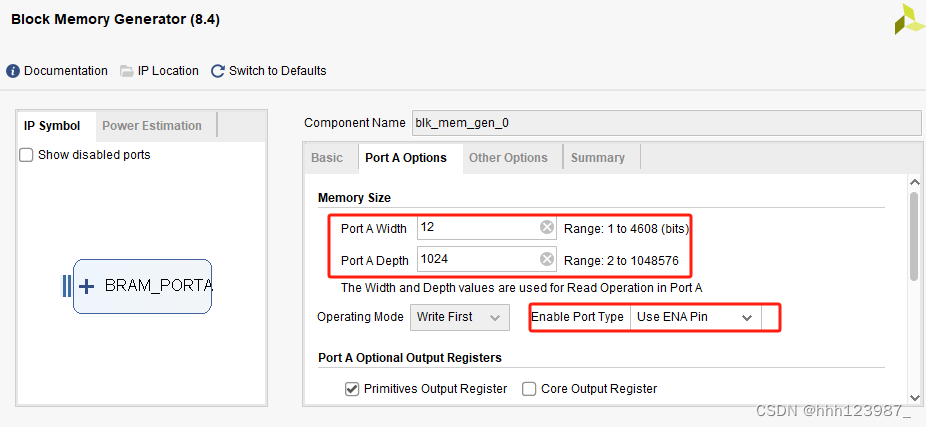

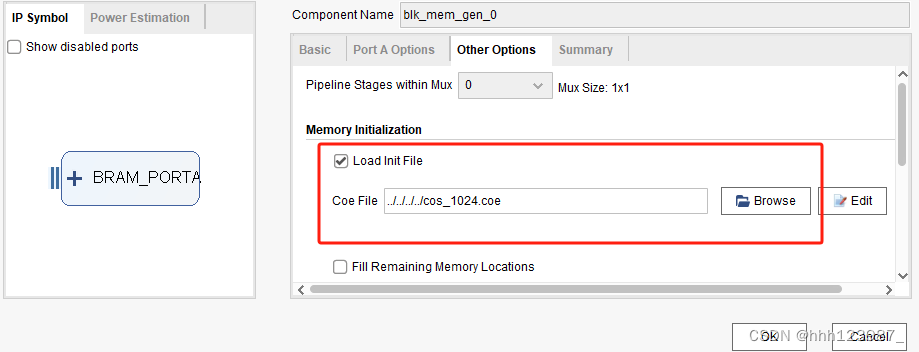

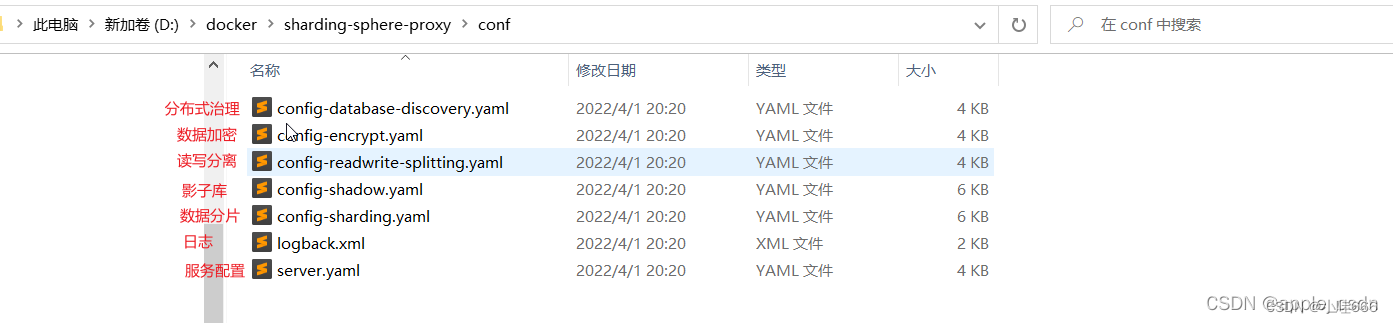

②配置ROM |

|

|

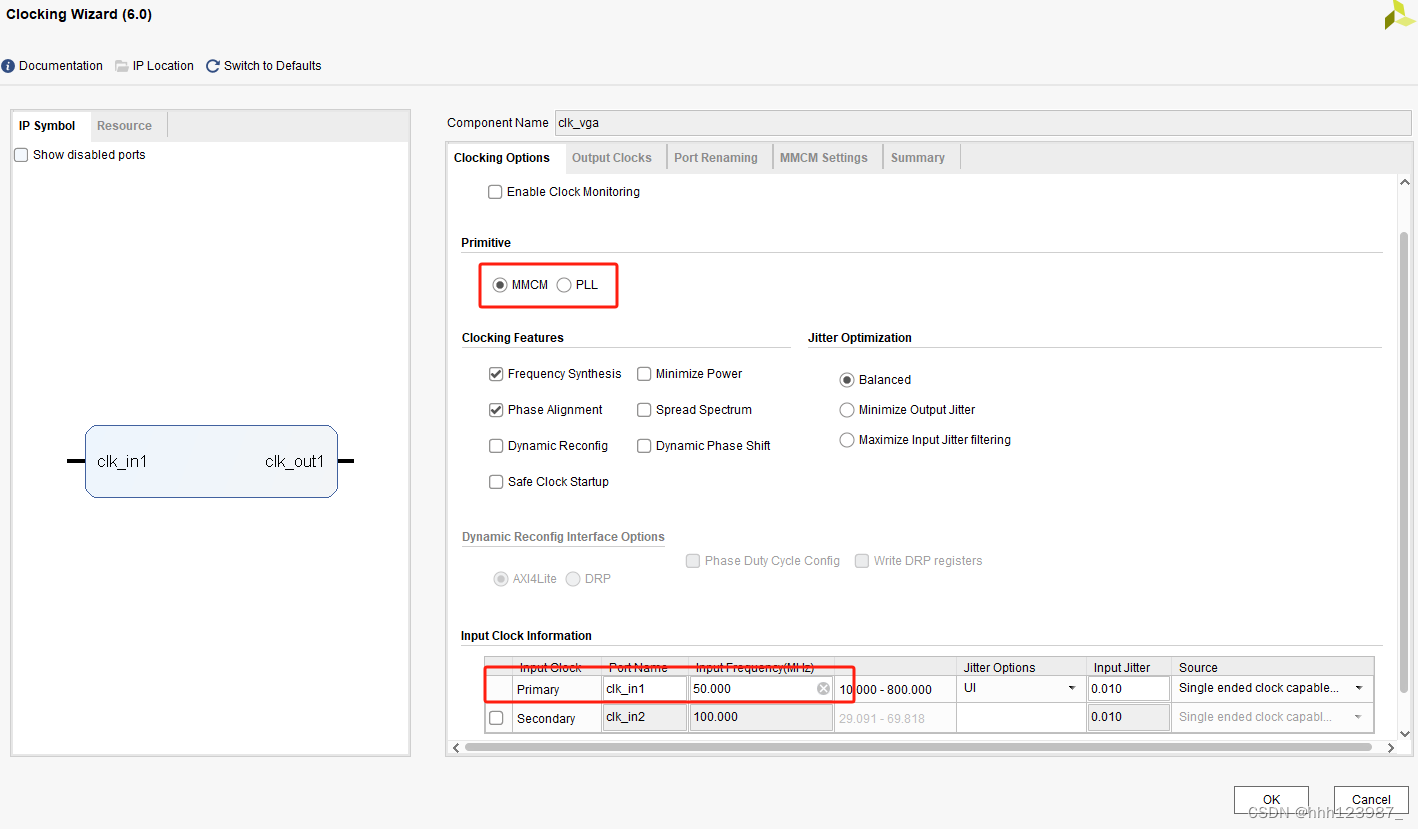

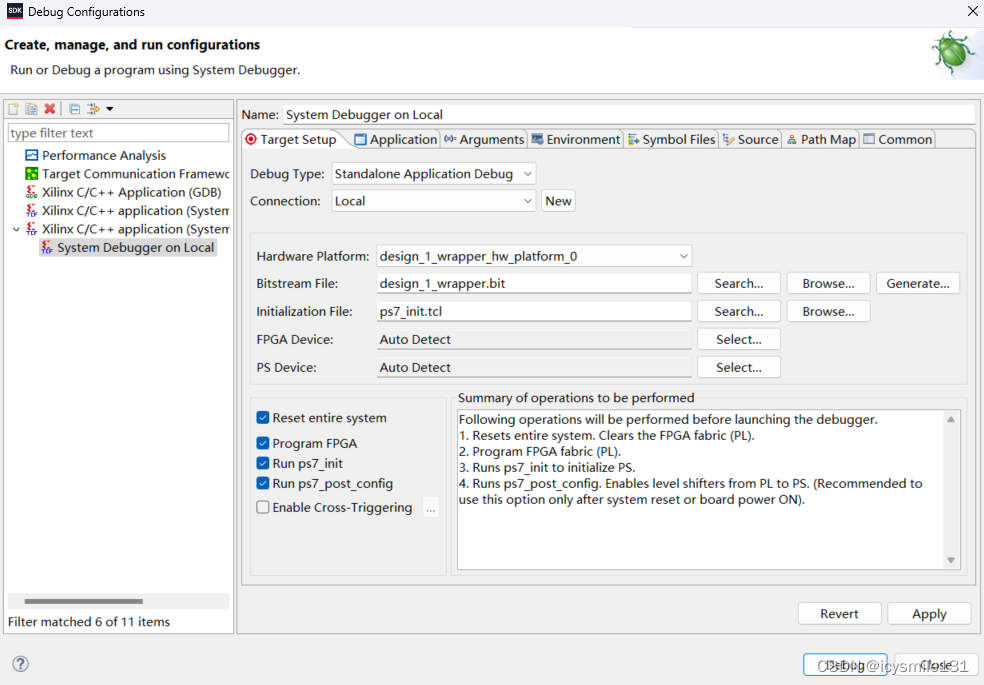

③VGA时钟配置 |

|

|

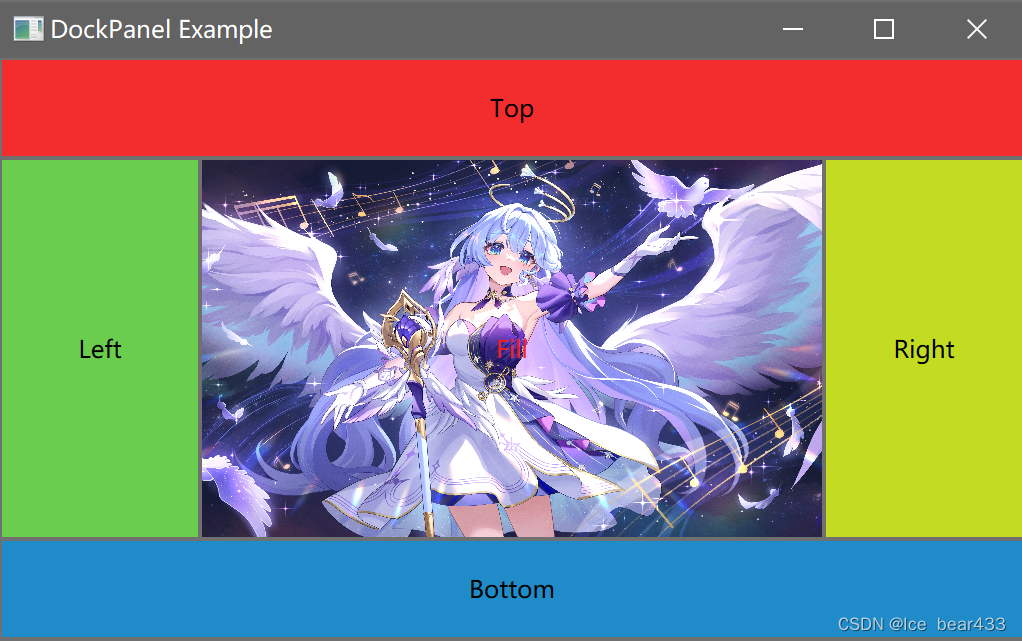

④VGA_CTRL |

| module VGA_CTRL( // data_req |

⑤vga_parameter.v |

| /* 使用时根据实际工作需求选择几个预定义参数就可以 MODE_RGB888 和 MODE_RGB565 两个参数二选一,用来决定驱动工作在 16 位模式还是 24 位模式 针对小梅哥提供的一系列显示设备,各个设备参数如下所述 4.3 寸屏:16 位色 RGB565 模式 5 寸屏:16 位色 RGB565 模式 GM7123 模块使用 24 位色 RGB888 模式, Resolution_xxxx 预定义用来决定显示设备分辨率,常见设备分辨率如下所述 4.3 寸 TFT 显示屏:Resolution_480x272 5 寸 TFT 显示屏:Resolution_800x480 VGA 常见分辨率: Resolution_640x480 Resolution_800x600 Resolution_1024x768 Resolution_1280x720 Resolution_1920x1080 */ //以下两行预定义根据实际使用的模式,选择一个使能,另外一个使用注释的方式屏蔽 `define MODE_RGB888 //`define MODE_RGB565 //以下 7 行预定义根据实际使用的分辨率,选择一个使能,另外 6 个使用注释的方式屏蔽 //`define Resolution_480x272 1 //时钟为 9MHz //`define Resolution_640x480 1 //时钟为 25.175MHz `define Resolution_800x480 1 //时钟为 33MHz //`define Resolution_800x600 1 //时钟为 40MHz TFT_5屏幕分辨率 //`define Resolution_1024x768 1 //时钟为 65MHz //`define Resolution_1280x720 1 //时钟为 74.25MHz //`define Resolution_1920x1080 1 //时钟为 148.5MHz //定义不同的颜色深度 `ifdef MODE_RGB888 `define Red_Bits 8 `define Green_Bits 8 `define Blue_Bits 8 `elsif MODE_RGB565 `define Red_Bits 5 `define Green_Bits 6 `define Blue_Bits 5 `endif //定义不同分辨率的时序参数 `ifdef Resolution_480x272 `define H_Total_Time 12'd525 `define H_Right_Border 12'd0 `define H_Front_Porch 12'd2 `define H_Sync_Time 12'd41 `define H_Back_Porch 12'd2 `define H_Left_Border 12'd0 `define V_Total_Time 12'd286 `define V_Bottom_Border 12'd0 `define V_Front_Porch 12'd2 `define V_Sync_Time 12'd10 `define V_Back_Porch 12'd2 `define V_Top_Border 12'd0 `elsif Resolution_640x480 `define H_Total_Time 12'd800 `define H_Right_Border 12'd8 `define H_Front_Porch 12'd8 `define H_Sync_Time 12'd96 `define H_Back_Porch 12'd40 `define H_Left_Border 12'd8 `define V_Total_Time 12'd525 `define V_Bottom_Border 12'd8 `define V_Front_Porch 12'd2 `define V_Sync_Time 12'd2 `define V_Back_Porch 12'd25 `define V_Top_Border 12'd8 `elsif Resolution_800x480 `define H_Total_Time 12'd1056 `define H_Right_Border 12'd0 `define H_Front_Porch 12'd40 `define H_Sync_Time 12'd128 `define H_Back_Porch 12'd88 `define H_Left_Border 12'd0 `define V_Total_Time 12'd525 `define V_Bottom_Border 12'd8 `define V_Front_Porch 12'd2 `define V_Sync_Time 12'd2 `define V_Back_Porch 12'd25 `define V_Top_Border 12'd8 `elsif Resolution_800x600 `define H_Total_Time 12'd1056 `define H_Right_Border 12'd0 `define H_Front_Porch 12'd40 `define H_Sync_Time 12'd128 `define H_Back_Porch 12'd88 `define H_Left_Border 12'd0 `define V_Total_Time 12'd628 `define V_Bottom_Border 12'd0 `define V_Front_Porch 12'd1 `define V_Sync_Time 12'd4 `define V_Back_Porch 12'd23 `define V_Top_Border 12'd0 `elsif Resolution_1024x768 `define H_Total_Time 12'd1344 `define H_Right_Border 12'd0 `define H_Front_Porch 12'd24 `define H_Sync_Time 12'd136 `define H_Back_Porch 12'd160 `define H_Left_Border 12'd0 `define V_Total_Time 12'd806 `define V_Bottom_Border 12'd0 `define V_Front_Porch 12'd3 `define V_Sync_Time 12'd6 `define V_Back_Porch 12'd29 `define V_Top_Border 12'd0 `elsif Resolution_1280x720 `define H_Total_Time 12'd1650 `define H_Right_Border 12'd0 `define H_Front_Porch 12'd110 `define H_Sync_Time 12'd40 `define H_Back_Porch 12'd220 `define H_Left_Border 12'd0 `define V_Total_Time 12'd750 `define V_Bottom_Border 12'd0 `define V_Front_Porch 12'd5 `define V_Sync_Time 12'd5 `define V_Back_Porch 12'd20 `define V_Top_Border 12'd0 `elsif Resolution_1920x1080 `define H_Total_Time 12'd2200 `define H_Right_Border 12'd0 `define H_Front_Porch 12'd88 `define H_Sync_Time 12'd44 `define H_Back_Porch 12'd148 `define H_Left_Border 12'd0 `define V_Total_Time 12'd1125 `define V_Bottom_Border 12'd0 `define V_Front_Porch 12'd4 `define V_Sync_Time 12'd5 `define V_Back_Porch 12'd36 `define V_Top_Border 12'd0 `endif |

⑥VGA_CTRL.xdc |

| set_property IOSTANDARD LVCMOS33 [get_ports {VGA_RGB[15]}] |

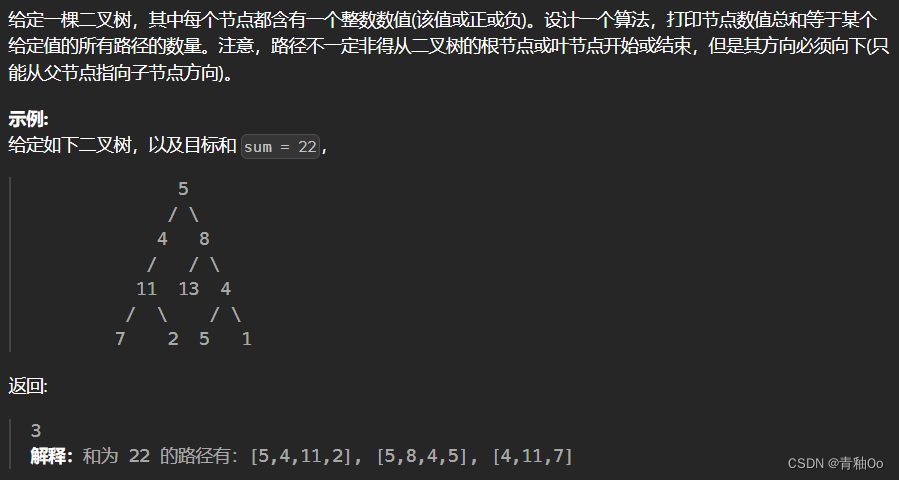

⑦VGA_cos |

| module VGA_cos(

wire R_all = vcount >= 0 && vcount < 480; |

|

|

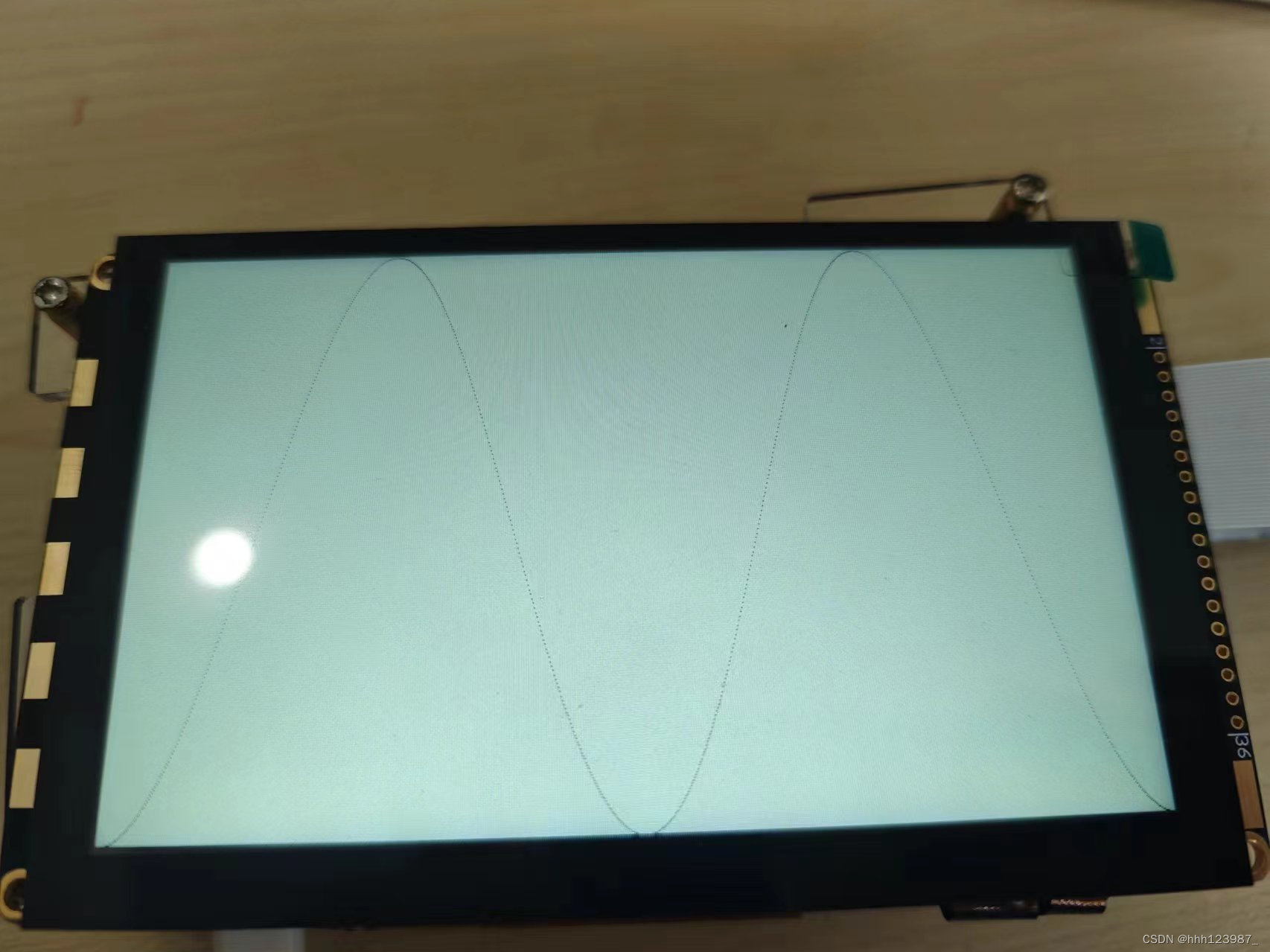

| 摸鱼怪碎碎念: ROM依次存储,地址增加对应时间增加 hcount 为列 vcount 为行 按照 hcount 增加,ROM中的值定位vcount |

2. 画饼

| 需要可读可写,就是用RAM啦~ 下次再慢慢摸鱼吧~ |