本博客参考自文章链接

本文以全加器为例,演示DC综合的流程。设计文件如下:

module full_adder(

input clk,

input rstn,

input [31:0] a_in,

input [31:0] b_in,

input c_in,

output reg [31:0] sum_out,

output reg c_out

);

wire c_out_w;

wire [31:0] sum_out_w;

assign {c_out_w,sum_out_w}=a_in+b_in+c_in;

always@(posedge clk)

if(~rstn)

c_out<=0;

else

c_out<=c_out_w;

//

always@(posedge clk)

if(~rstn)

sum_out<=0;

else

sum_out<=sum_out_w;

endmodule

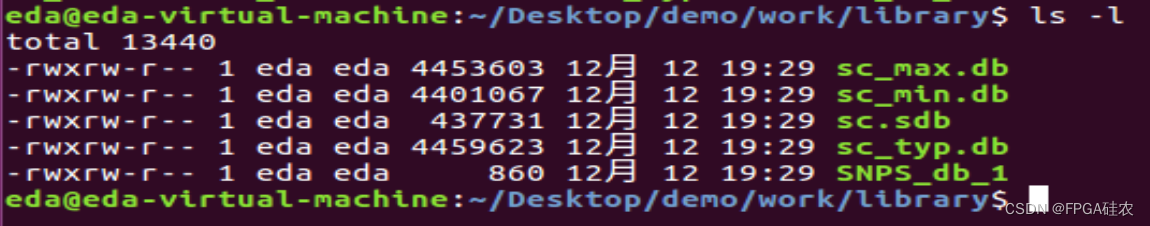

创建library文件夹

创建library文件夹,将工艺库文件放入此文件夹,如下图所示

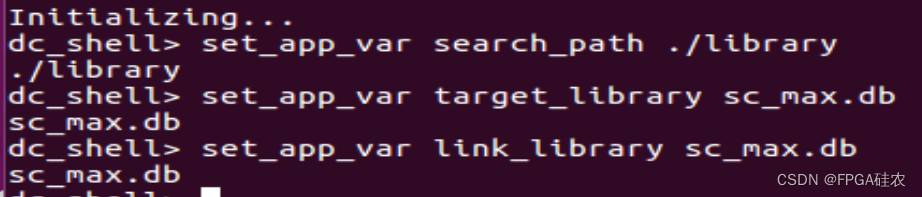

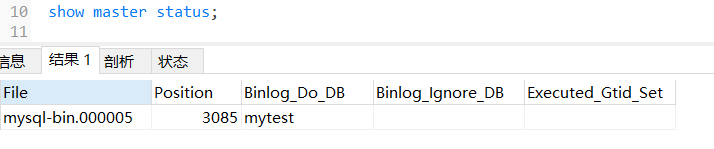

设置环境变量

启动dc,输入

set_app_var search_path ./library

输入

set_app_var target_library sc_max.db

设置目标库

输入

set_app_var link_library sc_max.db

设置链接库

结果如下图所示

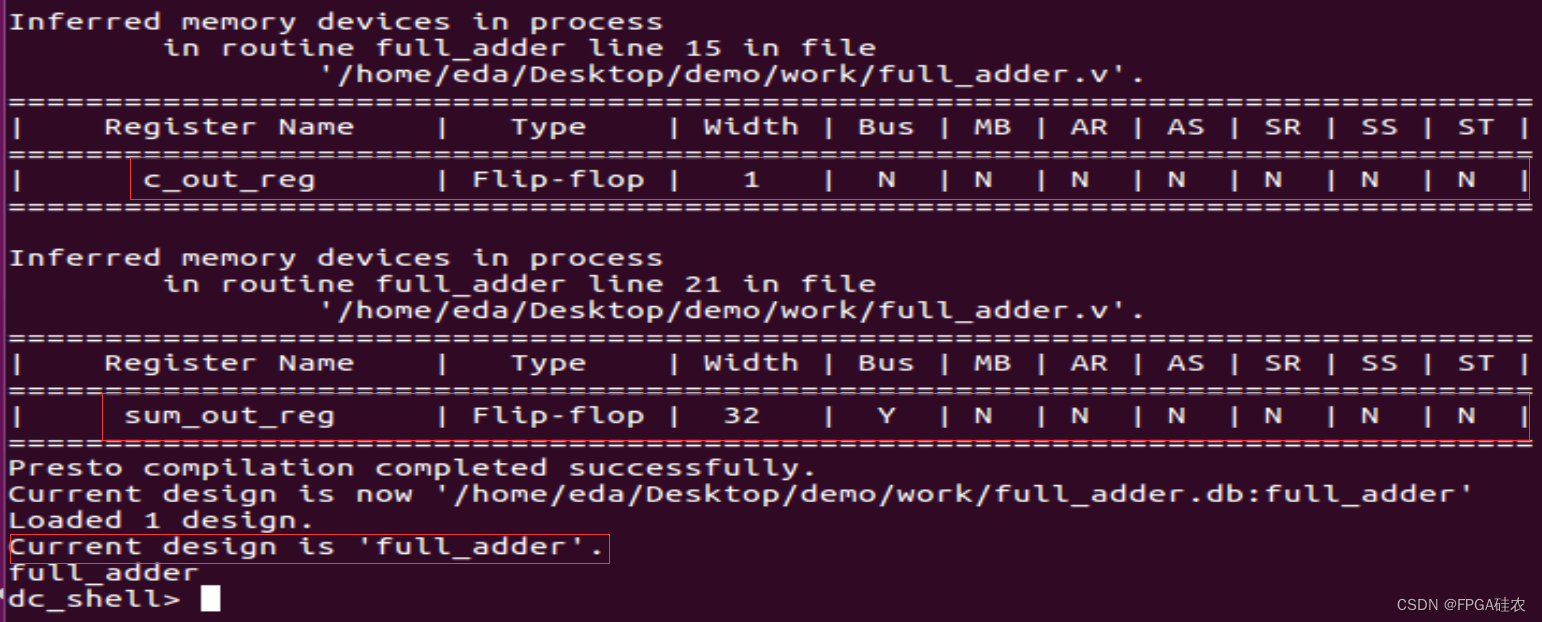

读入设计文件

输入命令:

read_file -format verilog {./full_adder.v}

输入后显示如下:

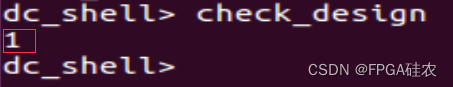

然后输入check_design检查设计,如下图所示

显示1,说明读取无误

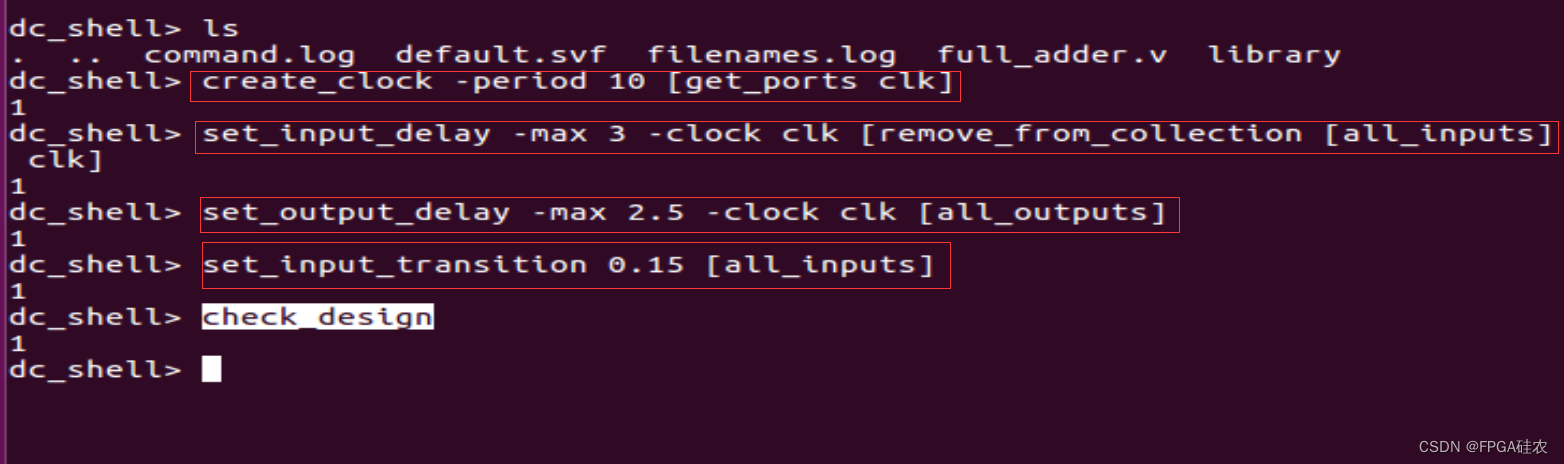

添加约束

创建时钟

create_clock -period 10 [get_ports clk]

设置输入延迟

set_input_delay -max 3 -clock clk [remove_from_collection [all_inputs] clk]

设置输出延迟

set_output_delay -max 2.5 -clock clk [all_outputs]

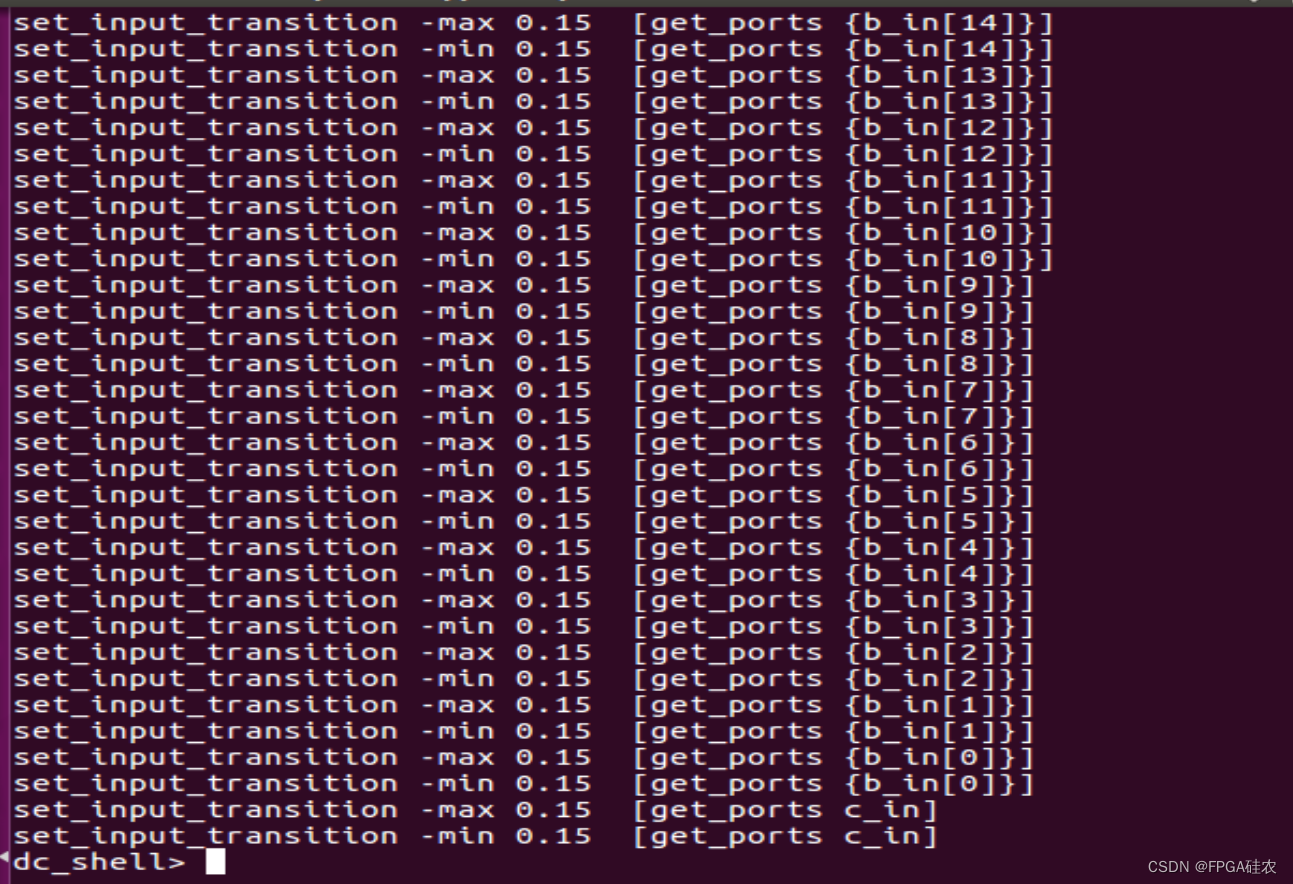

以及设置输入转换时间

set_input_transition 0.15 [all_inputs]

最后输入check_design进行检查

check_design

整个过程如图所示:

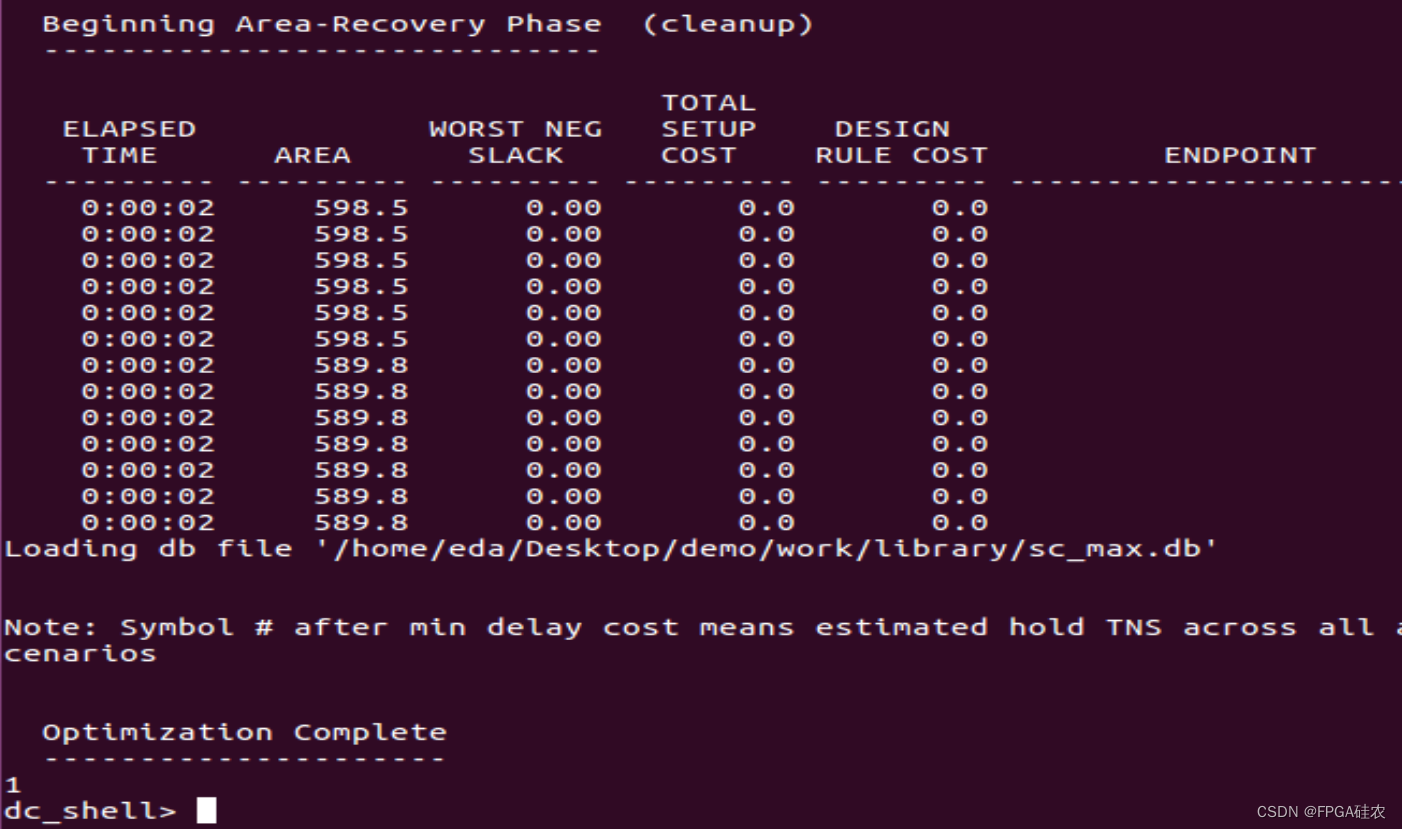

综合

输入compile进行综合。如下图所示

查看综合报告

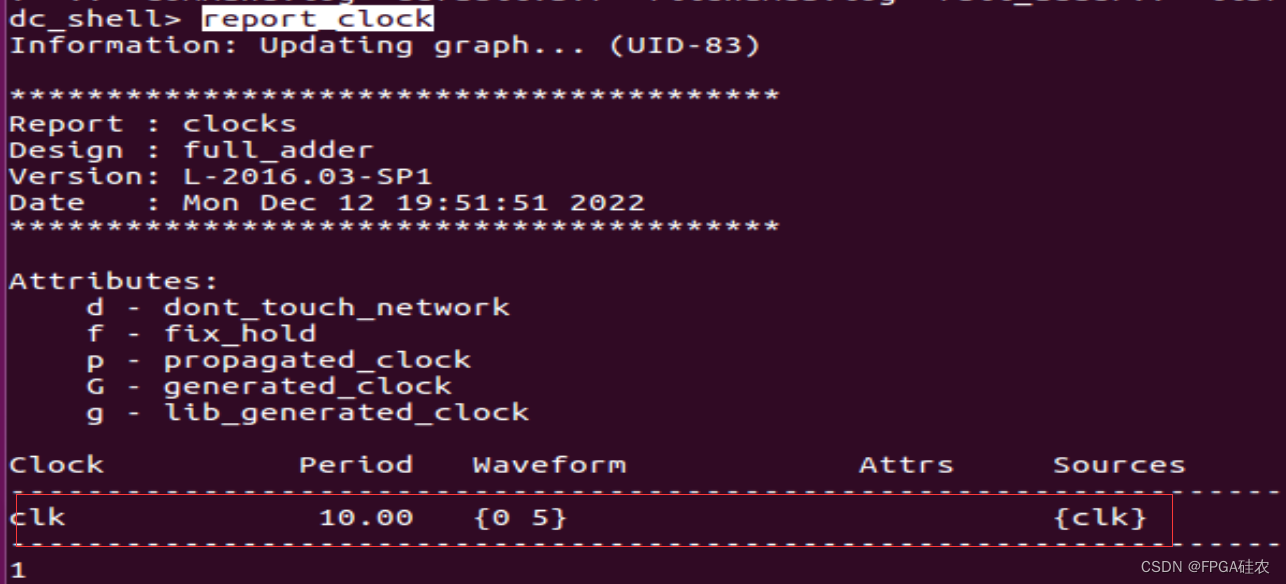

输入report_clock查看时钟

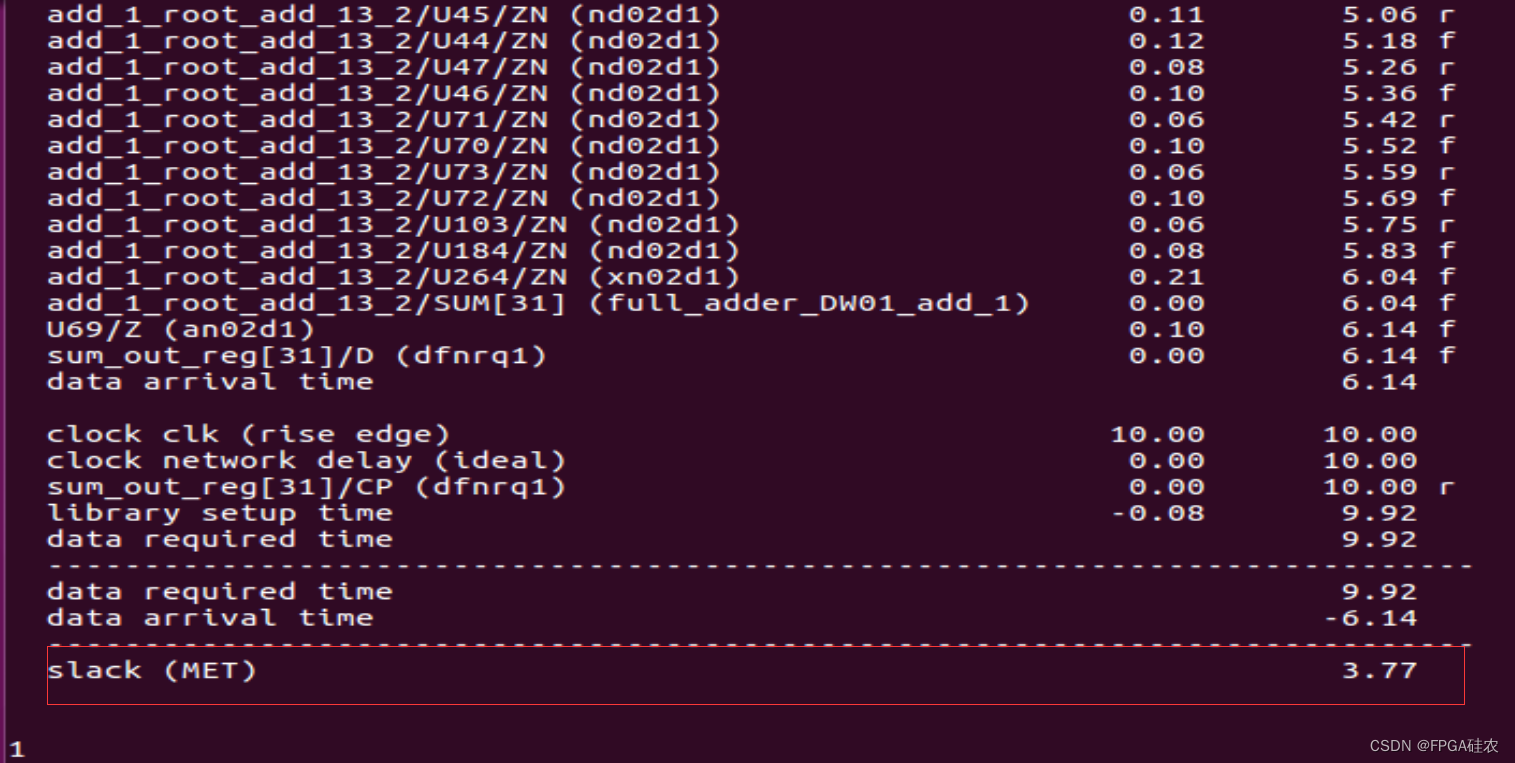

输入report_timing查看时序报告

可以看到,slack为3.77,大于0,时序是MET的。

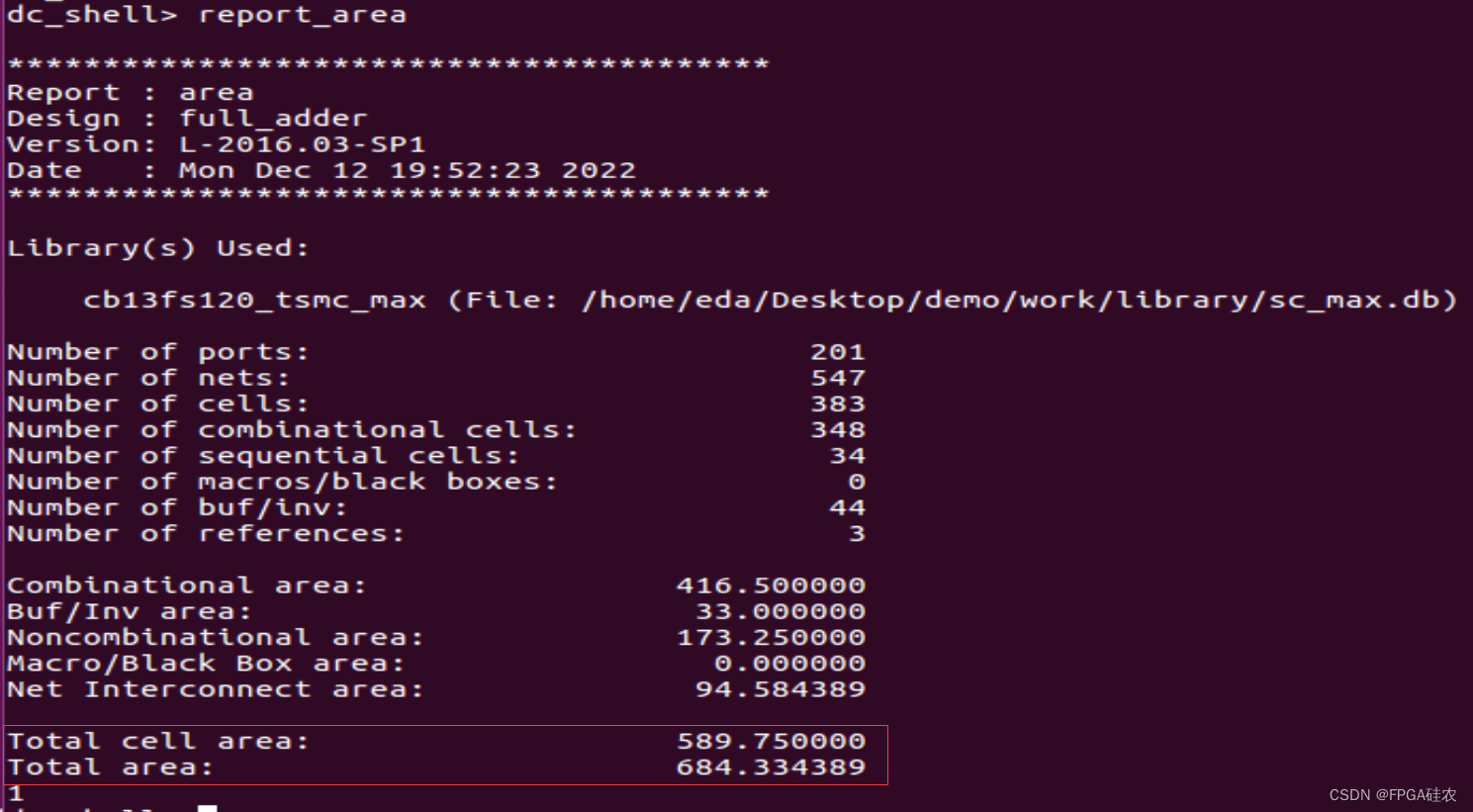

输入report_area查看综合后的面积:

输出相关文件

生成一个.sdc结尾的时序约束文件:

write_sdc full_adder.sdc

文件内容就是我们添加的约束:

输出用于做后仿的.sdf时延文件:

write_sdf full_adder.sdf

输出RTL的网表文件

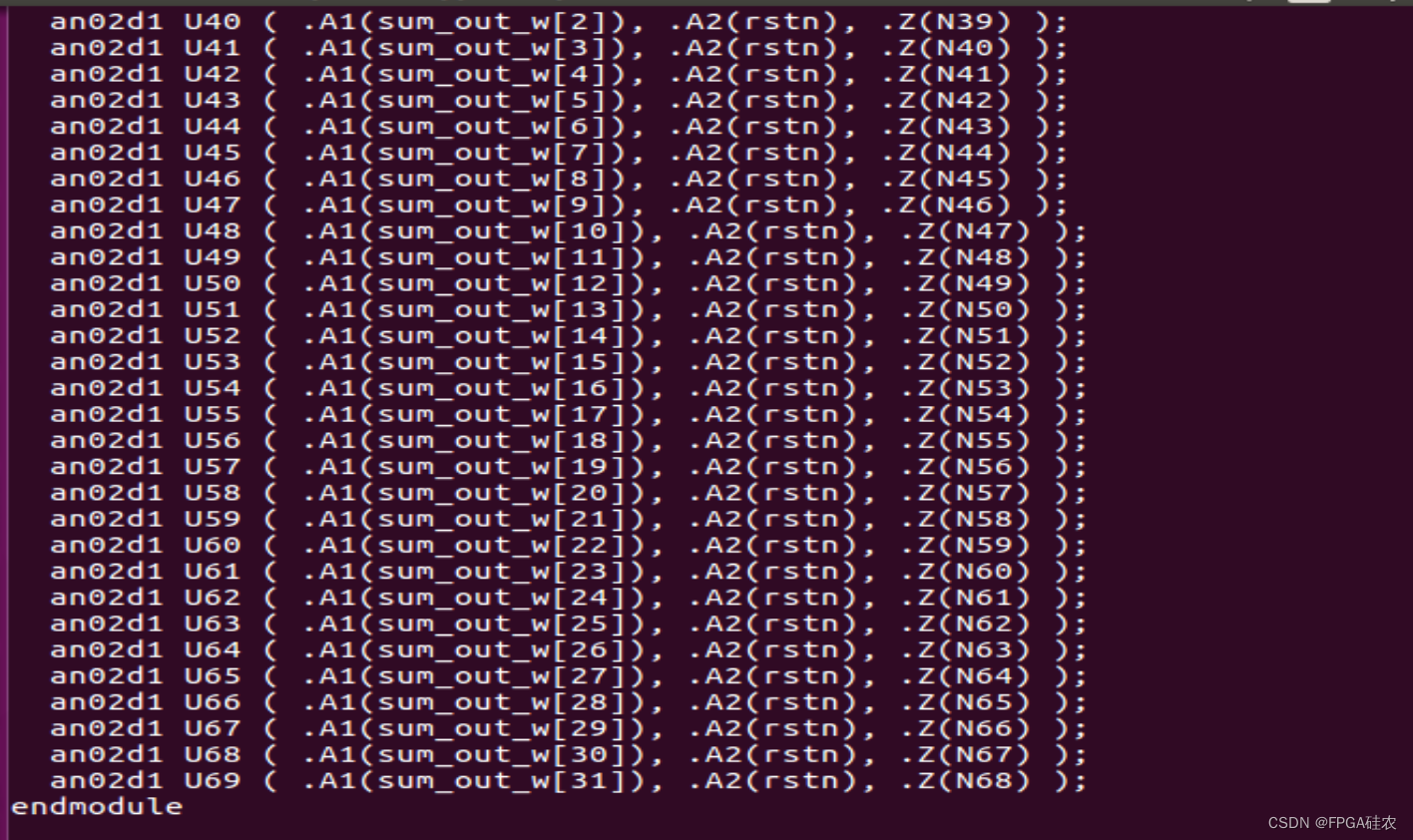

write_file -format verilog -output full_adder_netlist.v

网表文件的内容如下图所示

由图可以发现,网表文件是RTL代码的门级描述。

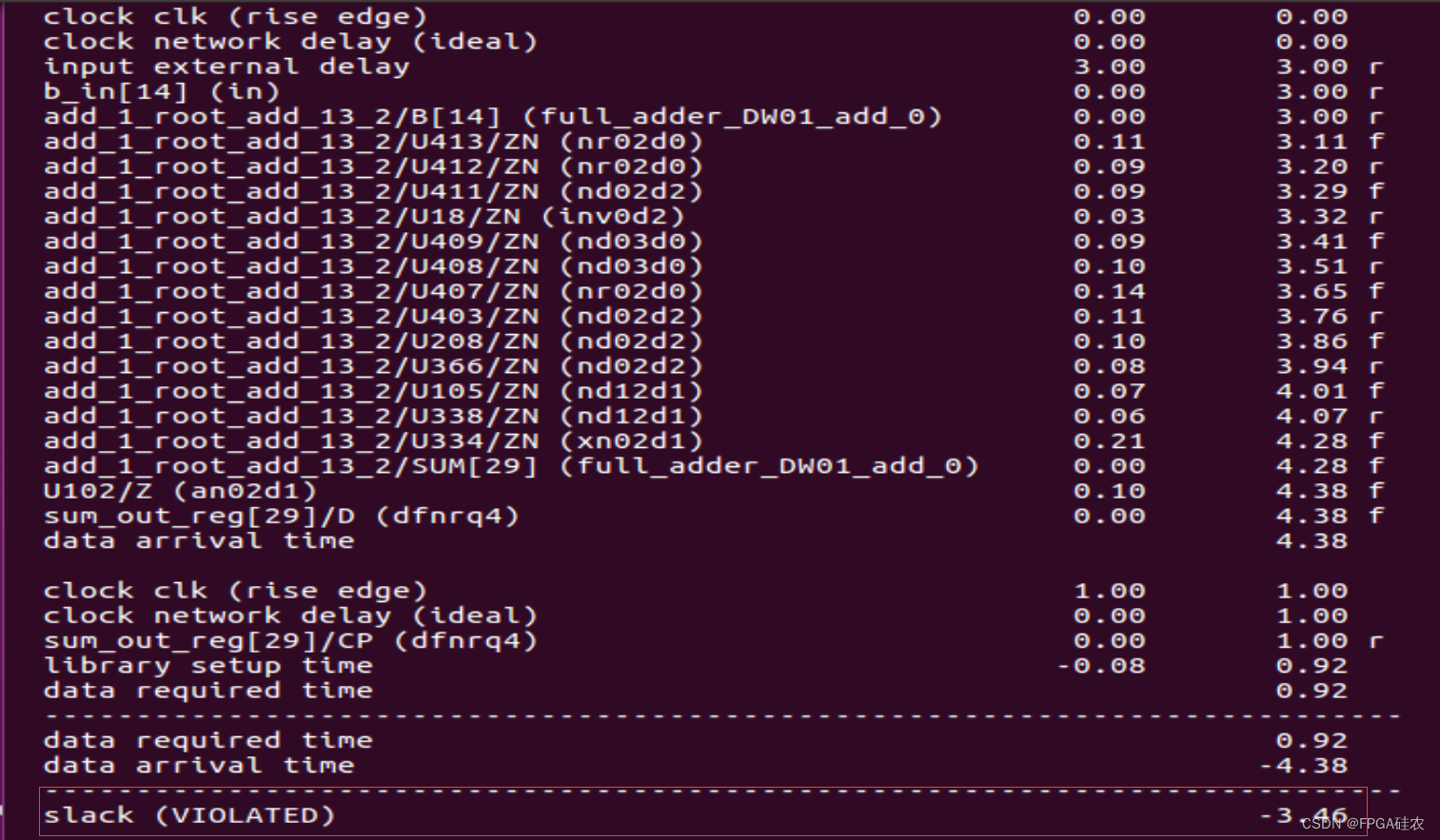

查看时序违例

为了让时序违例,首先修改时钟约束

create_clock -period 1 [get_ports clk]

然后重新输入compile综合。

输入report_timing,结果如下:

可以发现,将时钟约束为1ns后,时序发生违例。

![[vue学习笔记]数组+事件+v-model的使用](https://img-blog.csdnimg.cn/c13a9b4b823344edbf9e9e418e747f9b.png)

![[附源码]计算机毕业设计高校实验室仪器设备管理系统Springboot程序](https://img-blog.csdnimg.cn/8210a349a7264df78c15ac9e589c3507.png)