1 Vivado功能仿真

阅读本文需先学习: FPGA学习----Vivado软件使用

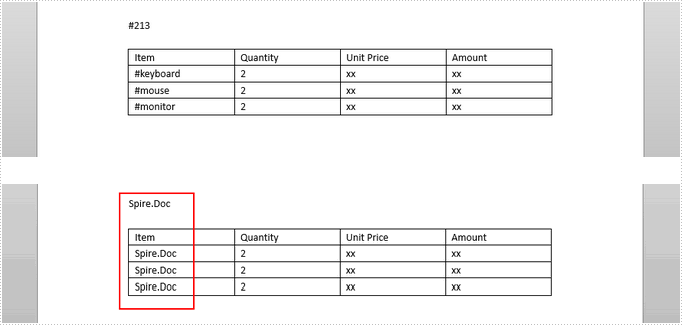

典型的FPGA设计流程,如图所示:

图片来自《领航者ZYNQ之FPGA开发指南》

Vivado 设计套件内部集成了仿真器 Vivado Simulator,能够在设计流程的不同阶段运行设计的功能仿真和时序仿真,结果可以在 Vivado IDE 集成的波形查看器中显示。Vivado 还支持与ModelSim、Verilog Compiler Simulator (VCS)、Questa Advanced Simulator等第三方仿真器的联合仿真

功能仿真需要的文件:

- 设计 HDL 源代码,也被称为 UUT(Unit Under Test): 可以是 VHDL 语言或 Verilog 语言,既可以是设计的顶层模块,也可以是设计的下层子模块

- 测试激励代码,也被称为 TestBench: 根据 UUT 顶层输入/输出接口的设计要求,来产生顶层输入接口的测试激励并监视顶层输出接口

- 仿真模型/库: 根据设计内调用的器件供应商提供的模块而定,如:FIFO、ADD_SUB 等。在使用Vivado Simulator 时,仿真器所需的仿真模型/库是预编译好并集成在 Vivado 中的,因此不需要进行额外的预编译操作,直接加载 HDL 设计和 TestBench 即可执行仿真

1.1 创建TestBench

点击Sources窗口中的+,如图所示:

弹出如下窗口,选择Add or Create Simulation Sources,然后点击Next:

如图所示,点击Create File:

弹出的窗口中输入TestBench的文件名,然后点击OK,如图所示:

点击Finish,如图所示:

弹出的自动定义模块窗口中,点击OK,结束TestBench 源文件端口的定义,如图所示:

弹出一个模块定义的确认按钮,点击Yes,如下图所示:

在 Source 窗口中的Simulation Sources下面的sim_1中找到创建的TestBench文件,双击打开,如图所示:

删除文件中默认的代码,然后替换成 LED 灯闪烁的 TestBench(激励)代码,代码如下:

`timescale 1ns / 1ps //仿真时间单位为1ns,精度为1ps

module tb_led_twinkle (); //TestBench 的模块名定义

//输入

reg sys_clk;

reg sys_rst_n;

//输出

wire [1:0] led;

//信号初始化

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

//生成时钟

always #10 sys_clk = ~sys_clk;

//例化待测设计

led_twinkle u_led_twinkle(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.led (led)

);

endmodule

为了便于仿真,稍微改动一下led_twinkle.v文件的代码,将计时器 cnt 的最大计时值设为 10,如下图所示:

module led_twinkle(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

output [1:0] led //LED灯

);

reg [25:0] cnt;

//对计数器的值进行判断,以输出 LED 的状态

//assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ;

assign led = (cnt < 26'd5) ? 2'b01 : 2'b10 ;//仅用于仿真

//计数器在 0~5000_000 之间进行计数

always @ ( posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

//else if(cnt < 26'd5000_0000)

else if(cnt < 26'd10)//仅用于仿真

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

ila_0 u_ila_0 (

.clk(clk), // input wire clk

.probe0(probe0), // input wire [0:0] probe0

.probe1(probe1), // input wire [1:0] probe1

.probe2(probe2) // input wire [25:0] probe2

);

endmodule

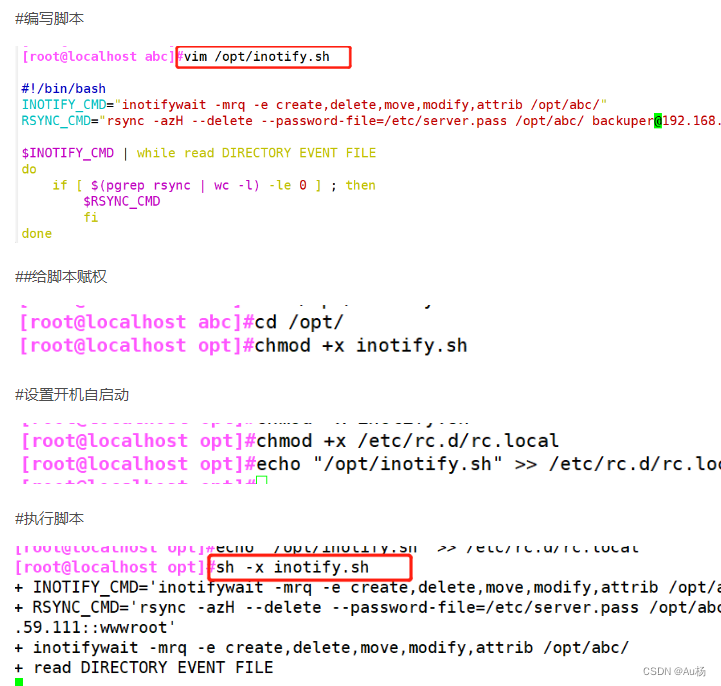

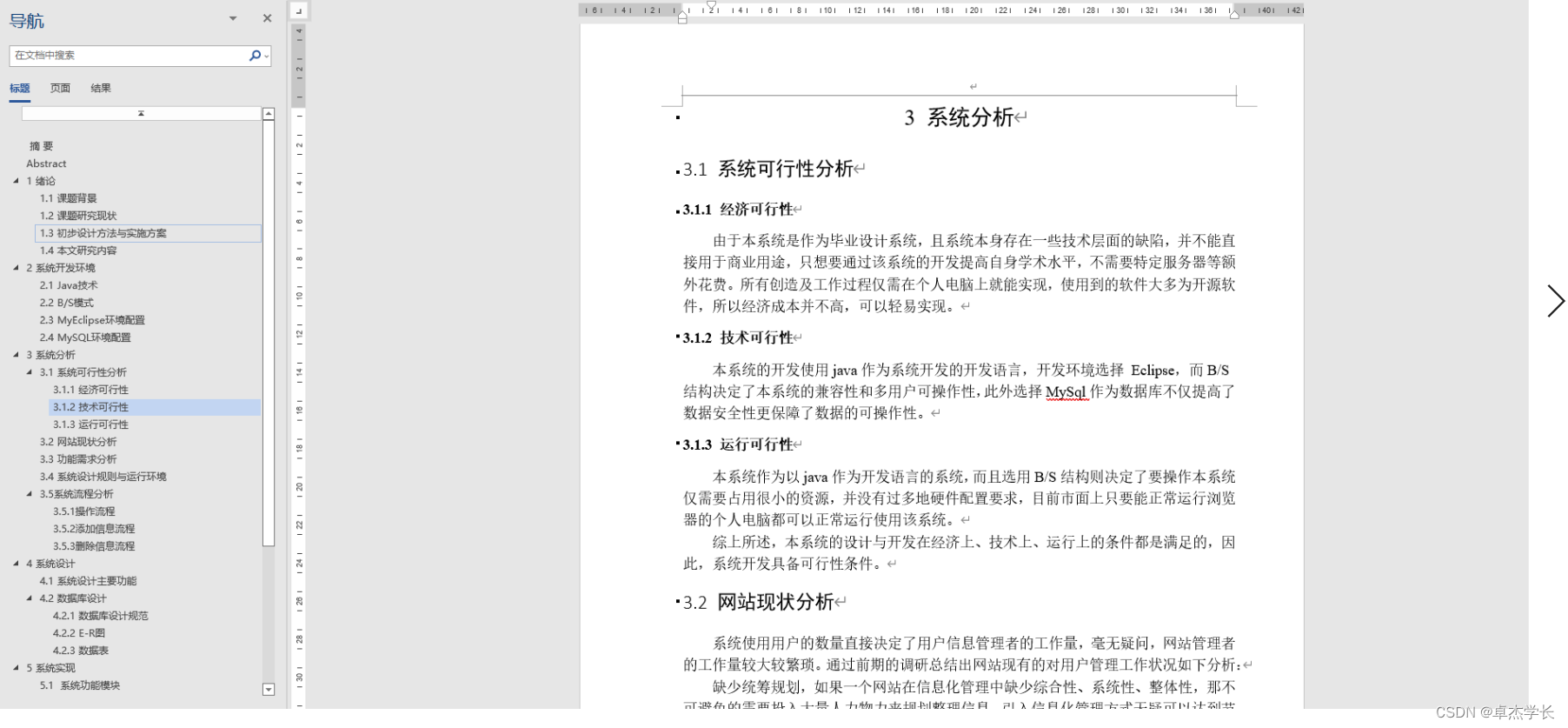

在Flow Navigator窗口中点击Run Simulation,并选择Run Behavioral Simulation,如图所示:

进入仿真界面,如图所示:

- Scope 窗口。 Scope(范围)是 HDL 设计的层次划分,可以看到设计层次结构。选择一个 Scope 层次结构中的作用域时,该作用域内的所有 HDL 对象,包括 reg、wire 等都会出现在Objects窗口中

- Object 窗口。 Objects窗口会显示在Scopes窗口中选择的范围内的所有 HDL 仿真对象,如图所示:

- 波形窗口。 用于显示所要观察信号的波形, 若要向波形窗口添加单个 HDL 对象或多个 HDL 对象,在Objects窗口中,右键单击一个或多个对象,然后从下拉菜单中选择Add to Wave Window选项

点击波形窗口中的保存按钮,如图所示:

弹出窗口,点击Yes,如图所示:

- 仿真工具栏。 仿真工具栏包含运行各个仿真动作的命令按钮,如图所示:

工具栏从左至右依次是:

Restart: 将仿真时间重置为零,波形窗口中原有的波形都会被清除。下次执行仿真时,会从 0时刻重新开始

Run all: 运行仿真

**Run For: ** 运行特定的一段时间。 紧随在后面的两个文本框用于设定仿真时长的数值大小和时间单位

Step: 按步运行仿真,每一步仿真一个 HDL 语句

Break: 暂停当前仿真

Relaunch: 重新编译仿真源并重新启动仿真

Settings 窗口中设置默认仿真时长的参数值,如图所示:

点击Restart,波形窗口中的当前仿真时刻点回归到0ns:

如图所示,开始仿真:

cnt 信号默认显示为 16 进制,为了方便观察,将其设置为 10 进制。对 cnt 信号右键,在弹出的菜单中选择Radix,然后选择Unsigned Decimal,如图所示:

修改后,波形如图所示:

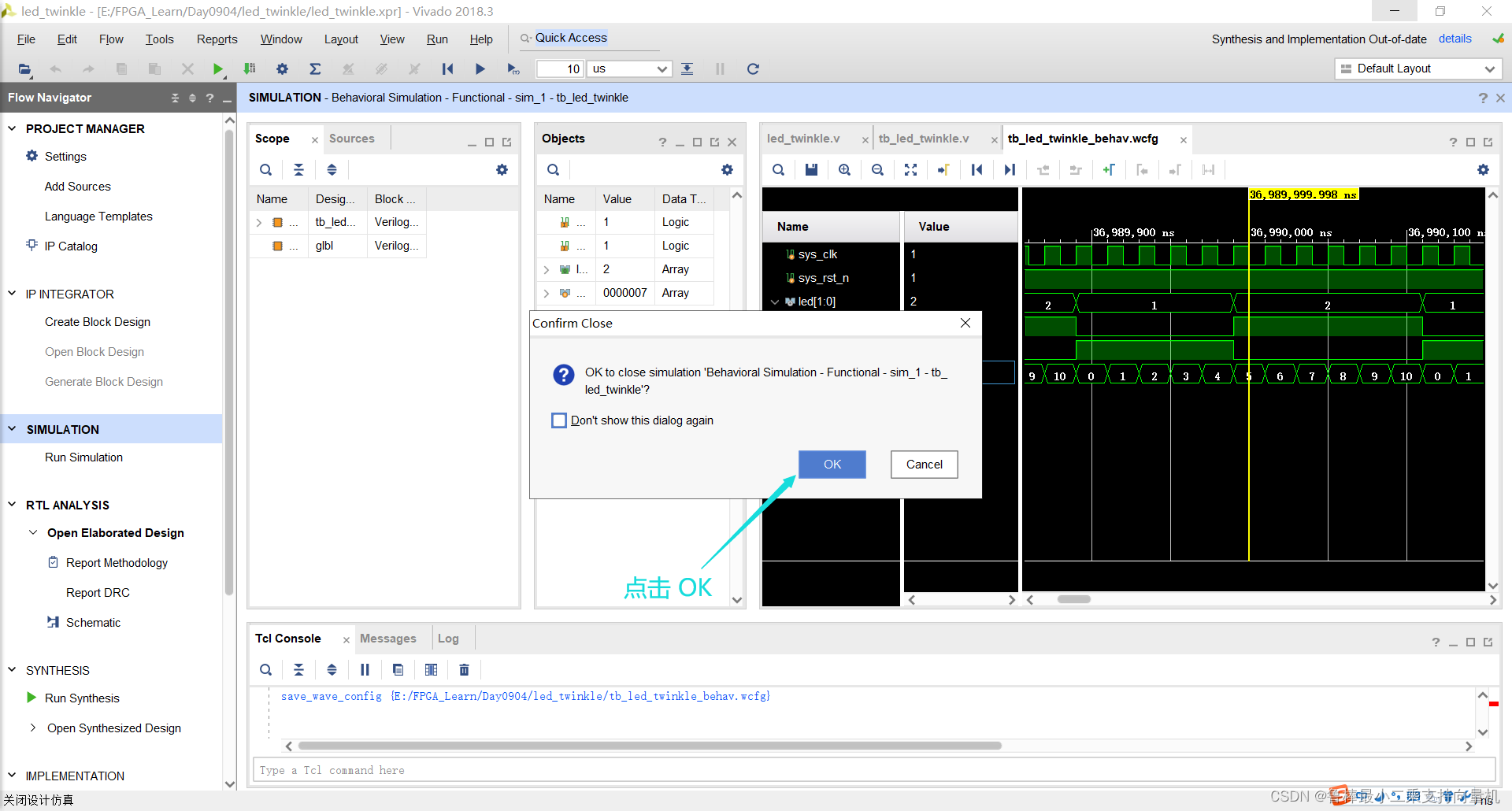

仿真结束后, 可以在 Flow Navigator 窗口中找到 SIMULA TION, 选择 Close Simulation ,如图所示:

弹出关闭仿真的确认窗口,点击OK即可:

致谢领航者ZYNQ开发板,开启FPGA学习之路!

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距