Impedance n.阻抗

dielectric n.电解质

propagation n.传播

标题:Gate Impedance Analysis of SiC power MOSFETs with SiO2 and High-κ Dielectric

阅读日期:2023.7.13

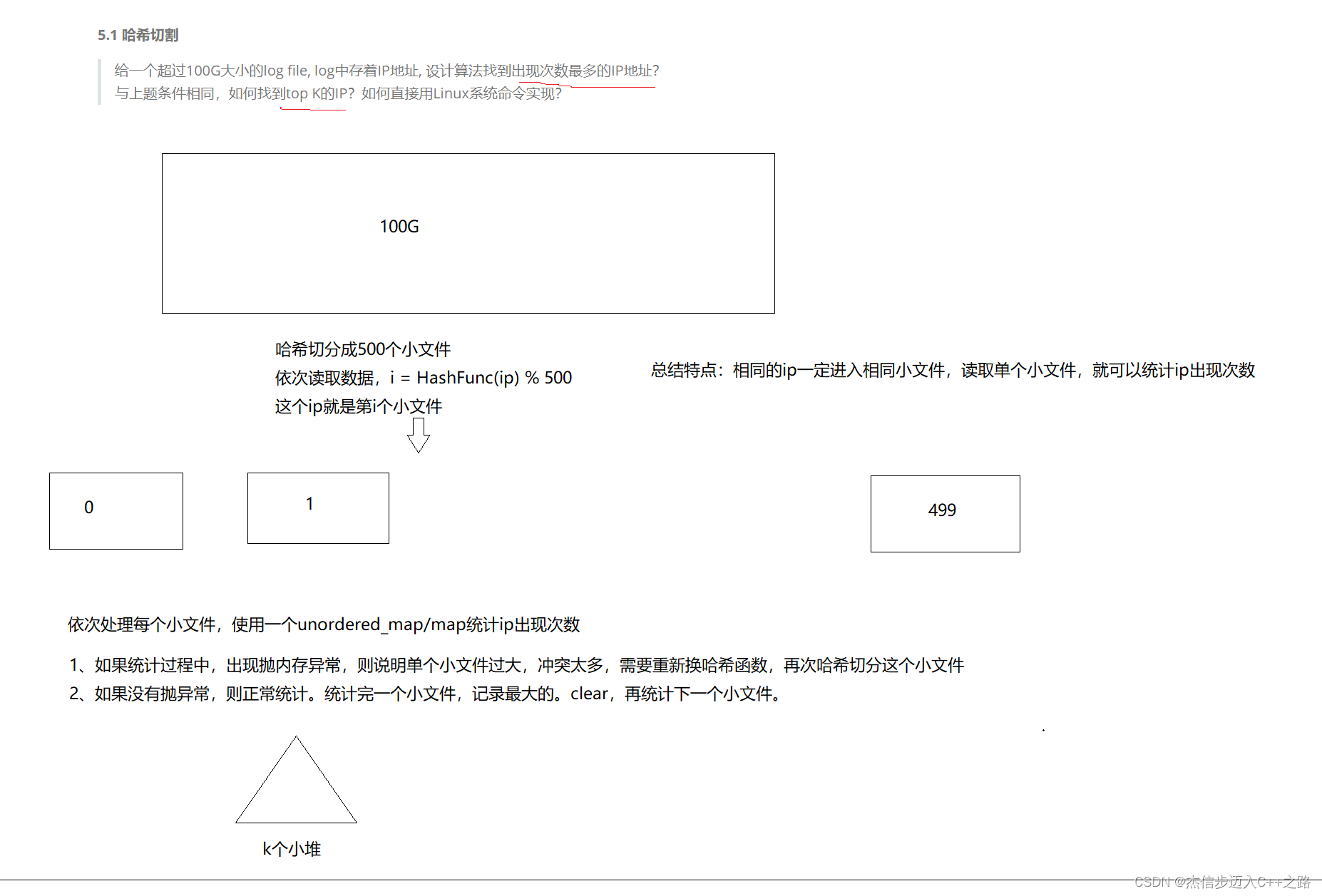

研究了什么

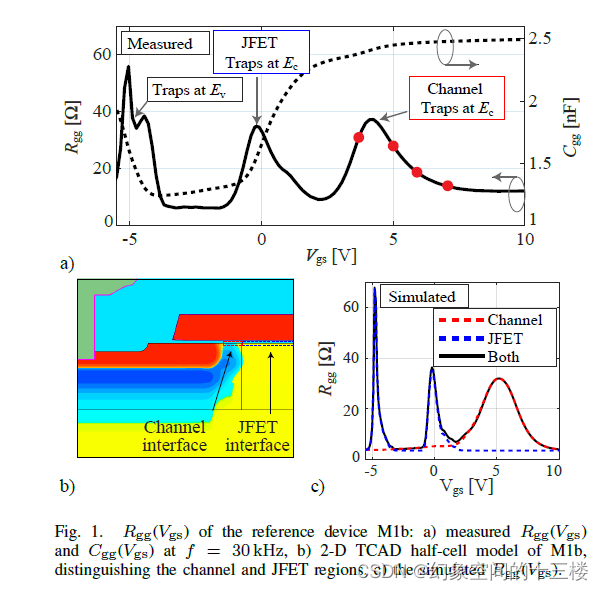

这篇论文研究了SiC功率MOSFET的门电阻Zgg特性,包括SiO2和高κ栅介质,以调查它们的介电-半导体界面质量,并区分通道和JFET贡献。该论文确定了不同SiC MOSFET中Zgg的电压和温度依赖性,并展示了最新设计在接近半导体界面陷阱方面的改进。该论文进行了实验表征和TCAD器件模拟以支持结论。

文章创新点

·该论文首次证明了通过测量Zgg(Vgs,f,T)可以区分通道和JFET区域中Dit的影响。

·该论文展示了如何利用SiC功率MOSFET的门电阻Zgg特性来调查它们的介电-半导体界面质量,并区分通道和JFET的贡献。

·该论文确定了不同SiC MOSFET中Zgg的电压和温度依赖性。

·该论文展示了最新设计在接近半导体界面陷阱方面的改进。

·该论文利用实验表征和TCAD器件模拟来支持结论。

文章的研究方法

电导方法:在与通道峰相关的Vgs点上对参考器件应用电导方法,以获得短路漏源端的MOSFET等效模型。

门电阻Zgg特性分析:使用门电阻Zgg特性来调查具有SiO2和高κ栅介质的SiC功率MOSFET的介电-半导体界面质量,并区分通道和JFET的贡献。

实验表征:进行实验表征以支持研究结论。

TCAD器件模拟:使用TCAD器件模拟来支持研究结论。

文章得出的结论

所提出的Rgg(Vgs)特性化方法允许对SiC功率MOSFET进行Dit评估,并可与制造过程中的不同步骤相关联。

可以通过测量Zgg(Vgs,f,T)来区分通道和JFET区域中Dit的影响。

确定了不同SiC MOSFET中Zgg的电压和温度依赖性。

最新设计在接近半导体界面陷阱方面显示出改进。

进行实验表征和TCAD器件模拟以支持结论。

](https://img-blog.csdnimg.cn/9a639a1eac2f440bb6146b5d5c4a065b.png#pic_center)