系列文章目录

FPGA时序约束(一)基本概念入门及简单语法

文章目录

- 系列文章目录

- 前言

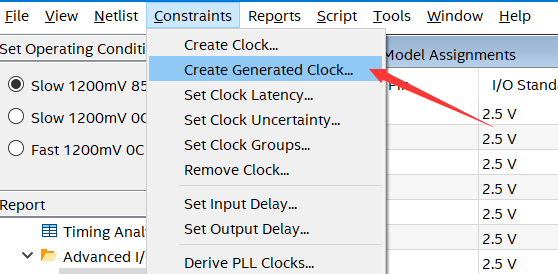

- Quartus时序约束

- 不进行时序约束的后果

- 时序约束方法

- TimeQuest Timing Analyzer 工具来对工程添加约束。

- 创建网表

- 读取SDC文件

- 创建时钟(Create Clock)

- 写入SDC文件

- 时序约束语法补充

- 参考文章

前言

最近由于不懂时序约束,在高速信号采集上面吃了很多亏,不知道系统工作异常的原因是什么。记录一下查到的资料,有些许自己的理解,可能有误。

Quartus时序约束

不进行时序约束的后果

在程序编译之后,会出现时序约束标红

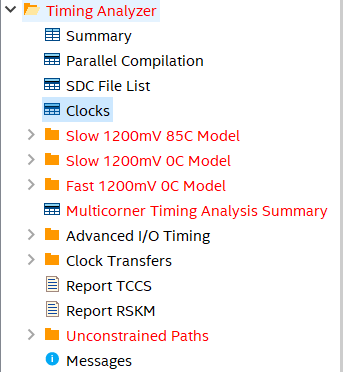

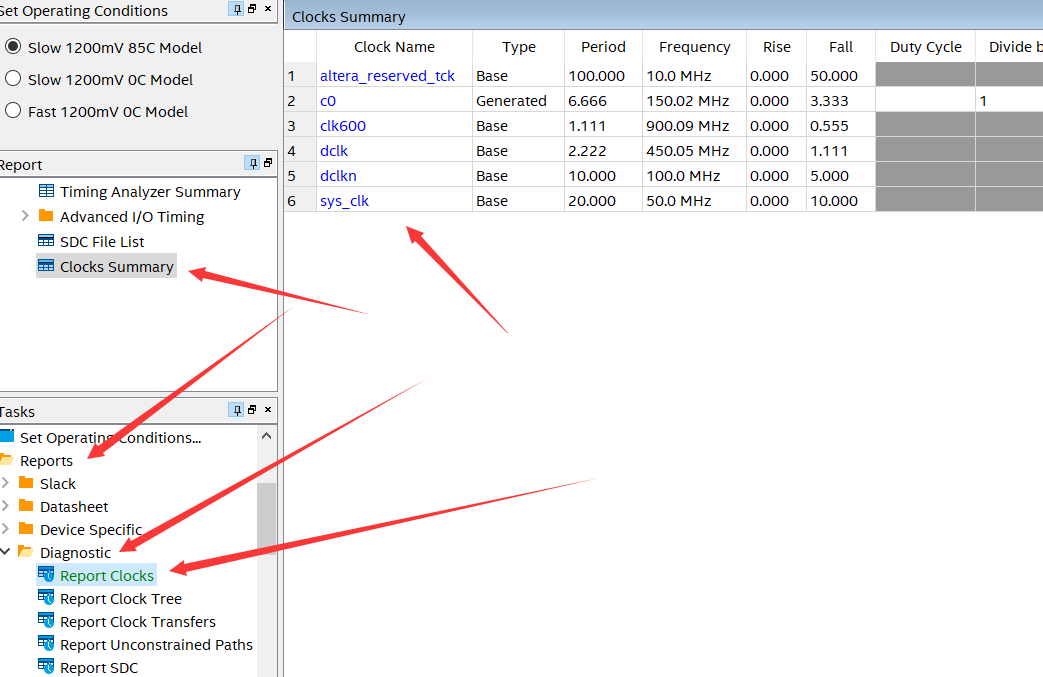

如果不自己编写时序约束文件,就会出现系统进行默认分配,这里如果没有自己编写sdc时序分析文件,quartus会自动分析潜在的时钟,如下图,在clock中查看

可能我们的输入是50M的时钟,系统按照1000M时钟进行了约束,但是你的FPGA内部寄存器和连线导致的延时,它不能满足1000M的时钟,所以就会标红。一些简单的程序,系统按照1000M去优化是没有问题的,但是复杂的程序就会出错了

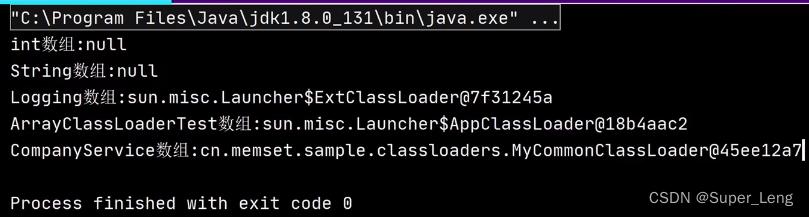

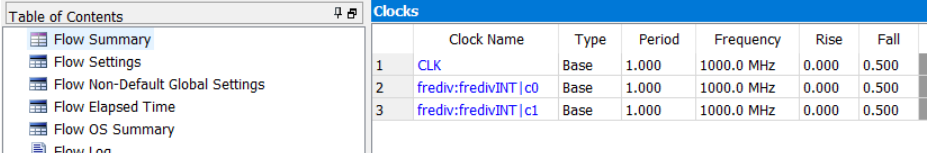

在TimeQusst Timing Analyzer下,slow 1200mv 85C model和slow 1200mv 0C Model以及Fast 1200mv 0C model里,quartus根据代码程序,按照刚才的clock会进行分析,Fmax表示当下条件下,该时钟的最大频率

-

Clocks:这一项是显示当前的设计中有哪些时钟信号

-

Slow 1200mV 85C Model:芯片内核供电电压 1200mV,工作温度85度情况下的慢慢速传输模型。

-

Slow 1200mV 0C Model:芯片内核供电电压 1200mV,工作温度0度情况下的慢速传输模型。

-

Fast 1200mV 0C Model:芯片内核供电电压 1200mV,工作温度0度情况下的快速传输模型。

时序约束方法

在上一篇文章已经简单介绍了一些时序约束的语法,现在介绍如何利用quaruts编写时序约束

- 熟悉了可以直接自己编写SDC文件

- 用 TimeQuest Timing Analyzer Wizard 软件按照向导的指引操作。

- 可以使用 TimeQuest Timing Analyzer 工具用图形化界面添加约束。

TimeQuest Timing Analyzer 工具来对工程添加约束。

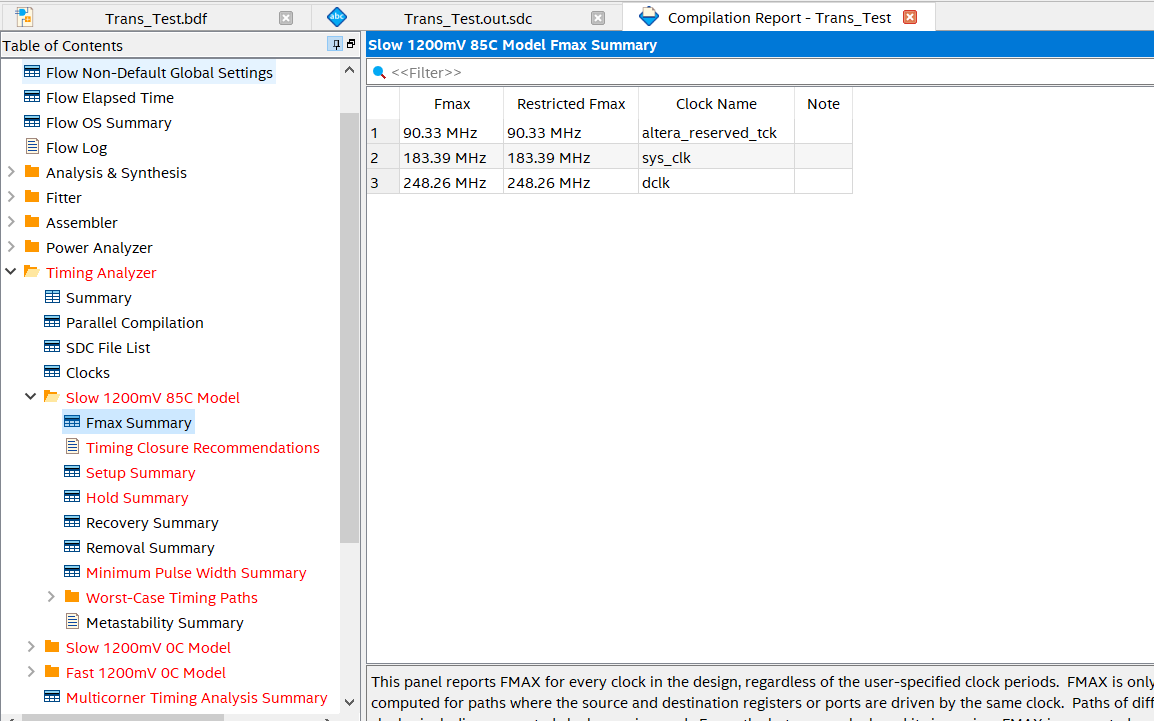

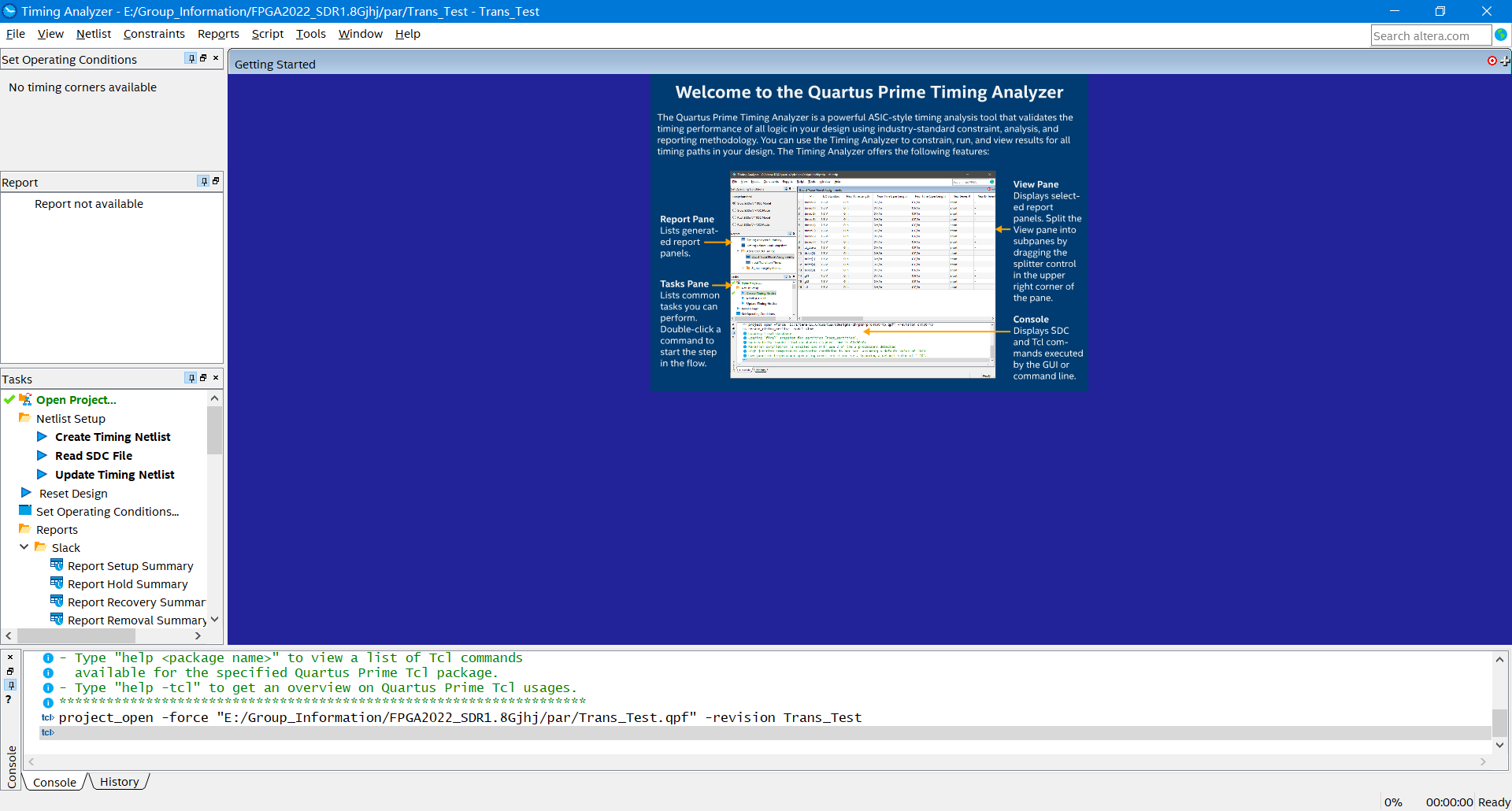

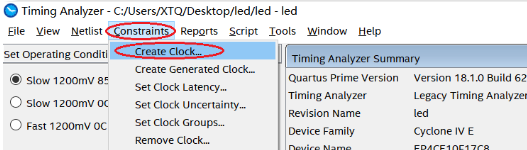

菜单栏依次点击:Tools->TimeQuest Timing Analyzer 可以打开,也可以直接点击工具栏里的 TimeQuest Timing Analyzer 图标

创建网表

约束的对象就是网表,网表就是 Quartus 软件经过编译,布局布线后得到的实际电路信息,该电路信息就是对应下载到芯片中后实际在芯片中呈现的电路。直接双击 Create Timing Netlist 选项就可以创建网表。

读取SDC文件

时序约束文件可以指导EDA软件(Quartus)进行布局布线,还可以指导时序分析软件(TimeQuest Timing Analyzer)对EDA软件编译得到的网表进行分析报告。

如果用户没有编写,就是使用默认那个1000M约束的默认文件。

创建时钟(Create Clock)

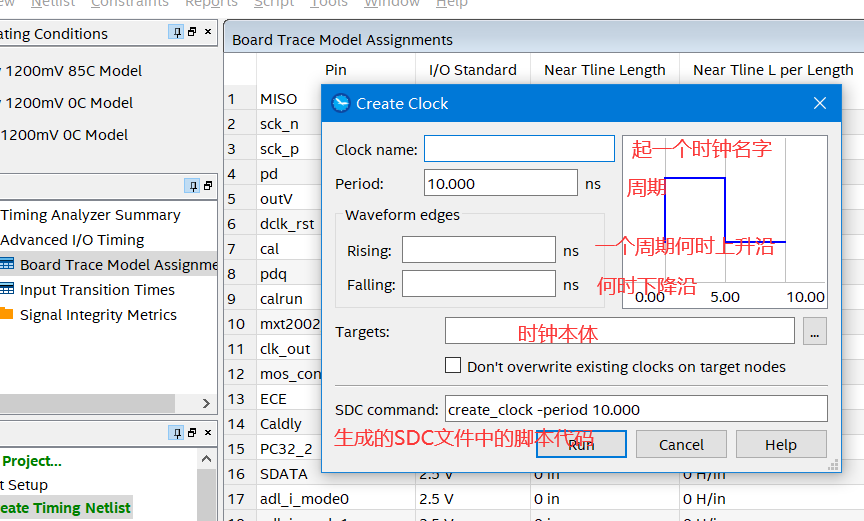

创建时钟约束,就是为当前网表模型指定一个明确的时钟信号。这样时序分析软件就能够基于该时钟参数,对网表中的各信号进行分析了。

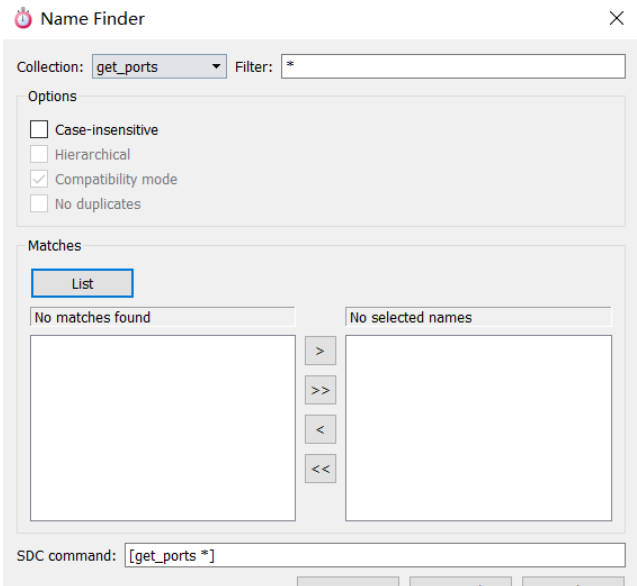

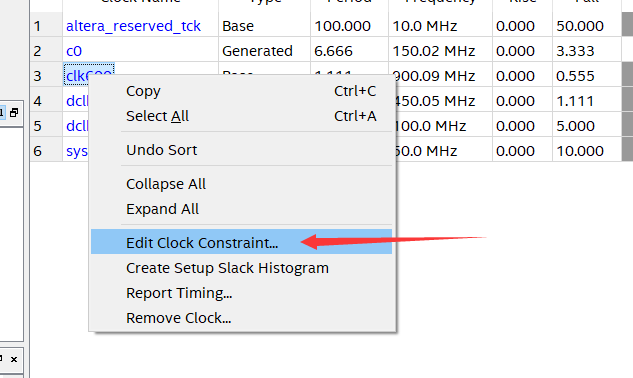

在这个界面筛选时钟以及选择时钟本体

例如:

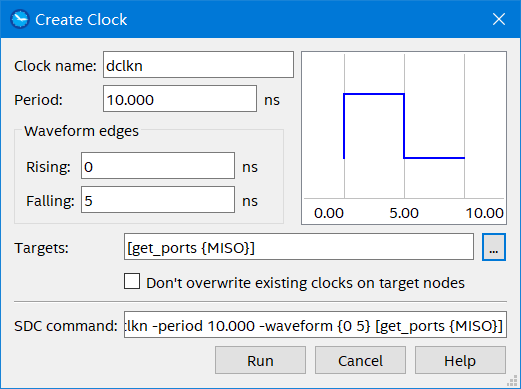

将代码中的 MISO信号重命名为dclkn进行约束,占空比为50%,周期是10ns。(上升沿和下降沿不填默认是50%占空比)

命令窗:

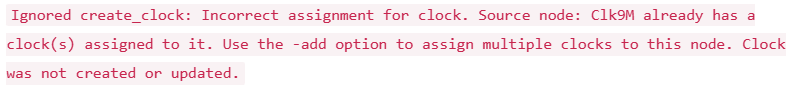

如果出现:

约束被忽略了,因为系统默认约束过了那么就不能创建了,只能更改

注意:clock name不能改,改了还是会被忽略

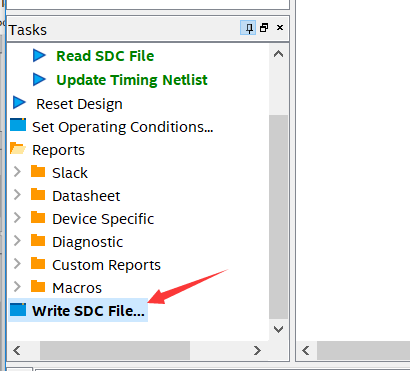

写入SDC文件

到这里就基本完成了,最后记得把SDC文件添加到工程里面就可以了

时序约束语法补充

上篇文章有一些简单的介绍语法,这次又学习了一些比较详细的,总共有13种约束命令。以下命令都可以在菜单的constraint里面找到,直接设置好参数让软件自动生成,当然也可以自己生成添加。(都是参考文章末尾的第二篇文章的,还有很多看不懂,慢慢加入东西吧)

-

Creat clock

约束外部进入FPGA的时钟,其他IC产生的给FPGA的类时钟信号 -

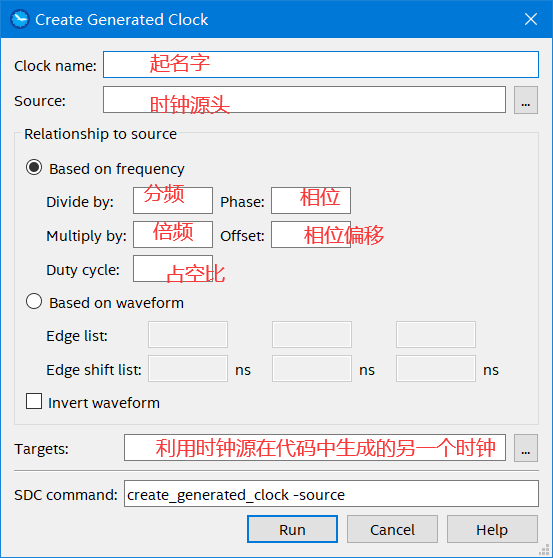

Creat generated clock

约束pLL(derive_pll_clocks)

约束FPGA输出到外部的时钟

时钟多路复用器(clock muxes)

涟漪时钟(ripple clocks),FPGA内部寄存器输出的时钟

phase:是偏移多少度

offset:是偏移多少ns

例子:create_generated_clock -name 起名字 -source [get_ports {原时钟}] [get_ports {生成的时钟}] -

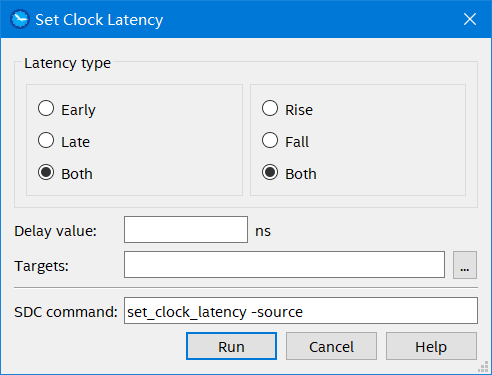

set_clock_latency

对输入到FPGA的时钟及类时钟(其他芯片产生的时钟给FPGA)

可以自己选择延迟类型

late指最大时钟延迟,early指最小时钟延迟(第二篇参考文章里面有详细解释,没太看懂) -

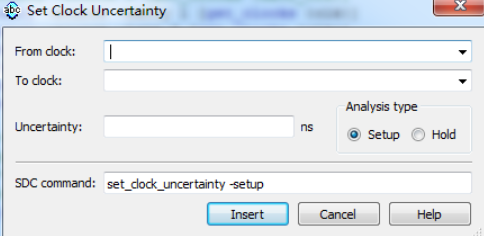

Set_clock_uncertainty

对时钟出现的抖动进行约束,是一个时钟到另一个时钟的约束,用 derive_clock_uncertainty约束命令不需要确定uncertainy的时间,

-

Set_clock_groups

把相关的时钟分成一个组,与其它不相关的时钟区分开。 timequest只对这组内的时钟域进行分析,组间的时钟路径将不会分析。 -

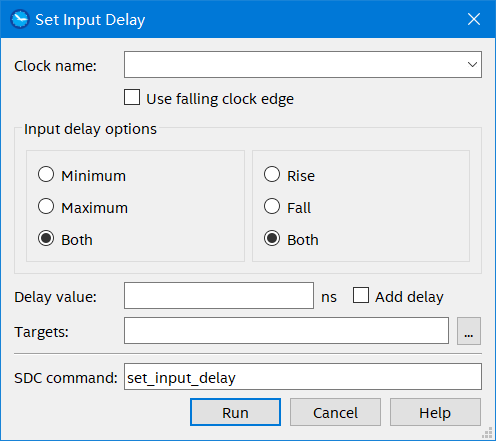

set_input_delay

对外部IC输入到FPGA管脚的约束,这个约束命令中的延迟信息需要告诉timequest。

外部IC到FPGA输入管脚Din[3:0]的最大延时是4ns,最小延时是2ns,外部IC时钟是ext1_clk。add delay选项用于说明有另外的外部寄存器连接到端口,通常用于对双倍速率接口的约束。

-

set_output_delay

FPGA输出到IC的延迟,与输入延迟相似 -

set false path

不要分析某个路径或某组路径 -

set_multicycle_path

两个寄存器间的数据传输在一个周期内没法完成时,我们可以通过该约束命令来改变他的建立关系值和保持关系值让其满足时序要求。 -

set muximum delay和set minimum delay

一般建议不要用

参考文章

一、FPGA时序分析工具(TimeQuest)

二、timequest静态时序分析学习笔记——命令约束