ArduJtag:Arduino上的轻量级JTAG协议底层驱动库

news2026/3/23 8:44:19

1. 项目概述ArduJtag 是一款专为 Arduino 平台设计的轻量级 JTAG 协议底层驱动库其核心目标是将复杂的 IEEE 1149.1 边界扫描Boundary-Scan协议抽象为可直接操控物理引脚、可编程时序、可组合状态机的嵌入式级接口。它并非通用型调试器固件而是面向硬件工程师与协议研究者的“JTAG 引脚控制器”——在不依赖专用 JTAG 调试器芯片如 FT2232H、CPLD 桥接器的前提下仅使用标准 Arduino 开发板如 Uno、Nano、Mega2560、Due、ESP32的 GPIO 和精确延时能力完成对任意 JTAG TAPTest Access Port设备的原始位操作。该库继承自 JTAGduino 项目并在《Diving into JTAG protocol》系列技术文章的实践验证中持续演进。其工程价值不在于替代 OpenOCD 或 ST-Link而在于提供一种“可触摸、可调试、可教学”的 JTAG 协议实现路径从 TCK 的上升沿采样、TMS 的状态迁移控制、TDI/TDO 的同步移位到 IR/DR 寄存器的串行加载与回读全部暴露于用户代码层面。这种设计使 ArduJtag 成为理解 JTAG 状态机、验证自定义 TAP 控制器、逆向分析未知 JTAG 设备、或构建低成本边界扫描测试平台的理想工具。2. JTAG 协议基础与 Arduino 实现约束2.1 JTAG 四线物理层与状态机本质JTAG 接口由四根核心信号线构成TCKTest Clock同步时钟所有数据采样与状态迁移均以 TCK 上升沿为基准TMSTest Mode Select状态机控制线在每个 TCK 周期采样一次决定 TAP 控制器下一状态TDITest Data In串行数据输入用于向当前选中的寄存器IR 或 DR写入数据TDOTest Data Out串行数据输出用于从当前寄存器读取数据其有效数据在 TCK 下降沿稳定在上升沿被采样。JTAG TAP 控制器是一个 16 状态有限状态机FSM其迁移完全由 TMS 电平序列驱动。关键状态包括Test-Logic-Reset、Run-Test/Idle、Shift-IR、Shift-DR、Update-IR、Update-DR等。任何 JTAG 操作如写 IR、读 DR都必须严格遵循状态机路径例如要进入Shift-IR状态需从Test-Logic-Reset或Run-Test/Idle出发依次施加特定长度的 TMS 序列典型为 5 位00001。2.2 Arduino 平台的工程挑战与应对策略在通用微控制器上实现 JTAG 面临三大硬性约束时序精度要求JTAG 标准未规定最大时钟频率但多数器件支持 1–10 MHz。Arduino UnoATmega328P主频仅 16 MHz若采用digitalWrite()delayMicroseconds()实现 TCK其函数调用开销与中断延迟将导致 TCK 周期严重抖动无法满足高速通信需求。GPIO 驱动能力Arduino 引脚输出电流有限约 20 mA而部分 JTAG 目标板可能要求更高驱动强度或存在电平不匹配如 3.3 V vs 5 V。无硬件移位器缺乏专用 SPI 或 UART 外设用于自动串行化所有位操作必须由软件循环完成。ArduJtag 的应对方案是分层设计底层引脚操作默认使用PORTx寄存器直写如PORTB | _BV(PORTB0)替代digitalWrite()将单次 GPIO 切换压缩至 1–2 个 CPU 周期可配置时钟生成通过#define JTAG_TCK_DELAY_US(n)宏定义最小 TCK 周期单位微秒实际 TCK 高低电平时间由该值决定用户可根据目标器件手册调整如 STM32F407 典型支持 ≥100 kHz电平适配建议文档明确要求用户外接电平转换器如 TXB0104或限流电阻库本身不处理电气兼容性纯软件移位所有ir()、dr()、sequence()函数内部均采用位操作循环逐位设置 TDI、采样 TDO、更新 TMS确保协议行为 100% 可控。3. 核心 API 接口详解ArduJtag 提供三个层级的 API寄存器级IR/DR、原子操作级sequence、以及底层引脚配置。所有函数均声明于Jtag.hpp头文件中使用前需通过#include Jtag.hpp引入。3.1 JTAG 引脚初始化与配置// 构造函数指定 Arduino 引脚编号 Jtag::Jtag(uint8_t tckPin, uint8_t tmsPin, uint8_t tdiPin, uint8_t tdoPin); // 初始化配置引脚模式执行 TAP 复位 void Jtag::begin();tckPin,tmsPin,tdiPin必须为输出模式tdoPin必须为输入模式begin()内部执行标准 JTAG 复位序列拉高 TMS 保持至少 5 个 TCK 周期强制 TAP 进入Test-Logic-Reset状态为后续操作建立确定起点。3.2 IRInstruction Register写入接口/** * brief 向 JTAG 指令寄存器IR写入指令码 * param instruction 指令码值低位在前Little-Endian Bit Order * param length 指令长度单位bit通常为 4 或 5 */ void Jtag::ir(uint16_t instruction, uint16_t length);关键参数说明参数类型含义典型值示例instructionuint16_t待写入的指令码按 LSB First 顺序排列BoundaryScan TAP 的BYPASS指令为0b11111→0x1FDebug TAP 的IDCODE指令为0b1110→0x0Elengthuint16_t指令总位数BoundaryScan TAP 为 5 bitDebug TAP 为 4 bit多 TAP 串联场景下的指令构造逻辑 当多个 TAP 串联如 STM32F407 的 BoundaryScan Debug时IR 指令必须按物理链路顺序拼接且遵循 LSB First 规则。假设链路为[BoundaryScan] - [Debug]则BoundaryScan IR 0b11111(5-bit)Debug IR 0b1110(4-bit)串联后总 IR Debug_IRBoundaryScan_IR0b11100b111110b111011111按 LSB First 解释0b111011111的 LSB 为最右位故字节序需反转。实际发送的 9-bit 序列为0b111110111→ 十六进制0x1FE因此向该双 TAP 链写入BYPASSIDCODE的正确调用为jtag.ir(0x1FE, 9); // instruction0x1FE, length93.3 DRData Register读写接口/** * brief 向/从 JTAG 数据寄存器DR读写数据 * param input 指向输入数据缓冲区的指针发送给目标的数据 * param length 数据总长度单位bit * param output 指向输出数据缓冲区的指针从目标读取的数据 */ void Jtag::dr(uint8_t *input, uint32_t length, uint8_t *output);数据缓冲区格式规范input和output均为uint8_t数组每个字节存储 8 位数据LSB 在前length可为任意值不限于 8 的倍数库自动计算所需字节数并处理末尾位若input nullptr则 TDI 持续输出0若output nullptr则忽略 TDO 采样。示例向 STM32F407 Debug TAP 的 IDCODE 寄存器32-bit发起读取IDCODE 寄存器位于 Debug TAP长度为 32 位。读取时需发送 32 个0因 IDCODE 为只读寄存器输入数据无意义同时采集 32 位 TDO 响应uint8_t tx_buffer[4] {0x00, 0x00, 0x00, 0x00}; // 32-bit zeros, LSB first uint8_t rx_buffer[4]; jtag.dr(tx_buffer, 32, rx_buffer); // rx_buffer 现在包含 32-bit IDCODE按 LSB first 存储 // 例如rx_buffer {0x00, 0x00, 0x00, 0x10} 表示 IDCODE 0x100000003.4 任意 JTAG 序列操作接口/** * brief 执行自定义 JTAG 位操作序列 * param n 操作步数即 TCK 周期数 * param tms TMS 电平数组每元素对应一个 TCK 周期的 TMS 值0 或 1 * param tdi TDI 电平数组每元素对应一个 TCK 周期的 TDI 值0 或 1 * param tdo 指向 TDO 采样结果数组的指针可为 nullptr * return 操作状态JTAG::OK 或 JTAG::ERROR */ JTAG::ERROR Jtag::sequence(size_t n, const uint8_t tms[], const uint8_t tdi[], uint8_t *tdo);此接口是 ArduJtag 的“瑞士军刀”允许用户完全绕过 IR/DR 抽象层直接操控 TAP 状态机。其典型应用场景包括状态机路径调试验证 TAP 是否响应预期 TMS 序列非标准寄存器访问访问厂商私有指令对应的 DR时序敏感操作如某些 FPGA 配置要求特定 TMS 序列维持多个周期故障注入测试故意发送错误 TMS 序列观察目标行为。调用示例强制进入 Shift-DR 状态并移位 8-bit 数据标准路径Run-Test/Idle→Select-DR-Scan→Capture-DR→Shift-DR。需 7 个 TCK 周期// TMS 序列0 (idle) → 1 (select-dr) → 1 (capture) → 0 (shift) → 0 → 0 → 0 const uint8_t tms_seq[7] {0, 1, 1, 0, 0, 0, 0}; // TDI 序列待发送的 8-bit 数据此处为 0x55 const uint8_t tdi_seq[7] {1, 0, 1, 0, 1, 0, 1}; // LSB first: 0x55 0b01010101 uint8_t tdo_seq[7]; JTAG::ERROR err jtag.sequence(7, tms_seq, tdi_seq, tdo_seq); if (err JTAG::OK) { // tdo_seq[0] 对应 Capture-DR 采样tdo_seq[1..6] 为 Shift-DR 移位结果 }4. 典型应用STM32F407 边界扫描与调试 TAP 交互4.1 硬件连接与初始化以 Arduino Mega25605V 逻辑连接 STM32F407VGT63.3V 逻辑为例需添加双向电平转换电路Arduino PinSignalLevel ShiftSTM32 PinNotes22TCKTXB0104 A1→B1PA15SWDCLK/JNTRST23TMSTXB0104 A2→B2PA13SWDIO/JTMS24TDITXB0104 A3→B3PA14SWDIO/JTCK (Note: TDI shared with JTCK on some packages)25TDOTXB0104 B4→A4PB3JTDI (or PA15 if remapped)初始化代码#include Jtag.hpp Jtag jtag(22, 23, 24, 25); // TCK, TMS, TDI, TDO void setup() { Serial.begin(115200); jtag.begin(); // 执行 TAP 复位 delay(100); }4.2 读取 BoundaryScan TAP 的 IDCODEBoundaryScan TAP 的 IR 长度为 5-bitIDCODE 指令码为0x010b00001。由于是单 TAP直接写入void readBS_IDCODE() { // 1. 写入 IDCODE 指令到 IR jtag.ir(0x01, 5); // instruction0x01, length5 // 2. 读取 32-bit IDCODE 从 DR uint8_t tx[4] {0}; // 发送 32 个 0 uint8_t rx[4]; jtag.dr(tx, 32, rx); // 3. 将 LSB-first 缓冲区转换为 32-bit 整数 uint32_t idcode (rx[0]) | (rx[1] 8) | (rx[2] 16) | (rx[3] 24); Serial.printf(BoundaryScan IDCODE: 0x%08lX\n, idcode); }4.3 读取 Debug TAP 的 IDCODE双 TAP 链如前所述需向串联链写入BYPASSBoundaryScanIDCODEDebug指令0x1FE9-bit再读取 32-bitvoid readDebug_IDCODE() { // 1. 写入复合 IRBoundaryScan(BYPASS0x1F) Debug(IDCODE0x0E) 0x1FE (9-bit) jtag.ir(0x1FE, 9); // 2. 读取 32-bit Debug IDCODE uint8_t tx[4] {0}; uint8_t rx[4]; jtag.dr(tx, 32, rx); uint32_t idcode (rx[0]) | (rx[1] 8) | (rx[2] 16) | (rx[3] 24); Serial.printf(Debug IDCODE: 0x%08lX\n, idcode); }4.4 使用 sequence() 验证 TAP 状态机以下代码验证从Run-Test/Idle进入Shift-IR的标准路径TMS 00001void test_shift_ir_path() { // 当前应在 Run-Test/Idle由 begin() 确保 // 发送 5-bit TMS 序列0-0-0-0-1 进入 Shift-IR const uint8_t tms_test[5] {0, 0, 0, 0, 1}; const uint8_t tdi_test[5] {0, 0, 0, 0, 0}; // 无关 uint8_t tdo_test[5]; JTAG::ERROR err jtag.sequence(5, tms_test, tdi_test, tdo_test); if (err JTAG::OK) { Serial.println(Successfully entered Shift-IR state.); } else { Serial.println(Failed to enter Shift-IR.); } }5. 性能优化与高级配置5.1 TCK 时钟速度调优TCK 速度由宏JTAG_TCK_DELAY_US控制默认值在Jtag.hpp中定义为1即 1 μs理论最高 500 kHz。用户可根据目标器件手册修改// 在 #include Jtag.hpp 前定义 #define JTAG_TCK_DELAY_US 2 // 降低至 250 kHz提高稳定性 #include Jtag.hpp实测性能参考Arduino Mega2560 16 MHzJTAG_TCK_DELAY_US理论 TCK 频率实际可用性适用场景1~500 kHz多数 3.3V 器件稳定协议学习、低速调试2~250 kHz兼容性最佳工业级边界扫描5~100 kHz绝对可靠长线缆、噪声环境5.2 与 FreeRTOS 的协同使用在 RTOS 环境下需确保 JTAG 操作的原子性。推荐方案为将 JTAG 操作封装为独立任务使用vTaskSuspendAll()/xTaskResumeAll()禁用调度器或在Jtag类中添加noInterrupts()/interrupts()保护适用于 AVR对于 ESP32使用portENTER_CRITICAL()/portEXIT_CRITICAL()。// FreeRTOS 任务示例 void jtag_task(void *pvParameters) { Jtag jtag(22, 23, 24, 25); jtag.begin(); while (1) { vTaskSuspendAll(); // 禁用调度 jtag.ir(0x01, 5); uint8_t rx[4]; jtag.dr(nullptr, 32, rx); xTaskResumeAll(); // 恢复调度 vTaskDelay(pdMS_TO_TICKS(100)); } }6. 限制与工程注意事项不支持 JTAG 链动态发现库要求用户预先知晓 TAP 数量、IR 长度及链路顺序无自动BYPASS扫描功能无错误校验机制dr()不验证 TDO 返回值是否符合预期需用户自行比对如 IDCODE 校验无 SWD 协议支持尽管部分引脚复用但 ArduJtag 仅实现纯 JTAG 模式不兼容 ARM Serial Wire DebugArduino Due/ESP32 兼容性DueARM Cortex-M3需修改底层 GPIO 操作为PIO寄存器ESP32 需替换为gpio_set_level()官方未提供需用户自行适配电源域隔离务必确保 Arduino 与目标板共地且电平转换器供电来自目标板 VCC避免反向电流损坏。7. 源码结构与可扩展性分析ArduJtag 源码结构极简核心文件为Jtag.hpp与Jtag.cppJtag.hpp声明类、枚举JTAG::ERROR、宏定义Jtag.cpp实现begin()、ir()、dr()、sequence()其中sequence()是所有操作的底层引擎ir()与dr()均为其封装。可扩展方向添加scan_chain_tap_count()方法通过发送全1IR 并统计 TDO 响应位数自动探测链上 TAP 数量集成idcode_lookup()表内置常见器件 IDCODE 数据库自动识别芯片型号支持SAMPLE/PRELOAD指令扩展边界扫描测试能力实现引脚电平强制与捕获PlatformIO 自动引脚映射利用platformio.ini中的board_build.f_cpu自动选择最优时序策略。该库的价值正在于其“裸露”的实现方式——每一行代码都在诉说 JTAG 协议的本质时钟、状态、数据。当工程师亲手用sequence()驱动出第一个正确的 IDCODE他所掌握的已不仅是 Arduino 引脚而是整个数字世界的测试入口。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2439870.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

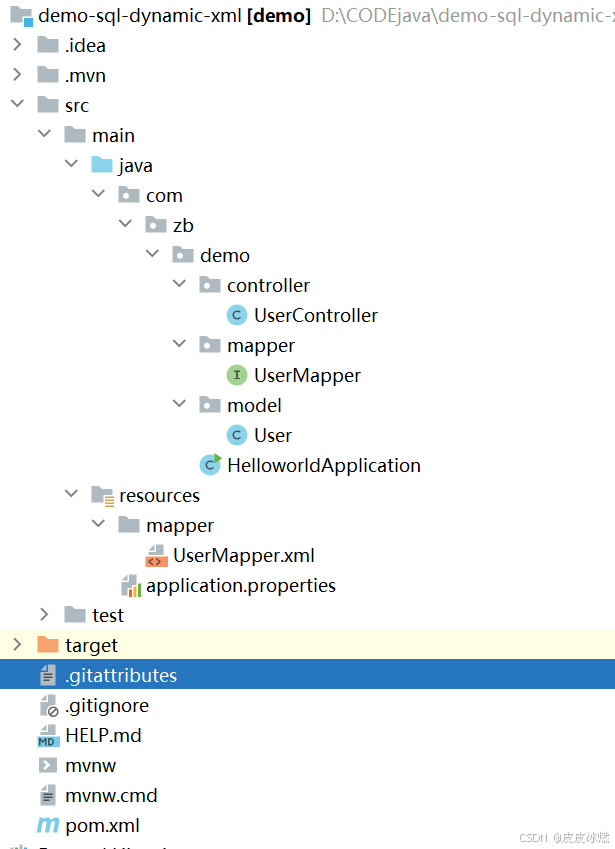

SpringBoot-17-MyBatis动态SQL标签之常用标签

文章目录 1 代码1.1 实体User.java1.2 接口UserMapper.java1.3 映射UserMapper.xml1.3.1 标签if1.3.2 标签if和where1.3.3 标签choose和when和otherwise1.4 UserController.java2 常用动态SQL标签2.1 标签set2.1.1 UserMapper.java2.1.2 UserMapper.xml2.1.3 UserController.ja…

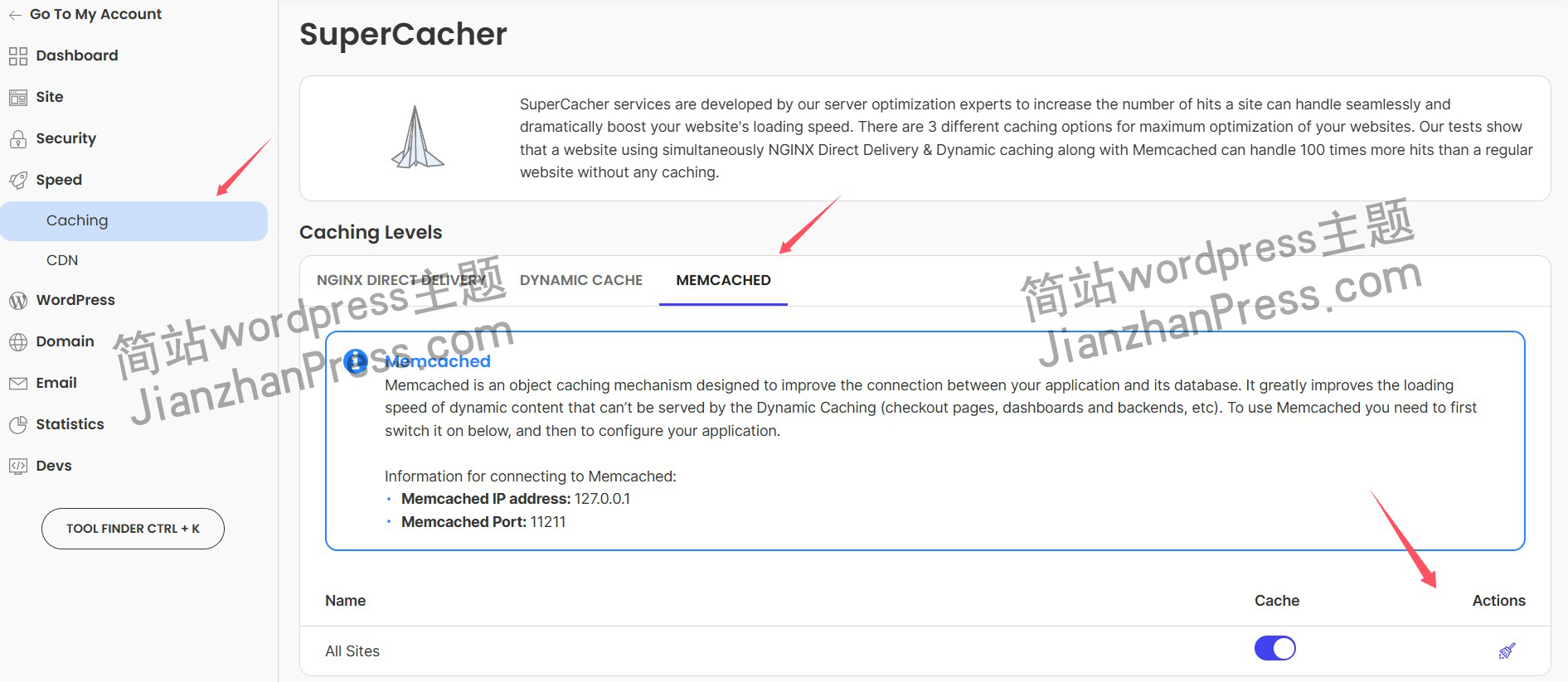

wordpress后台更新后 前端没变化的解决方法

使用siteground主机的wordpress网站,会出现更新了网站内容和修改了php模板文件、js文件、css文件、图片文件后,网站没有变化的情况。

不熟悉siteground主机的新手,遇到这个问题,就很抓狂,明明是哪都没操作错误&#x…

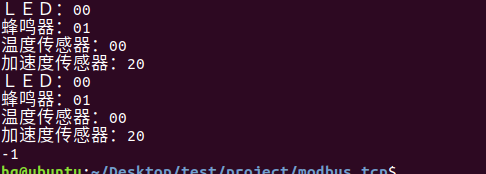

网络编程(Modbus进阶)

思维导图 Modbus RTU(先学一点理论)

概念 Modbus RTU 是工业自动化领域 最广泛应用的串行通信协议,由 Modicon 公司(现施耐德电气)于 1979 年推出。它以 高效率、强健性、易实现的特点成为工业控制系统的通信标准。 包…

UE5 学习系列(二)用户操作界面及介绍

这篇博客是 UE5 学习系列博客的第二篇,在第一篇的基础上展开这篇内容。博客参考的 B 站视频资料和第一篇的链接如下:

【Note】:如果你已经完成安装等操作,可以只执行第一篇博客中 2. 新建一个空白游戏项目 章节操作,重…

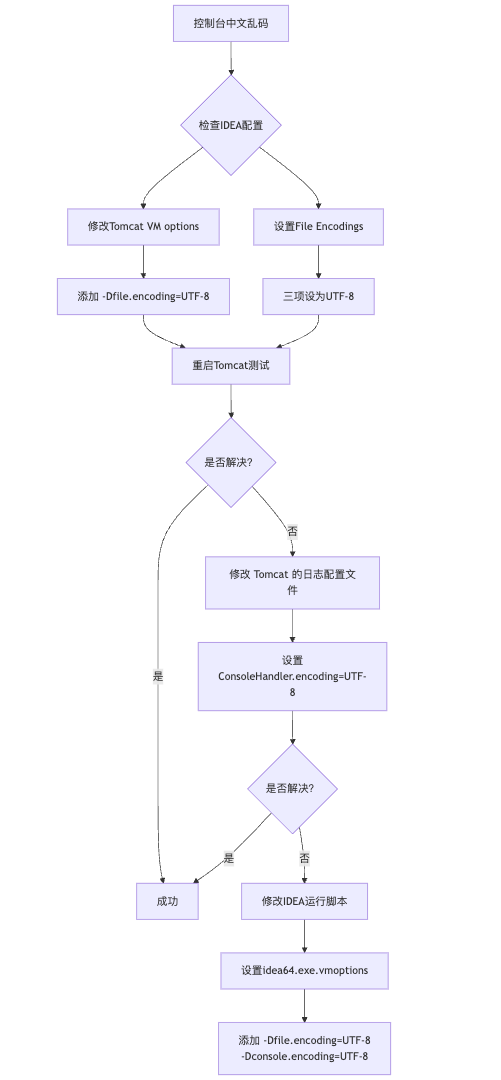

IDEA运行Tomcat出现乱码问题解决汇总

最近正值期末周,有很多同学在写期末Java web作业时,运行tomcat出现乱码问题,经过多次解决与研究,我做了如下整理:

原因:

IDEA本身编码与tomcat的编码与Windows编码不同导致,Windows 系统控制台…

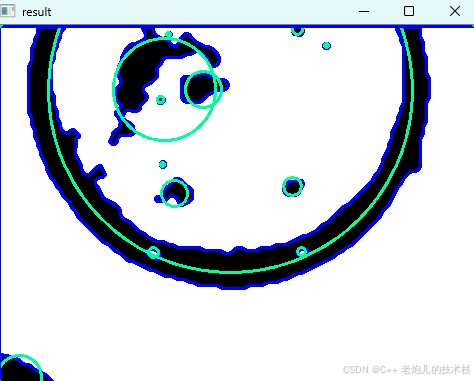

利用最小二乘法找圆心和半径

#include <iostream>

#include <vector>

#include <cmath>

#include <Eigen/Dense> // 需安装Eigen库用于矩阵运算 // 定义点结构

struct Point { double x, y; Point(double x_, double y_) : x(x_), y(y_) {}

}; // 最小二乘法求圆心和半径 …

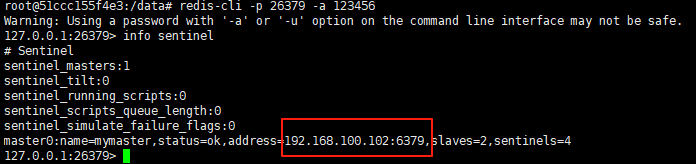

使用docker在3台服务器上搭建基于redis 6.x的一主两从三台均是哨兵模式

一、环境及版本说明

如果服务器已经安装了docker,则忽略此步骤,如果没有安装,则可以按照一下方式安装: 1. 在线安装(有互联网环境): 请看我这篇文章 传送阵>> 点我查看 2. 离线安装(内网环境):请看我这篇文章 传送阵>> 点我查看

说明:假设每台服务器已…

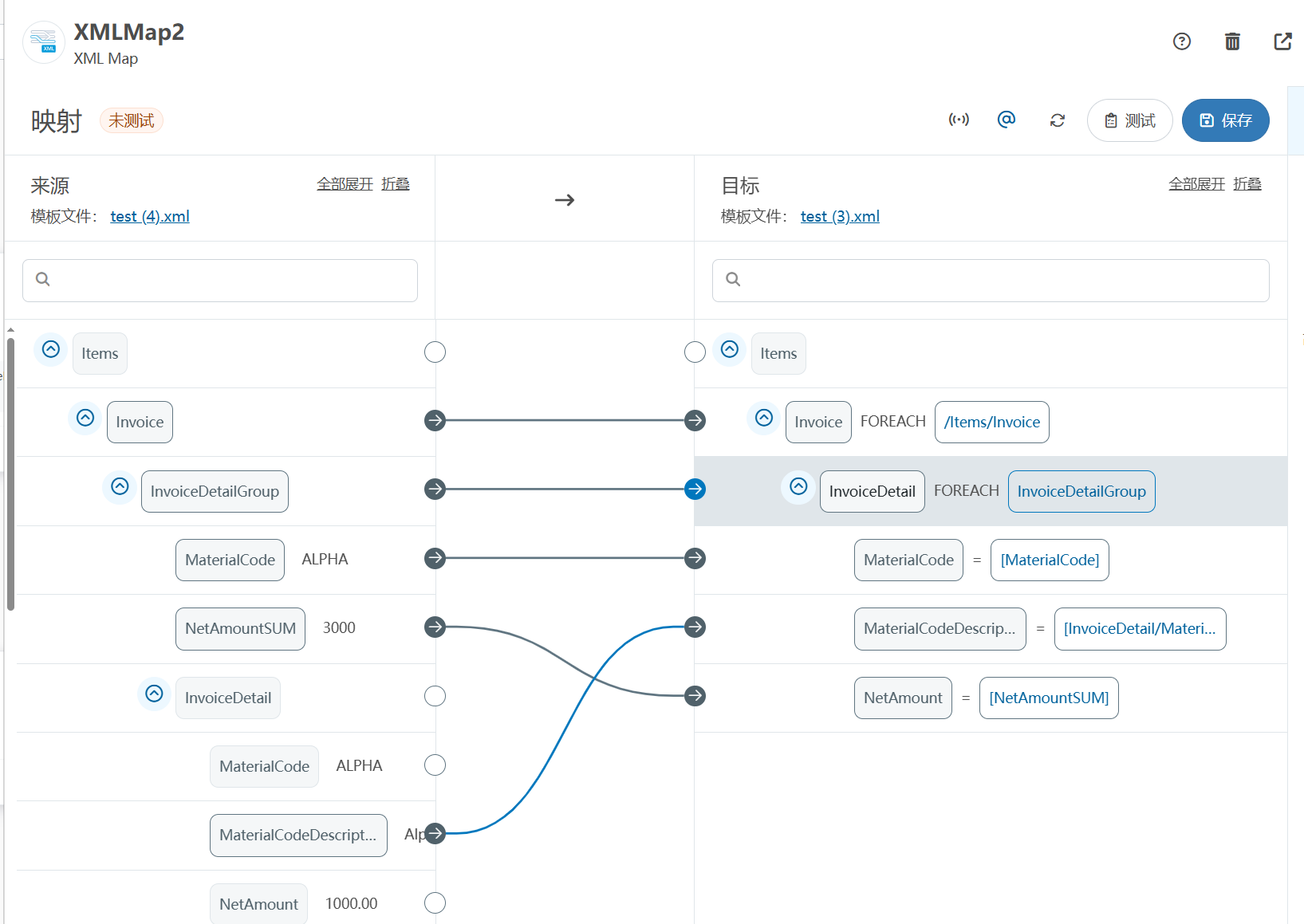

XML Group端口详解

在XML数据映射过程中,经常需要对数据进行分组聚合操作。例如,当处理包含多个物料明细的XML文件时,可能需要将相同物料号的明细归为一组,或对相同物料号的数量进行求和计算。传统实现方式通常需要编写脚本代码,增加了开…

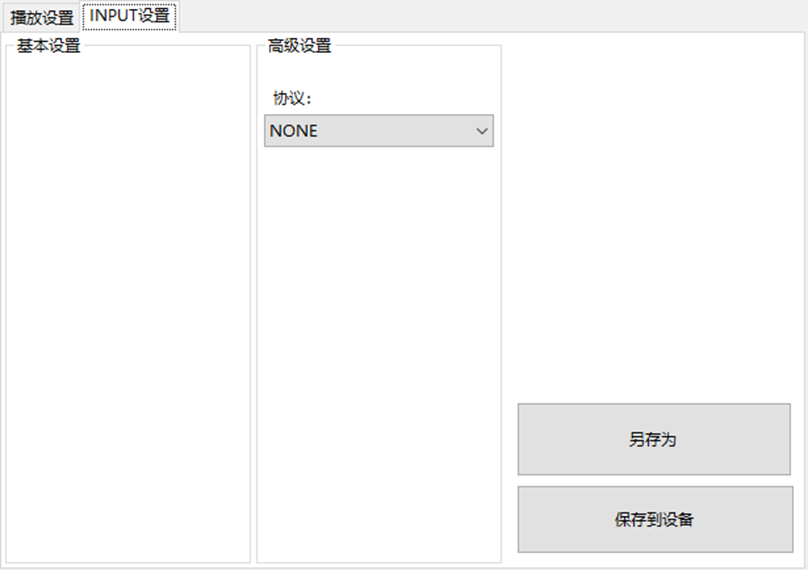

LBE-LEX系列工业语音播放器|预警播报器|喇叭蜂鸣器的上位机配置操作说明

LBE-LEX系列工业语音播放器|预警播报器|喇叭蜂鸣器专为工业环境精心打造,完美适配AGV和无人叉车。同时,集成以太网与语音合成技术,为各类高级系统(如MES、调度系统、库位管理、立库等)提供高效便捷的语音交互体验。

L…

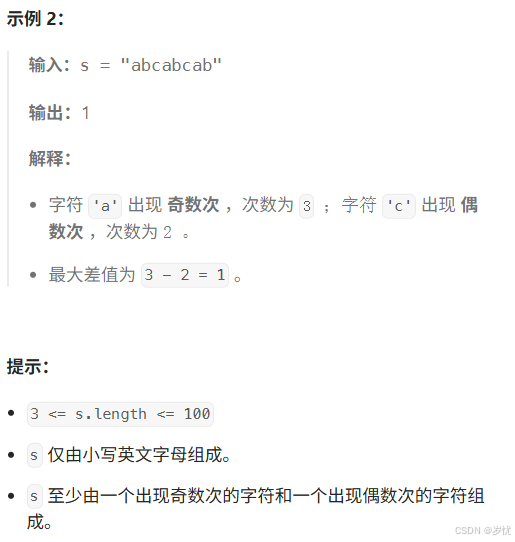

(LeetCode 每日一题) 3442. 奇偶频次间的最大差值 I (哈希、字符串)

题目:3442. 奇偶频次间的最大差值 I 思路 :哈希,时间复杂度0(n)。 用哈希表来记录每个字符串中字符的分布情况,哈希表这里用数组即可实现。

C版本:

class Solution {

public:int maxDifference(string s) {int a[26]…

【大模型RAG】拍照搜题技术架构速览:三层管道、两级检索、兜底大模型

摘要

拍照搜题系统采用“三层管道(多模态 OCR → 语义检索 → 答案渲染)、两级检索(倒排 BM25 向量 HNSW)并以大语言模型兜底”的整体框架: 多模态 OCR 层 将题目图片经过超分、去噪、倾斜校正后,分别用…

【Axure高保真原型】引导弹窗

今天和大家中分享引导弹窗的原型模板,载入页面后,会显示引导弹窗,适用于引导用户使用页面,点击完成后,会显示下一个引导弹窗,直至最后一个引导弹窗完成后进入首页。具体效果可以点击下方视频观看或打开下方…

接口测试中缓存处理策略

在接口测试中,缓存处理策略是一个关键环节,直接影响测试结果的准确性和可靠性。合理的缓存处理策略能够确保测试环境的一致性,避免因缓存数据导致的测试偏差。以下是接口测试中常见的缓存处理策略及其详细说明:

一、缓存处理的核…

龙虎榜——20250610

上证指数放量收阴线,个股多数下跌,盘中受消息影响大幅波动。 深证指数放量收阴线形成顶分型,指数短线有调整的需求,大概需要一两天。 2025年6月10日龙虎榜行业方向分析 1. 金融科技

代表标的:御银股份、雄帝科技

驱动…

观成科技:隐蔽隧道工具Ligolo-ng加密流量分析

1.工具介绍

Ligolo-ng是一款由go编写的高效隧道工具,该工具基于TUN接口实现其功能,利用反向TCP/TLS连接建立一条隐蔽的通信信道,支持使用Let’s Encrypt自动生成证书。Ligolo-ng的通信隐蔽性体现在其支持多种连接方式,适应复杂网…

铭豹扩展坞 USB转网口 突然无法识别解决方法

当 USB 转网口扩展坞在一台笔记本上无法识别,但在其他电脑上正常工作时,问题通常出在笔记本自身或其与扩展坞的兼容性上。以下是系统化的定位思路和排查步骤,帮助你快速找到故障原因:

背景:

一个M-pard(铭豹)扩展坞的网卡突然无法识别了,扩展出来的三个USB接口正常。…

未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?

编辑:陈萍萍的公主一点人工一点智能 未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?RWM通过双自回归机制有效解决了复合误差、部分可观测性和随机动力学等关键挑战,在不依赖领域特定归纳偏见的条件下实现了卓越的预测准…

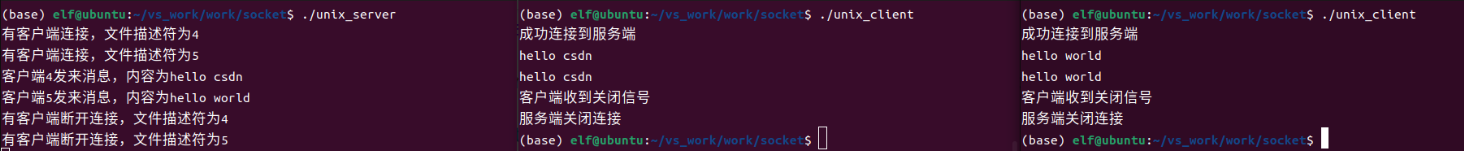

Linux应用开发之网络套接字编程(实例篇)

服务端与客户端单连接

服务端代码

#include <sys/socket.h>

#include <sys/types.h>

#include <netinet/in.h>

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <arpa/inet.h>

#include <pthread.h>

…

华为云AI开发平台ModelArts

华为云ModelArts:重塑AI开发流程的“智能引擎”与“创新加速器”!

在人工智能浪潮席卷全球的2025年,企业拥抱AI的意愿空前高涨,但技术门槛高、流程复杂、资源投入巨大的现实,却让许多创新构想止步于实验室。数据科学家…

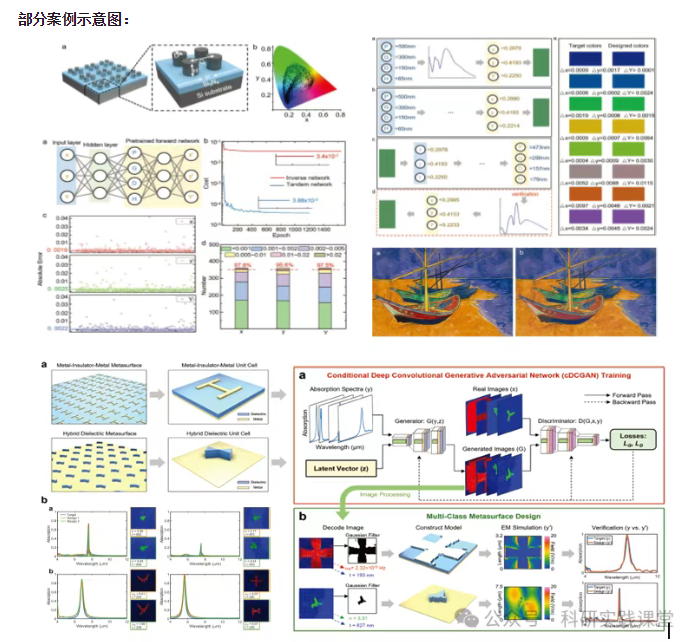

深度学习在微纳光子学中的应用

深度学习在微纳光子学中的主要应用方向

深度学习与微纳光子学的结合主要集中在以下几个方向:

逆向设计 通过神经网络快速预测微纳结构的光学响应,替代传统耗时的数值模拟方法。例如设计超表面、光子晶体等结构。

特征提取与优化 从复杂的光学数据中自…