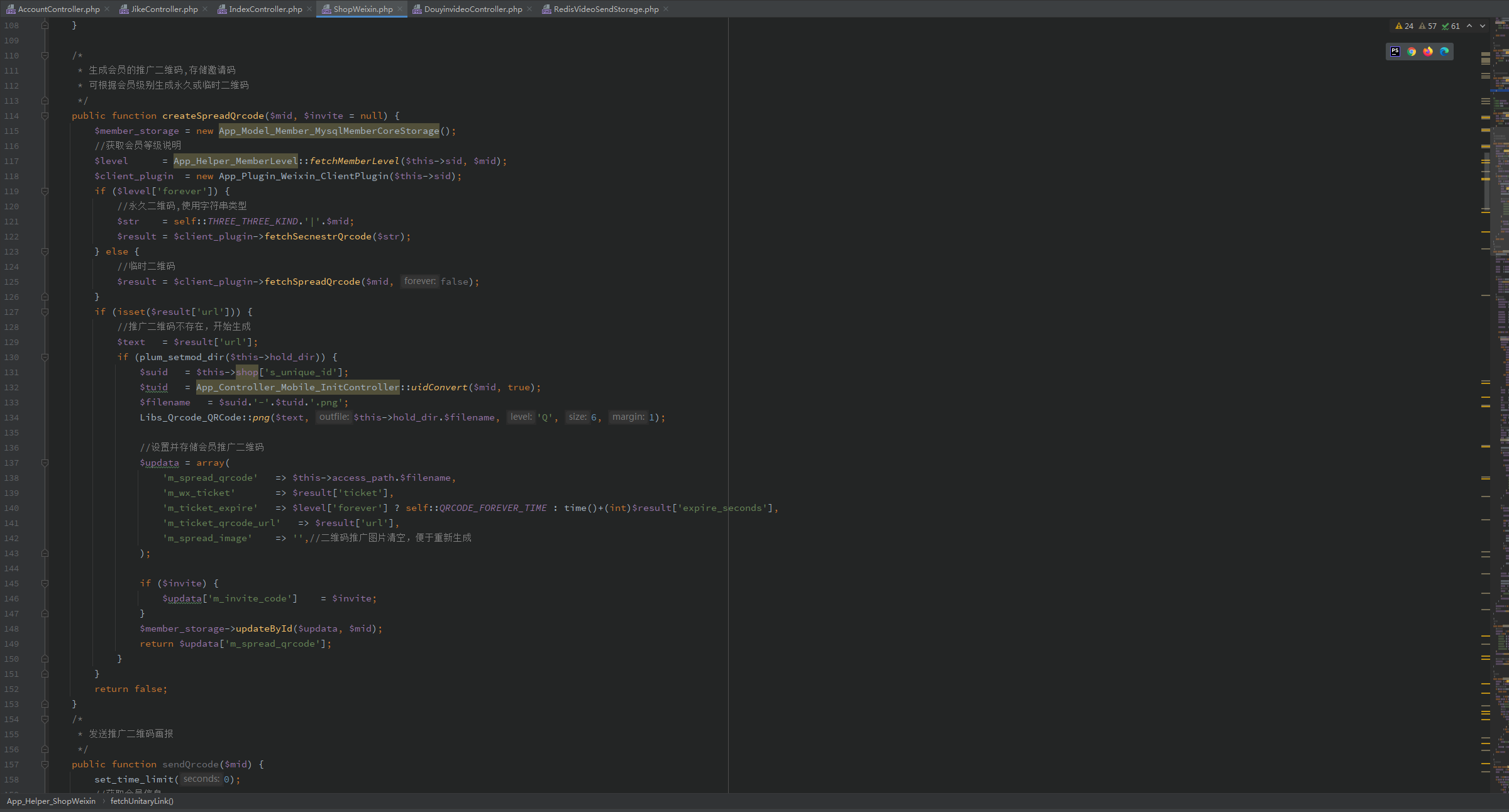

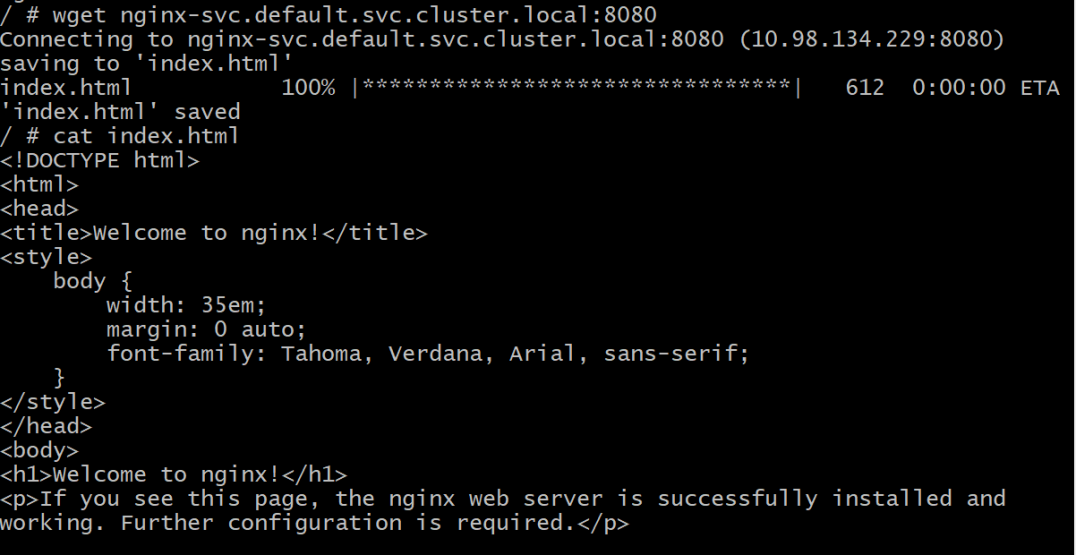

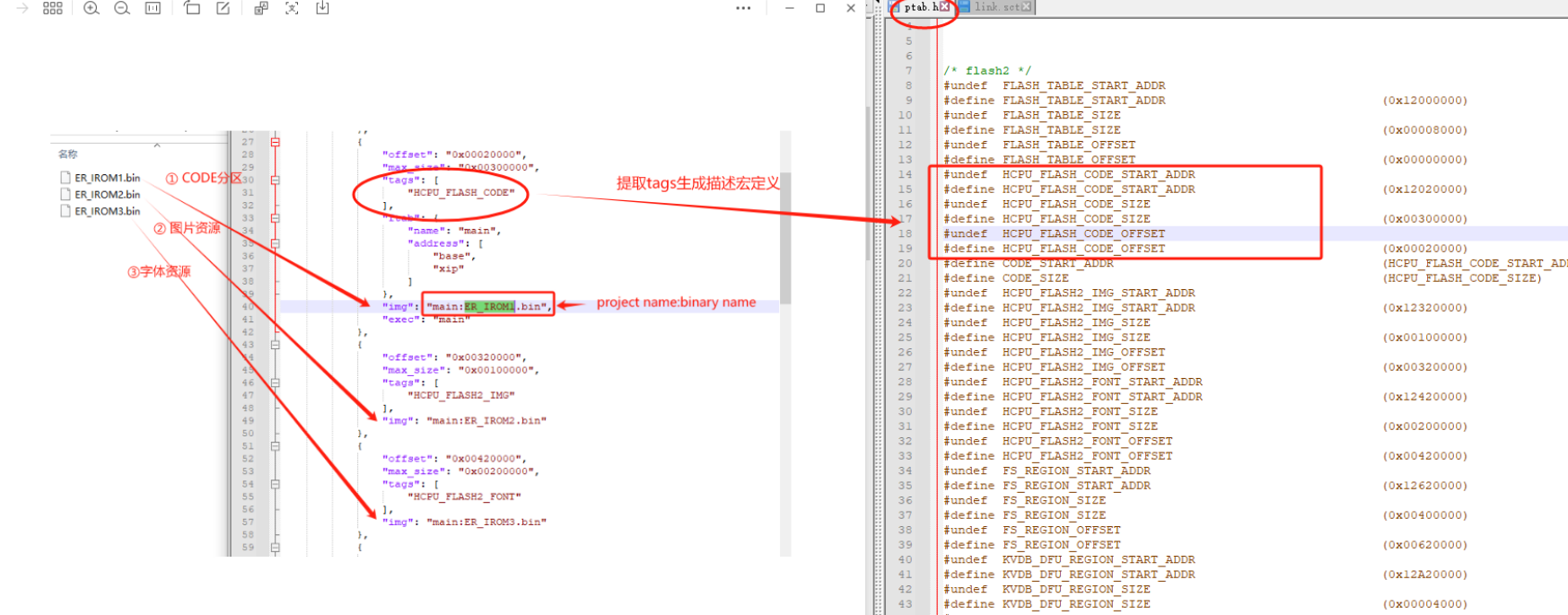

分区配置

(ptab.json)

img

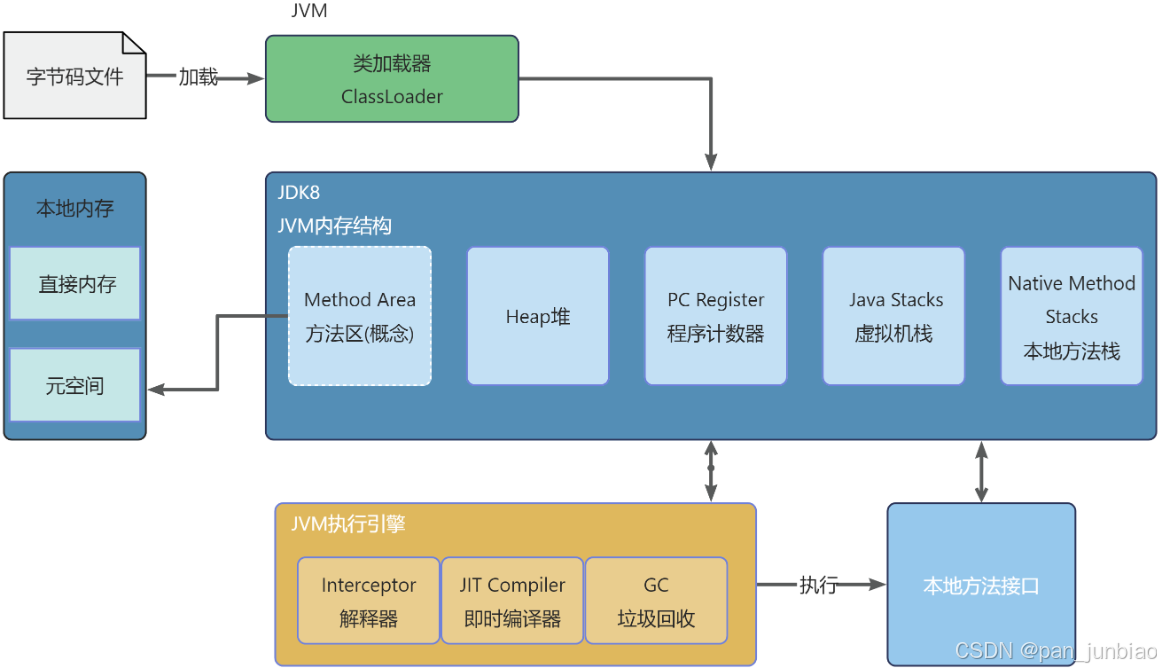

属性介绍:

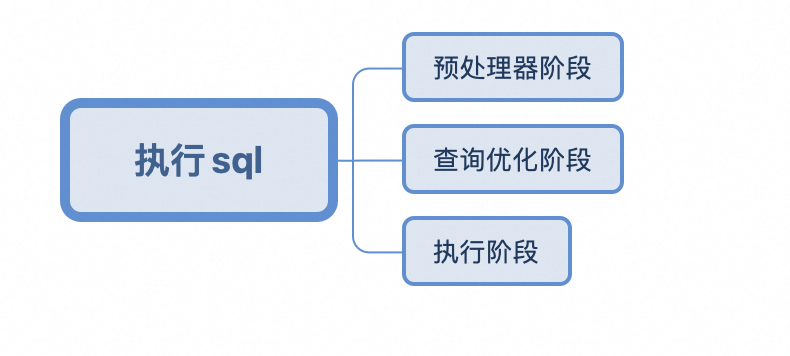

img

属性指定分区存放的

image

名称,指定的

image

名称必须是当前工程生成的

binary

。

如果

binary

有多个文件,则以

proj_name:binary_name

格式指定文件名,

proj_name

为工程

名,主工程为

main

,子工程则与编译脚本配置的名称一致,比如

acpu

作为子工程加入编译,

子工程名为

acpu

,生成了两个

binary

文件分别为

ER_IROM1.bin

和

ER_IROM2.bin

,可以用

acpu:ER_IROM1.bin

表示

ACPU

编译生成的

ER_IROM1.bin

文件。

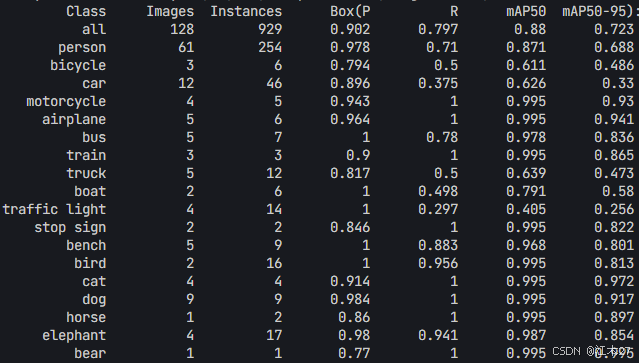

ftab

属性介绍:

ftab

属性用于描述

flash

分区表,即该分区与

flash table

中哪个条目相关联,以此生成

flash

table

的描述文件

ftab.c

。

ftab

包含以下属性:

- name

:名称,

main

和

bootloader

为系统预留,分别表示主程序和二级

bootloader

(

二

者是系统预留的名称,不能随便使用,除此以外的名字可以由用户随意指定,如

acpu_region1

可以用来表示

ACPU

的代码分区

)。

- address

:地址类型列表,如果分区起始地址是

image

的

base

地址,则填写

”base”

,如果分

区起始地址为

image

的

xip

地址(即执行地址),则填写

”xip”

,如果两者都是(即不需要搬移

代码到

xip

地址执行),则需要同时填写

”base”

和

”xip”

。

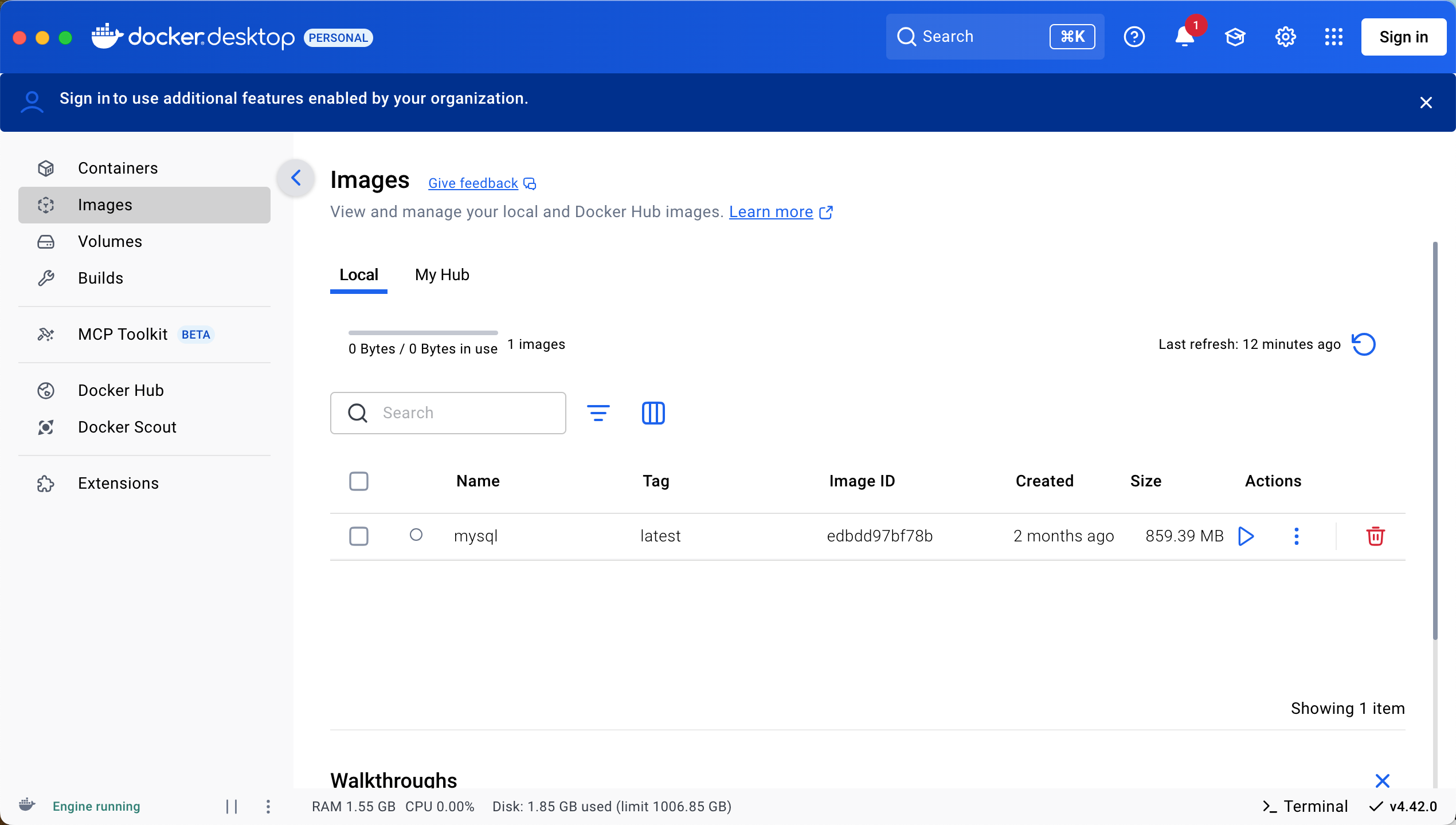

以

\example\multimedia\lvgl\watch\project\sf32lb52-lcd_n16r8_hcpu

例程为例,主工程要生成

3

个

binary

,分别为:

ER_IROM1.bin ---

用于

CODE

,

img

属性为:

main:ER_IROM1.bin

;带

ftab

属性。

ER_IROM2.bin ---

用于图片资源,

img

属性为:

main:ER_IROM2.bin

ER_IROM3.bin ---

用于字体资源,

img属性为: main:ER_IROM3.bin

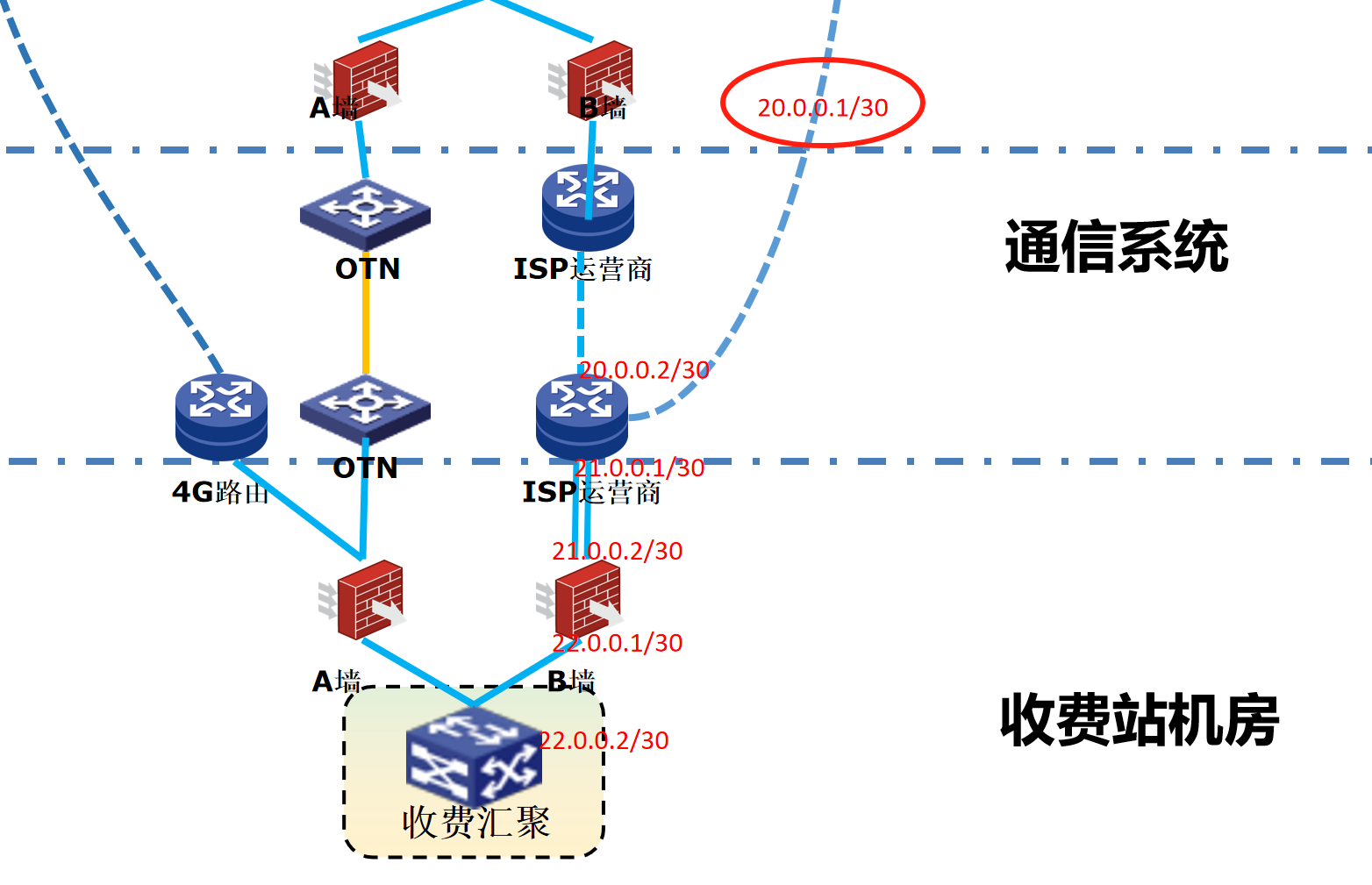

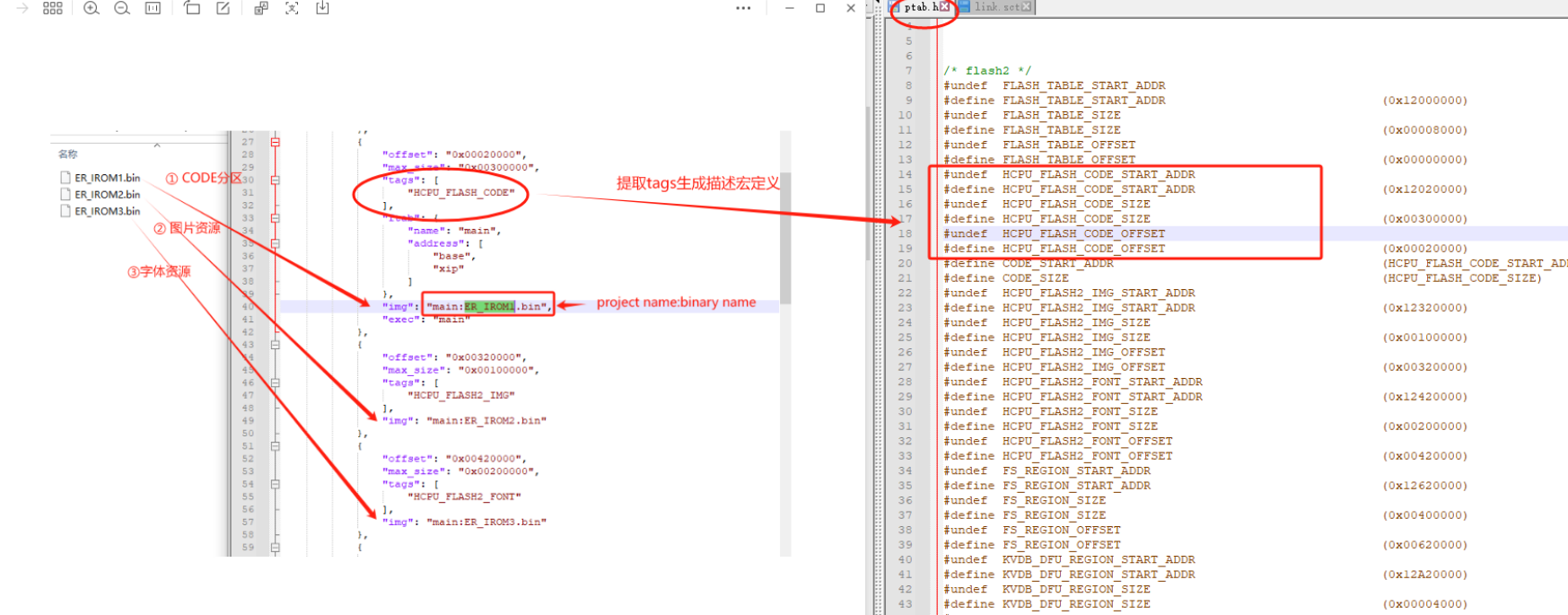

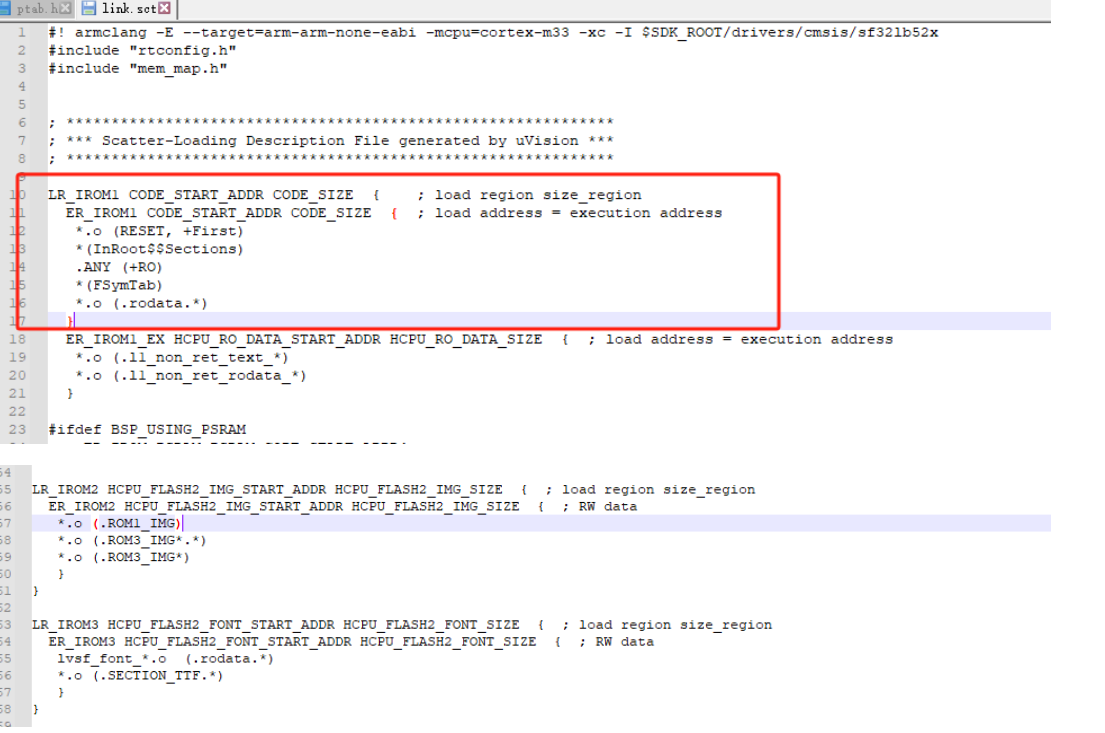

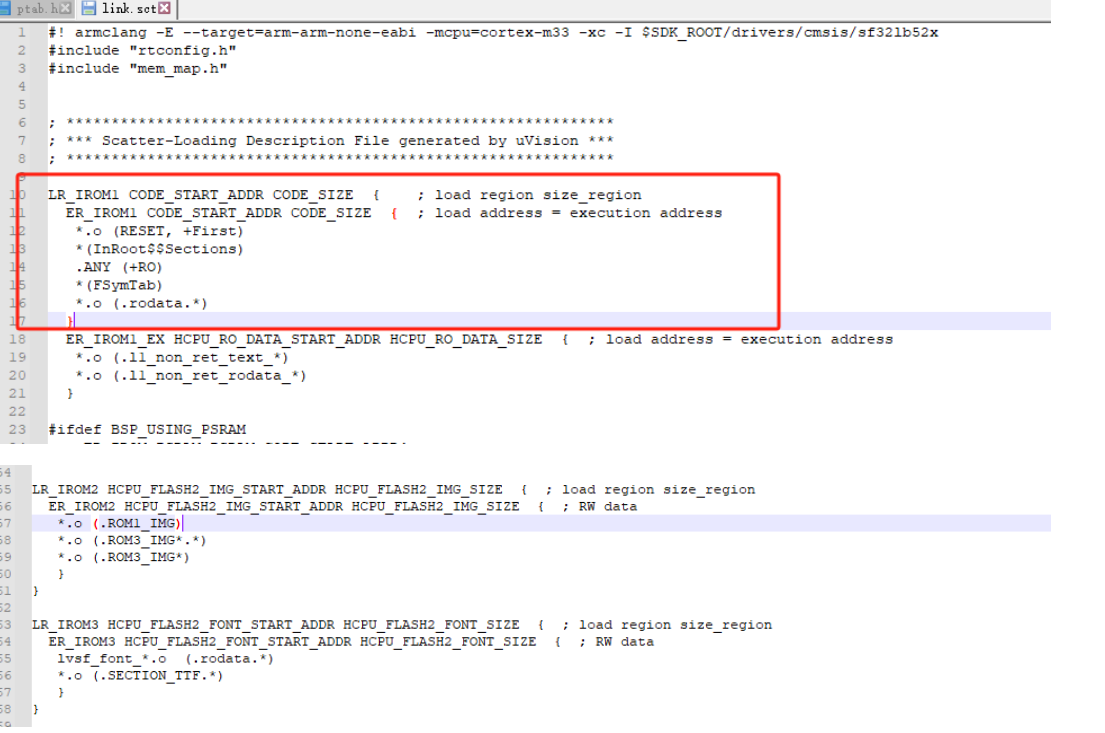

链接脚本配置(

.sct/.ld

)

以

\example\multimedia\lvgl\watch\project\sf32lb52-lcd_n16r8_hcpu

例程为例:

生成

3

个

binary

(

ER_IROM1.bin

、

ER_IROM2.bin

、

ER_IROM3.bin

)。

域起始地址、大小在

ptab.h

(提取ptab.json生成)中定义。

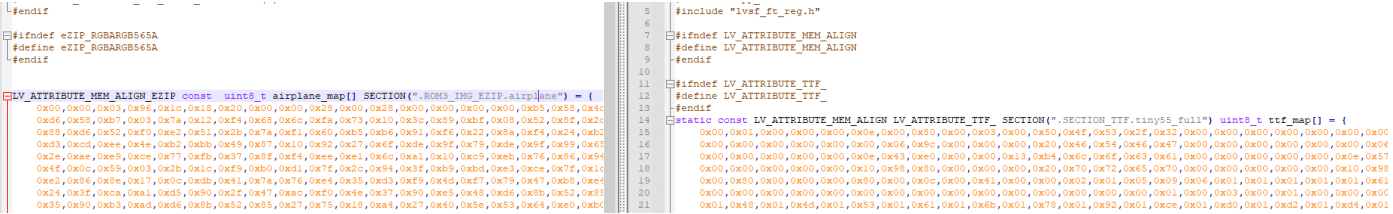

ER_IROM2

域、

ER_IROM3

域分别存放图片资源和字体资源,例程中以图片资源和字体资源的

段名指定(可根据需要自定义规则)。

GCC环境下.ld同理配置。

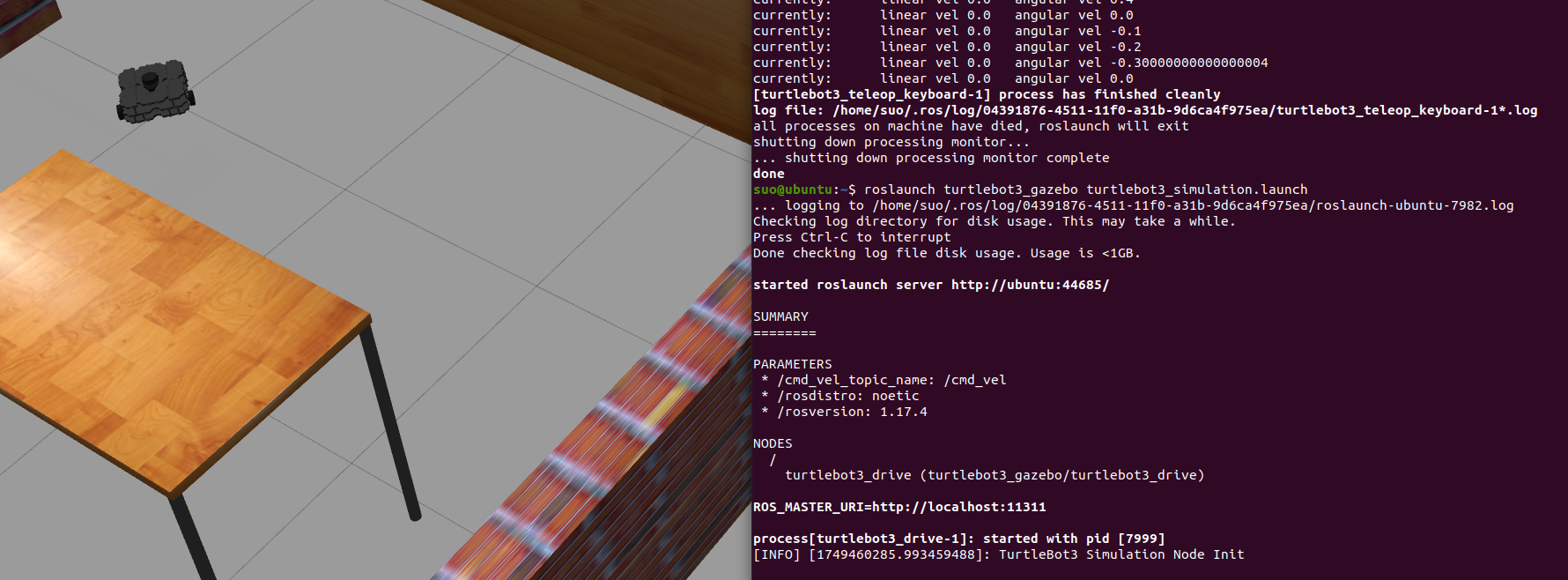

[

{

"mem": "flash2",

"base": "0x12000000",

"regions": [

{

"offset": "0x00000000",

"max_size": "0x00008000",

"tags": [

"FLASH_TABLE"

],

"img": "ftab",

"exec": "ftab"

},

{

"offset": "0x00010000",

"max_size": "0x00010000",

"tags": [],

"ftab": {

"name": "bootloader",

"address": [

"base"

]

},

"img": "bootloader"

},

{

"offset": "0x00020000",

"max_size": "0x00300000",

"tags": [

"HCPU_FLASH_CODE"

],

"ftab": {

"name": "main",

"address": [

"base",

"xip"

]

},

"img": "main:ER_IROM1.bin",

"exec": "main"

},

{

"offset": "0x00320000",

"max_size": "0x00100000",

"tags": [

"HCPU_FLASH2_IMG"

],

"img": "main:ER_IROM2.bin"

},

{

"offset": "0x00420000",

"max_size": "0x00200000",

"tags": [

"HCPU_FLASH2_FONT"

],

"img": "main:ER_IROM3.bin"

},

{

"offset": "0x00620000",

"max_size": "0x00400000",

"img": "fs_root",

"tags": [

"FS_REGION"

]

},

{

"offset": "0x00A20000",

"max_size": "0x00004000",

"tags": [

"KVDB_DFU_REGION"

]

},

{

"offset": "0x00A24000",

"max_size": "0x00004000",

"tags": [

"KVDB_BLE_REGION"

]

}

]

},

{

"mem": "psram1",

"base": "0x60000000",

"regions": [

{

"offset": "0x00000000",

"max_size": "0x00040000",

"tags": [

"PSRAM_CODE"

]

},

{

"offset": "0x00040000",

"max_size": "0x007C0000",

"tags": [

"PSRAM_DATA"

]

}

]

},

{

"mem": "hpsys_ram",

"base": "0x20000000",

"regions": [

{

"offset": "0x00000000",

"max_size": "0x0006BC00",

"tags": [

"HCPU_RAM_DATA"

]

},

{

"offset": "0x00020000",

"max_size": "0x00020000",

"ftab": {

"name": "bootloader",

"address": [

"xip"

]

},

"tags": [

"FLASH_BOOT_LOADER"

],

"exec": "bootloader"

},

{

"offset": "0x00040000",

"max_size": "0x00010000",

"tags": [

"BOOTLOADER_RAM_DATA"

]

},

{

"offset": "0x0006BC00",

"max_size": "0x00014000",

"tags": [

"HCPU_RO_DATA"

]

},

{

"offset": "0x0007FC00",

"max_size": "0x00000400",

"tags": [

"HPSYS_MBOX"

]

},

{

"offset": "0x0007FC00",

"max_size": "0x00000200",

"tags": [

"HCPU2LCPU_MB_CH2_BUF"

]

},

{

"offset": "0x0007FE00",

"max_size": "0x00000200",

"tags": [

"HCPU2LCPU_MB_CH1_BUF"

]

}

]

},

{

"mem": "lpsys_ram",

"base": "0x20400000",

"regions": [

{

"offset": "0x00000000",

"max_size": "0x00006000",

"tags": [

"LPSYS_RAM"

]

}

]

}

]