对FPGA 芯片的配置,本质上是将根据设计生成的包含配置命令和配置数据的比特流文件写入到配置存储器中。

1 配置模式

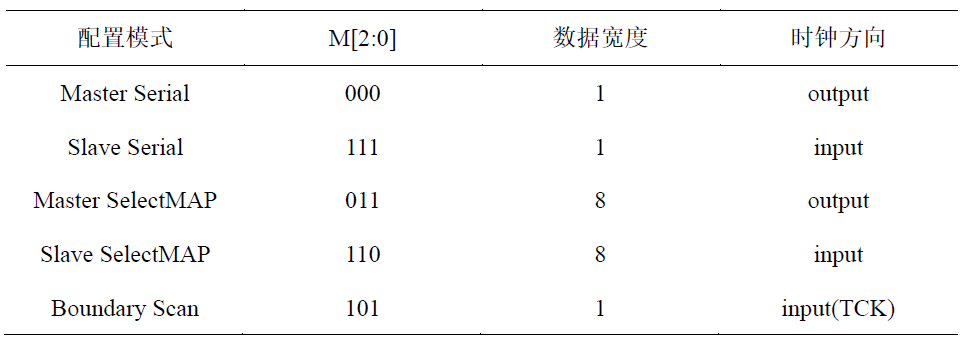

Virtex II 系列FPGA 一共有五种配置模式,配置模式的选择是根据管脚M[2:0]来决定。

(1)串行配置模式

串行配置模式中,数据总线宽度只有1 位。串行配置方式有主串模式和从串模式。主串模式中,时钟由FPGA 提供,PROM 在时钟控制下读取内部存储数据并输出。从串模式中,配置时钟由外部提供,在外部控制器的控制下将配置数据读出并写入FPGA 中。

(2)并行配置模式

Virtex II 系列FPGA 的并行模式,数据总线位宽一共有8 位。数据位宽增加所产生的优点是它的配置速度很快,所以它也是重构技术使用的一种主要模式。它是从Platform Flash PROM 中加载配置数据完成对FPGA 的配置。根据时钟方向,并行配置模式可以分为主模式和从模式两种模式。

(3)边界扫描模式

FPGA 设计有JTAG 口,可以通过测试访问端口完成对FPGA 的配置。这种模式下,接口数据宽度只有1 位,连线简单,但是配置速度慢。

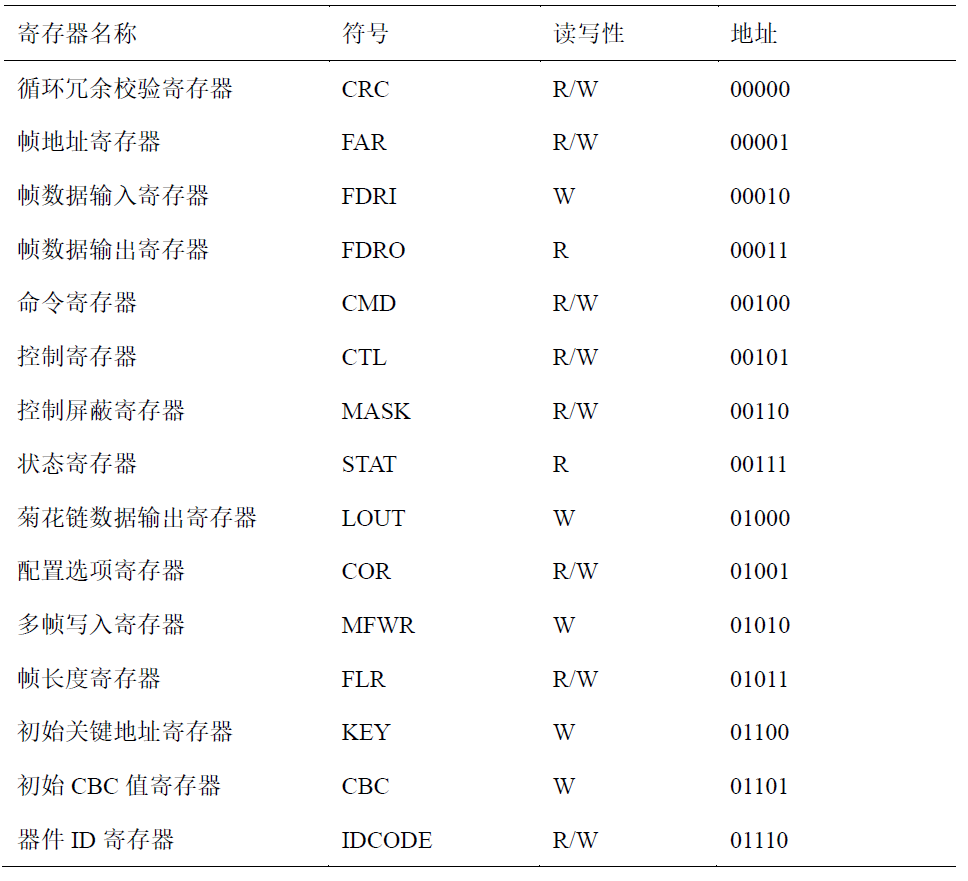

2 FPGA 配置寄存器

Virtex II 系列FPGA 内部一共有15 个32bit 的配置寄存器,每个寄存器对应一个唯一的地址。通过对这15 个配置寄存器的读写操作,完成对FPGA 的配置、回读和刷新操作。配置寄存器的具体情况如下表所示。

(1)CRC 寄存器

CRC 寄存器用来存放配置位流中已经写好的CRC 值。FPGA 会在配置过程中根据输入的配置数据计算其CRC 值,并将写入的CRC 值与计算的得来的CRC值进行比较,若结果不匹配,FPGA 会停止配置转而加载安全文件。

(2)FAR 寄存器

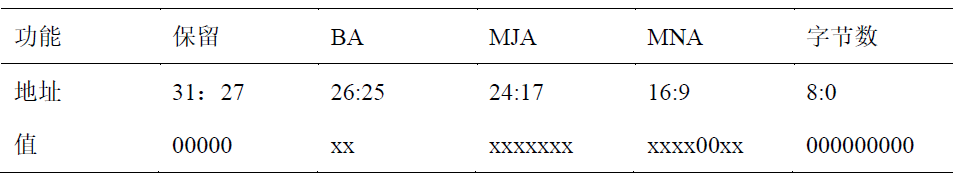

FAR 寄存器是帧地址寄存器,它用来存放配置数据再次输入时需要写入的起始帧的地址。FPGA 进行配置时是以帧为单位进行配置。在FAR 寄存器中,最大的可寻址单位是块,用块地址(BA)来区分,块由多个列组成,用主地址(MJA)来区分,列由多个帧构成,用从地址(MNA)来区分。用块地址、主地址和从地址就可以精确定位到每一个需要配置的帧。

FAR 寄存器的具体构成由下表所示。当需要进行配置和回读多个帧时,帧地址寄存器会自动改变地址。

(3)FDRI 寄存器

帧数据输入寄存器,缓存输入的配置数据。配置数据从数据端口输入先缓存在FDRI 寄存器中,然后以FAR 寄存器指向的地址为起始地址向配置存储器写入配置数据。

(4)FDRO 寄存器

帧数据输出寄存器,缓存回读时的配置数据。在接收到回读命令后,按照FAR寄存器指向的地址读取配置数据,缓存到FDRO 寄存器中输出。

(5)CMD 寄存器

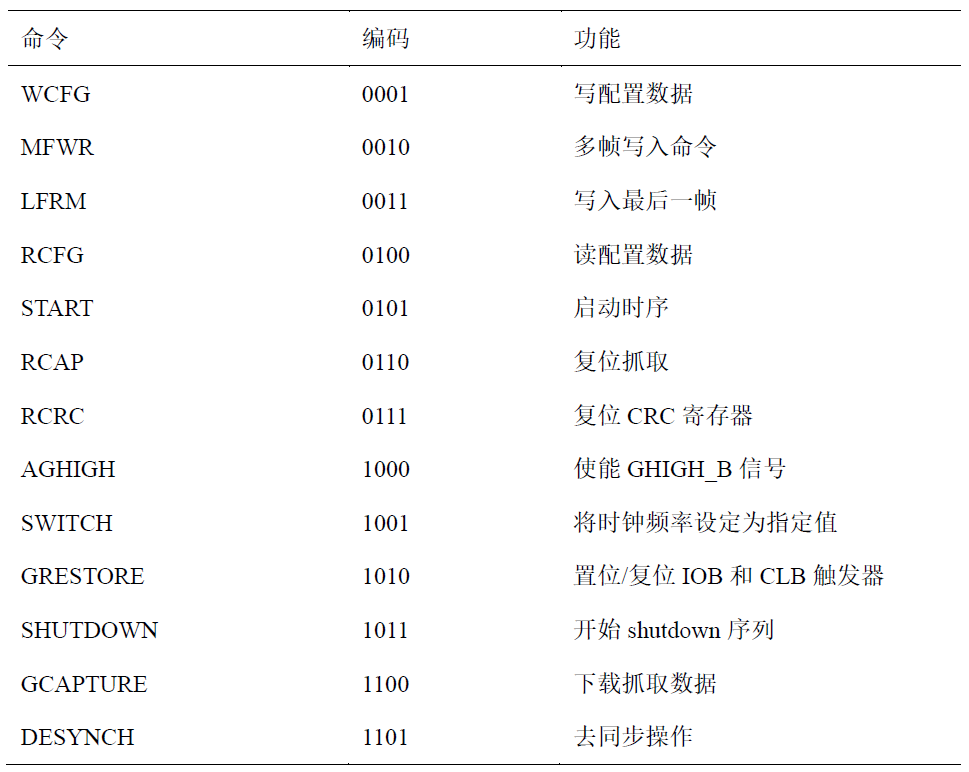

CMD 寄存器是命令寄存器,通过向CMD 寄存器写入数据来执行对应的控制命令。CMD 寄存器用来实现FPGA 所有的配置命令。通过CMD 命令可以控制整个配置过程。具体的配置命令和编码如下表所示。

(6)CTL 寄存器

控制寄存器,配置过程中主要是用来控制配置端口的保留,在回读和刷新操作时需要将配置端口保留下来,不能将其复用。

(7)MASK 寄存器

掩码寄存器,控制CTL 寄存器的写入。新数据要写入的位置必须被MASK寄存器使能后才能写入,否则视为无效。

(8)COR 寄存器

配置选项寄存器,通过其来设置一些配置选项,主要是设置FPGA 配置时钟频率。

(9)FLR 寄存器

帧长寄存器,表示配置逻辑的帧长。

(10)IDCODE 寄存器

ID 寄存器,用来写入配置器件的ID。每种型号的FPGA 都有一个对应的ID。