文章目录

- A1. (并行编程 基于的)硬件环境 的 基本模型

- A2. 特定的硬件实现

- B1. 并行编程基本模型与编程技术

- ✅ 并行编程的一般流程

- **第一阶段:基于“编程直觉模型”设计程序**

- **第二阶段:程序编译并部署到实际硬件**

- B2.特定的 硬件环境下的 并行编程

A1. (并行编程 基于的)硬件环境 的 基本模型

- 缓存一致性

- 内存一致性模型

- 同步原语

Coherence is a key hardware design concept and is a necessary part of our intuitive notion the memory abstraction.

缓存一致性是硬件设计中的一个关键概念,并且是我们对“内存抽象”的直觉理解中不可缺少的一部分。

“Memory abstraction”(内存抽象)指的是:我们希望内存就像一个统一的存储体,不管由谁访问,结果都是一致的。

“Coherence”(一致性)确保这一点在多处理器系统中成立。

However, parallel software often makes stronger assumptions about how memory behaves.

然而,并行软件通常会对内存行为做出更强的假设。

比如程序员可能会假设某个写操作会立即对其他线程可见,或者假设不同线程看到的共享变量更新顺序是一致的——这在现代硬件中未必成立,需要内存模型(即符合哪一种内存一致性模型)来进行约束。

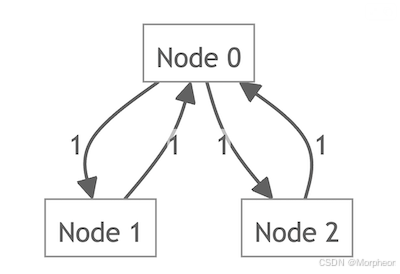

Note that sequential consistency does not obviate the need for synchronization.

SC allows operations from different processes to be interleaved arbitrarily and at the granularity of individual instructions.

Synchronization is needed if we want to preserve atomicity (mutual exclusion) across multiple memory operations from a process, or if we want to enforce certain orders in the interleaving across processes.

顺序一致性只是规定了所有处理器看到的操作顺序,但不会自动保证并发程序中所需的临界区互斥、原子性、同步条件等正确性

因此,仍然需要锁、信号量、屏障等同步手段。

在顺序一致性模型下,来自不同进程的操作可以以单条指令为粒度进行任意交错执行。

如果我们希望在一个进程的多个内存操作之间保持原子性(互斥性),或希望在多个进程之间的操作交错中强制实施某些顺序,就必须使用同步机制。

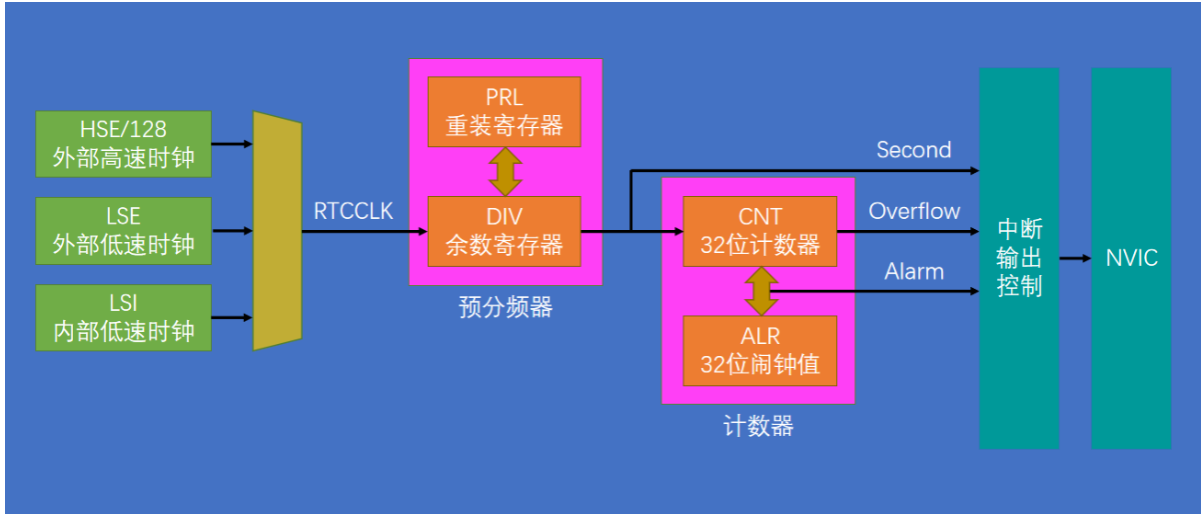

Section 5.6 examines how the low-level synchronization operations make use of the available hardware primitives on cache coherent multiprocessors, and how the algorithms can be tailored to use the machine efficiently.

第 5.6 节将研究低层次同步操作如何利用缓存一致性多处理器所提供的硬件原语(primitives),以及如何对同步算法进行调整以高效利用机器资源。

这句话重点在于:

低层次同步操作:如锁、自旋锁、原子操作(如 compare-and-swap);

硬件原语:指的是架构层面提供的支持同步的功能,比如总线锁、cache invalidation、load-linked/store-conditional 等;

tailored:是指对算法做调整,使它们能更好地“贴合”当前硬件的工作方式,从而获得更好的效率(如减少总线争用、避免伪共享等)。

The latter portions of the chapter examine the implications these cache coherent shared memory architectures have for software that runs on them.

本章后半部分将探讨这些具有缓存一致性(cache coherent)的共享内存架构对其上运行的软件所产生的影响。

这里说的是:“缓存一致性共享内存系统”不仅是硬件问题,还会影响到运行其上的软件设计,尤其是在多线程程序、同步机制和性能优化方面。

A2. 特定的硬件实现

B1. 并行编程基本模型与编程技术

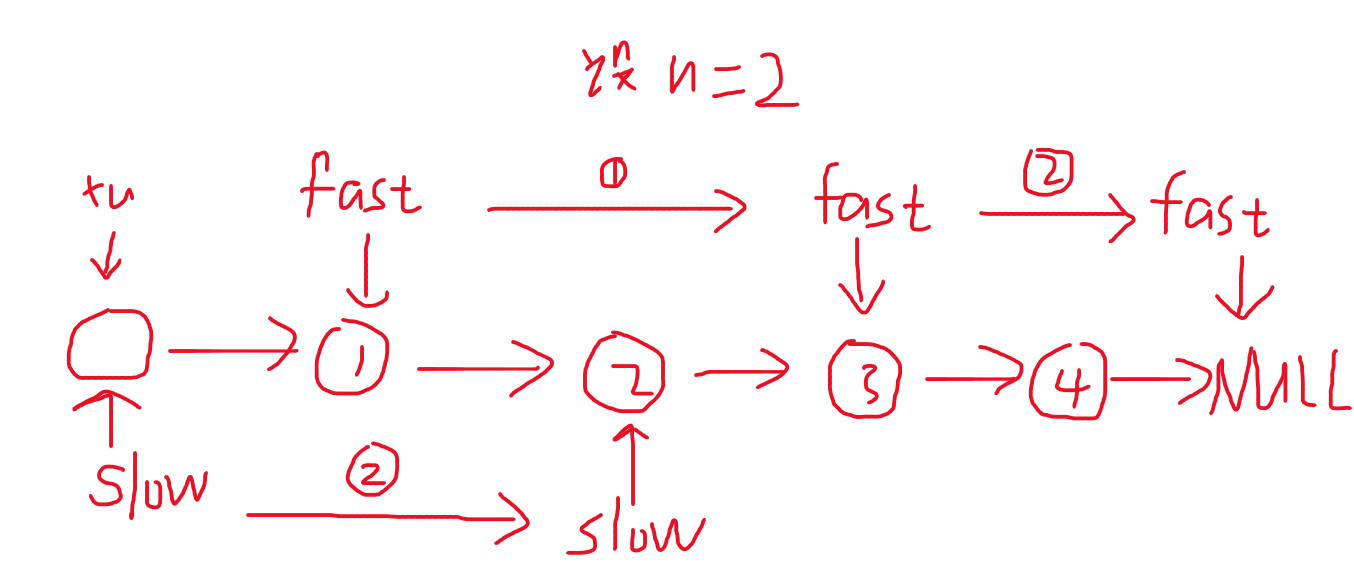

并行编程通常先按编程直觉模型(如 SC)设计与验证逻辑,然后在部署或实现阶段,再通过编译器或硬件机制适配具体平台的内存一致性模型。

✅ 并行编程的一般流程

第一阶段:基于“编程直觉模型”设计程序

- 通常假设 Sequential Consistency(SC):

➤ 所有线程都按程序顺序执行,操作全局统一生效,如同单核系统接力运行。 - 这个阶段开发者聚焦逻辑正确性:

- 判断是否有数据竞争(data race)

- 验证临界区是否加锁

- 思考共享变量访问的可见性与一致性

- 代表工具/语言模型:

- C++/Java 中的 SC-for-DRF(Data-Race-Free 程序视为顺序一致)模型

- OpenMP/Pthreads 的默认语义

- CUDA/OpenCL 中的 thread group sync 机制

第二阶段:程序编译并部署到实际硬件

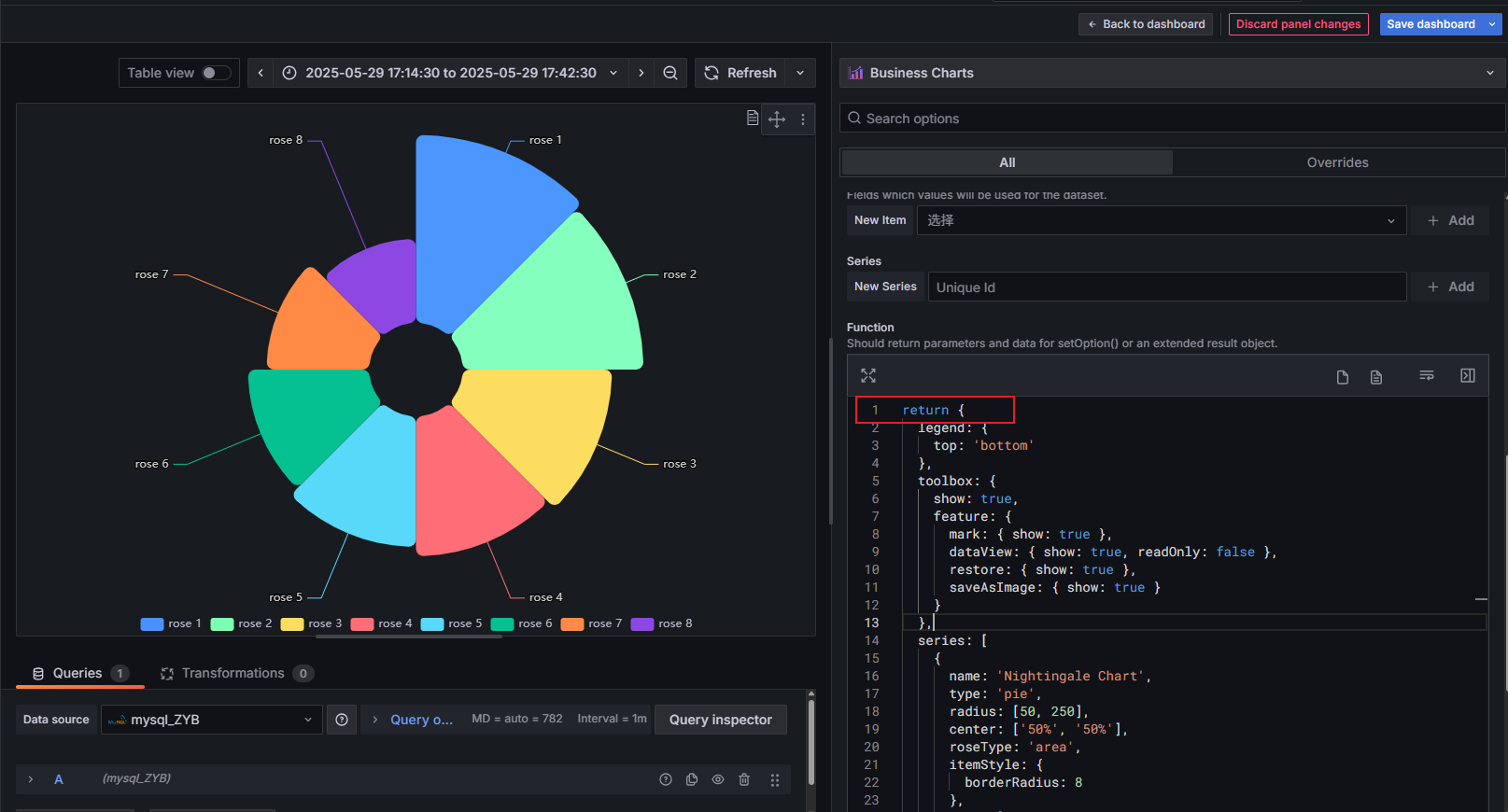

- 此时才要面对实际硬件的内存模型,如:

- x86 的 TSO

- ARM、RISC-V 的 RCsc/RCpc

- GPU 的非常弱一致性模型

- 编译器或程序员需要:

- 插入合适的 memory fences(内存栅栏)

- 使用 atomic 指令 / 原语

- 利用 内存模型相关 API(如

std::memory_order_acquire等)

B2.特定的 硬件环境下的 并行编程

Section 5.7 discusses the implications for parallel programming more generally, putting together our knowledge of parallel programs from Chapters 2 and 3 and of bus-based cache-coherent architecture from this chapter.

第 5.7 节将从更广义的角度探讨这些架构对并行编程的影响,并综合第 2 章和第 3 章关于并行程序的知识,以及本章关于基于总线的缓存一致性架构的内容。

这里将回顾前面章节介绍的 并行程序基本模型与编程技术;

与本章所学的 硬件架构(总线型缓存一致性系统) 结合,进一步分析编程层面会遇到什么样的约束与优化方向。

In particular, it discusses how temporal and spatial data locality may be exploited to reduce cache misses and traffic on the shared bus.

特别地,它会讨论如何利用时间局部性和空间局部性来减少缓存未命中率(cache miss)和共享总线上的数据通信(流量)。

Temporal locality(时间局部性):近期访问的数据未来可能还会被访问(→ 使用缓存可以提高命中率);

Spatial locality(空间局部性):访问一个地址后,很可能会访问邻近地址(→ 利用块式缓存可提高效率);

降低 cache miss 和总线流量 是共享内存并行编程中性能优化的关键目标,尤其是在基于总线的系统中,总线是瓶颈资源。

![[文献阅读] Emo-VITS - An Emotion Speech Synthesis Method Based on VITS](https://i-blog.csdnimg.cn/direct/4aadf56dd16246a79bbdbaf70ed36238.png)