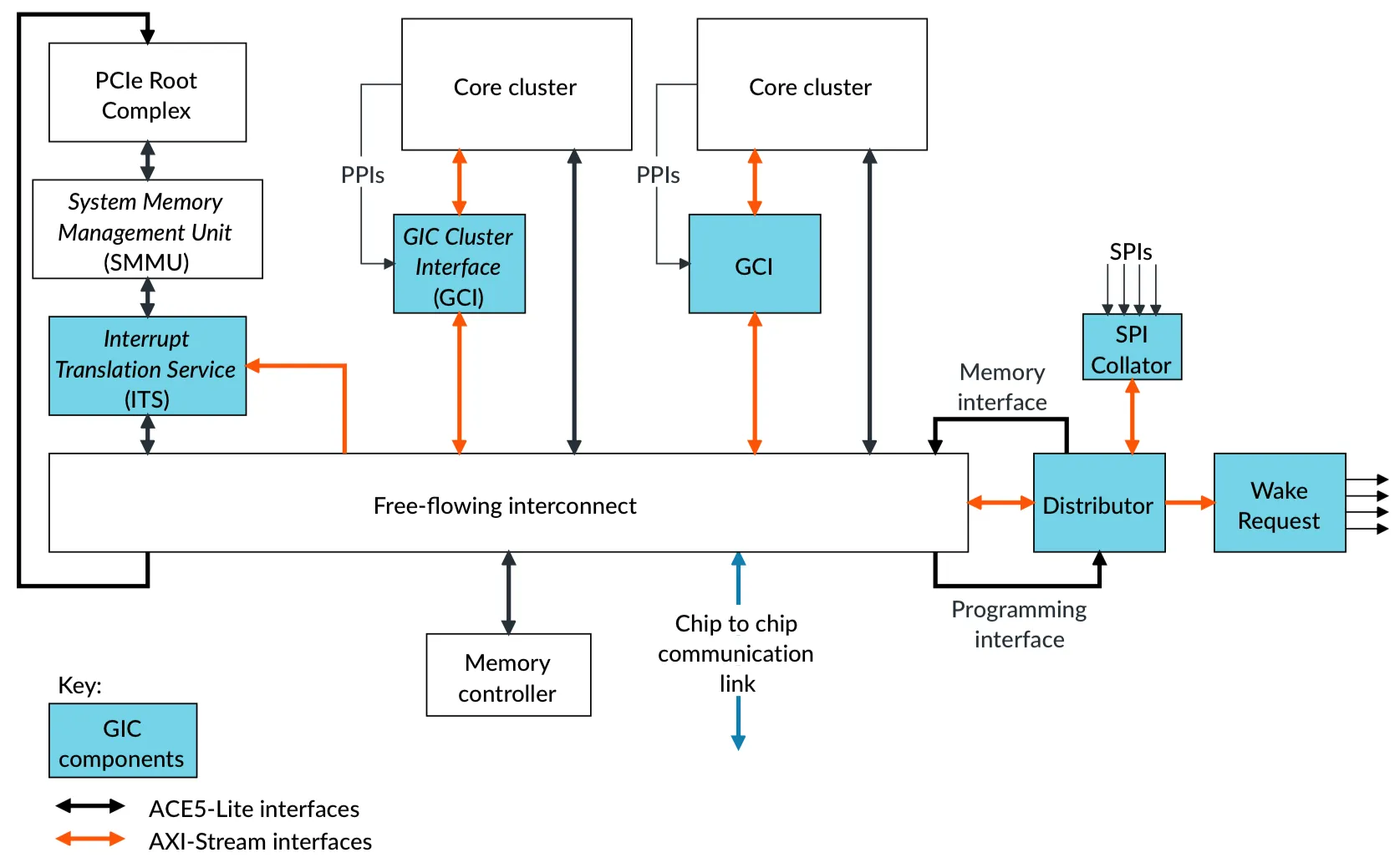

GIC-700是用于处理外设与处理器核之间,以及核与核之间中断的通用中断控制器。GIC-700支持分布式微体系结构,其中包含用于提供灵活GIC实现的几个独立块。

GIC700支持GICv3、GICv3.1、GICv4.1架构。

该微体系结构规模可从单核到互联多chip环境,最高支持16个chip,每个chip最多包含512个核。

所有的GIC -700模块都通过完全信任的AXI5-Stream接口通道进行通信。这意味着接口仅对其ic ready信号施加瞬态反压,使数据包能够在任何自由流动的互连上路由。通道可以通过专用的AXI5-Stream总线路由,也可以通过系统中任何可用的自由传输层路由。如果该通道上的所有事务完成而不依赖于任何其他事务,则该通道描述为自由流动。

1. 组件概述

GIC700包含几个重要的块,它们组合在一起工作,在系统中创建一个体系结构兼容GICv3、GICv3.1、GICv4的实现。

GIC700有如下的块:

- Distributor(GICD):gicd是GIC交互以及实现SPIs和LPIs功能的中心组件。它对除了GITS- TRANSLATER寄存器的整个GIC编程模型负责。在支持GICv4.1架构的实现中,gicd还会管理vSGIs和vPEs。gicd还维护multichip下有关SPI一致性的寄存器空间。chip上所有核的LPI功能都被组合到gicd内的单个cache中。

- GIC Cluster Interface(GCI):gci维护一组指定核的的PPIs和SGIs。一个gci组件可以支持1-64个核的规模。最好将其放置在处理器核旁边以减少它与核之间的连线。gci也被称为Redistributor。GICv3和GICv4.1架构指出一个redistributor的地址空间,在GICv3中被分为两部分,而在GICv4.1中被分为四部分。用于SGI功能的部分被放置在redistributor中,剩余的三个部分则放置在distributor中。GIC700支持从distributor分别下电gci以及和它关联的核。

- Interrupt Translation Service(ITS):ITS翻译基于消息的中断和消息信号中断(MSI/MSIx),它们源于外部PCI Express (PCIe)根复核(RC),或其他来源。ITS还在核心电源管理期间管理lpi。GIC700最多支持32个ITS模块。

- MSI-64 Encapsulator:MSI-64封装器是一个小组件,它将写入GITS_TRANSLATER寄存器所需的DeviceID (DID)组合到单个内存访问中。

- SPI Collator:GIC700支持最多1984个SPIs。SPI collator将SPIs转换为消息转发给gicd。这让gicd可以使用分层的时钟门控并且可以使用更激进的低功耗状态。GIC700最多可以包含32个SPI collator。1984个SPIs分配给32个SPI collator,每个SPI collator最多支持1024个SPIs。

- Wake Request:Wake Request组件包含了架构定义的每一个核的wake request信号。它是一个分离的组件,可以放置在远离gicd的位置,例如放置在SCP旁。

- GIC interconnect:该组件是一组组件的集合,用于在不同组件之间使用AXI5-Stream接口进行路由。

- Top level:顶层没有特定的接口,而是将时钟域或电源域内其他模块的接口组合在一起,以减少域桥接的数量。

2. 功能

GIC700提供中断服务和屏蔽,寄存器和编程接口,中断分组,安全,性能监控和错误修正

- 中断服务和中断屏蔽:

- 支持以下中断类型

- 最多56000个物理的LPIs。在GIC700中,一个外设通过写一个内存映射的寄存器来产生LPIs。

- 当支持GICv4.1架构时,每一个vPE最多可以支持56000个直接注入的vLPIs。

- 最多支持1984个SPIs。

- 每一个核最多支持48个PPIs,并且可以通过编程控制为边沿触发还是电平触发。

- 最多支持16个SGIs。

- 当支持GICv4.1架构时,每一个vPE最多可以支持16个直接注入的vSGIs

- 最多支持32个ITS。用于为基于消息的中断提供设备隔离以及ID转换。并且支持VM虚拟机直接访问设备。

- 中断屏蔽和32个级别的中断优先级,每一个中断优先级有5bit

- 支持以下中断类型

- 寄存器和编程接口:

- 使用MPIDR寄存器中的地址,实现灵活的亲和路由,支持四级亲和路由

- 每个芯片上的单个ACE5-Lite从属接口,用于在非单片配置中编程所有寄存器,但不包括GITS_TRANSLATER寄存器。每个ITS都有一个可选的ACE5-Lite从属接口,用于编程GITS_TRANSLATER寄存器。

- 在multichip下SPI寄存器数据的一致性视角

- 安全:

- 全局禁用安全的信号。gicd_ctlr_ds信号用于禁用系统的安全状态

- 中断分组(group0、group1ns、group1s)让中断路由到目标异常等级

- 性能监控

- GIC700提供PMU(performance monitoring unit)计数器,并且包含快照功能

- 错误修正和控制

- ARMv8.2 RAS(reliability accessibility serviceability)兼容架构错误上报:

- 软件访问错误

- ITS命令和转换错误

- 错误纠正码ECC(error correcting code)错误

- 错误中断控制,允许软件修复错误

- 软件机制可以触发和测试错误修复功能

- ARMv8.2 RAS(reliability accessibility serviceability)兼容架构错误上报:

3. GIC700与GIC600对比

| 功能 | GIC700 | GIC600 | 备注 |

|---|---|---|---|

| GIC架构版本 | v3.1, v4.1 | v3 | |

| SPI collator数量 | |||

| 32 | 1 | 对于GIC700,一个SPI collator最多可以支持1024个SPIs | |

| SPI数量 | 1984 | 960 | 960是指在不支持GICv3.1扩展的情况下最大SPIs数量 |

| 单个核支持的PPI数量 | 16,32,48 | 8,12,16 | 16是指在不支持GICv3.1扩展的情况下最大PPIs数量 |

| 支持直接注入vLPIs和vSGIs | 是 | 否 | |

| 支持地址空间分区和监控(MPAM memory partitioning and monitoring) | 是 | 否 | |

| 支持地址空间标签扩展(MTE memory tagging extension) | 是 | 否 | |

| 支持领域管理扩展(RME realm management extensions) | 是 | 否 | |

| 软件可以改变GIC安全属性 | 否 | 是 | 对于GIC600,软件可以修改GICD_CTLR.DS比特位 |

| ACE-Lite版本 | ACE5-Lite | ACE-Lite | |

| 每一个ITS可编程寄存器空间大小 | 当支持直接注入时4x64KB,否则为2x64KB | 2x64KB | |

| ITS最大数量 | 32 | 16 | |

| chips之间传输LPIs、SGIs、vSGIs的credits数量 | 1-8 | 1 | “Number of credits” 是一个信用系统,它定义了在两个芯片之间发送中断可以有多少未完成的传输。 |

| 支持额外的AXI4-Stream接口用于GITS_TRANSLATER寄存器的写事务 | 支持 | 不支持 | |

| 支持使用比配置更少的gicr | 支持 | 不支持 | |

| GCI处理器接口AXI数据总线宽度 | 16,32 | 16 | |

| GCI支持每一个核单独的wake request信号 | 支持 | 不支持 | |

| 支持的最大multichip数量 | 63 | 15 | |

| 支持local cross-chip地址 | 支持 | 不支持 | |

| 支持RAM I/O边带信号 | 支持 | 不支持 | |

| 支持过滤安全PMU事件 | 支持 | 不支持 | |

| 支持SPI RAM保留 | 支持 | 不支持 | |

| 支持不可屏蔽中断NMIs(non- maskable interrupt) | 支持 | 不支持 |