一、低功耗设计架构规划(Power Plan)

低功耗设计的起点是架构级的电源策略规划,主要包括:

电源域划分

基于功能模块的活跃度划分多电压域(Multi-VDD),非关键模块采用低电压(0.6-0.7V)可降低45-50%动态功耗。例如视频编解码模块可独立设置电压域。

动态调压技术

采用DVFS(动态电压频率调节)和AVS(自适应电压调节),根据负载实时调整工作点。某移动SoC通过DVFS实现30%的功耗优化。

电源关断设计

对非活跃模块实施Power Gating,配合状态保持寄存器(Retention FF)实现快速唤醒。需插入隔离单元(Isolation Cell)防止信号漂移。

二、RTL级功耗优化(Implementation)

在RTL阶段,工程师通过工具链实现快速迭代:

Spyglass Power优化

通过时钟门控效率分析(Q-to-Clock Ratio)、寄存器活动密度等指标识别优化点。典型案例:某AI加速器通过自动插入时钟门控,实现23%的动态功耗降低。

向量无关分析技术

无需仿真波形即可识别空闲周期,指导架构级优化。例如发现DSP模块50%时间处于闲置状态,触发深度睡眠模式改造。

形式化验证保障

采用Formality进行RTL与门级网表的等效性检查(LEC),确保低功耗逻辑修改的正确性。

三、精准功耗估算(Estimation)

全流程覆盖多精度估算工具:

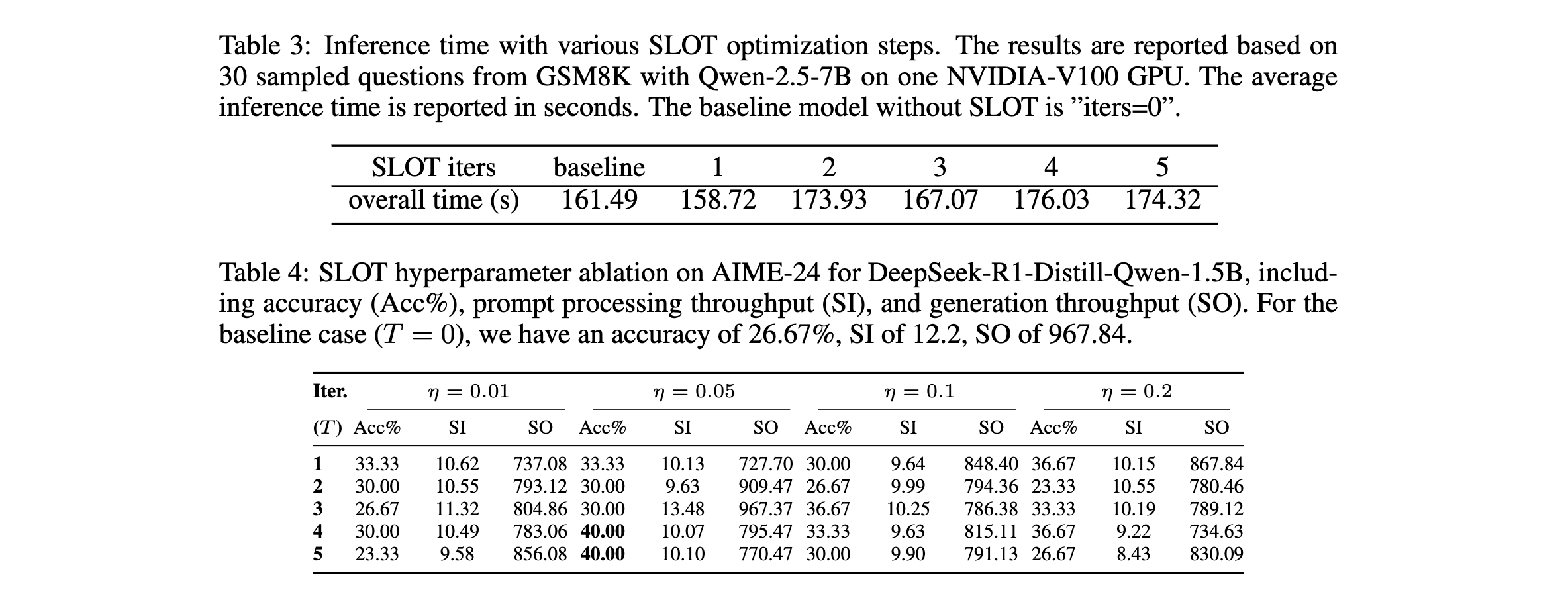

| 阶段 | 工具 | 精度 | 耗时案例 |

|---|---|---|---|

| RTL级 | SpyGlass PE | ±15% | 百万实例/15min |

| 门级平均 | PrimeTime PX | ±5% | 10GB SAIF/6h |

| 峰值功耗 | VCS+Siloti | ±2% | 加速21倍 |

Verdi Siloti技术突破

通过RTL与门级信号映射(99.5%匹配率),复用RTL仿真波形加速门级分析。某5nm芯片项目将原本7天的门级仿真缩短至8小时,功耗估算误差仅2%。

四、签核验证(SignOff)

确保低功耗设计正确实施的最后防线:

UPF一致性验证

使用VC LP检查电源策略文件,定位缺失的电平转换器(Level Shifter)或隔离单元。某车规芯片通过静态验证发现12处跨电压域连接错误。

物理实现验证

IC Compiler II后布局阶段检查电源网络IR Drop,PrimeRail分析动态压降热点。某GPU项目通过优化电源网格密度,解决5%的局部压降问题。

功耗完整性签核

采用Redhawk进行全芯片电迁移(EM)和静态功耗分析,确保符合TSMC N7工艺的6mW/mm²泄漏功耗要求。

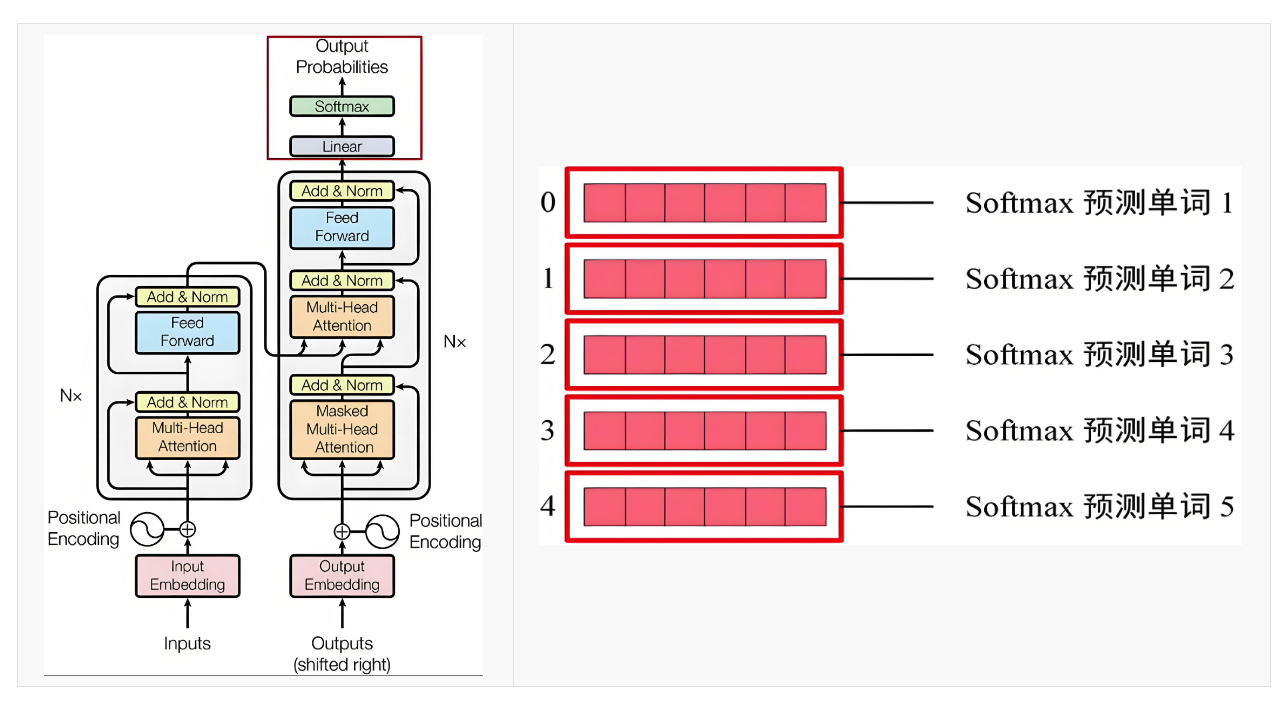

| 检查项 | 目标值 | 实测值 | 状态 |

|---|---|---|---|

| 最大IR Drop | <5% VDD | 4.7% | ✅ |

| EM violation | 0 | 2 | ⚠️ |

| 漏电功耗 | <10mW | 8.3mW | ✅ |

| 动态功耗误差 | ±3% | +2.1% | ✅ |

五、行业最佳实践

分层优化策略

RTL阶段完成80%的架构优化,门级阶段聚焦20%的精细化调整。

数据驱动迭代

建立功耗回归测试套件,跟踪每个commit的功耗变化趋势。某通信芯片团队通过持续监控,将功耗超标风险降低70%。

工具链协同

Synopsys全流程方案实现数据贯通:Spyglass优化建议可直接导入Design Compiler实现,Verdi波形数据无缝对接PrimeTime PX。

结语

随着AIoT和移动设备对能效要求的持续提升,低功耗设计已从可选技巧变为必备能力。通过架构创新、工具链协同和严谨的签核验证,工程师正在不断突破"每瓦特性能"的极限。

![[特殊字符]《Qt实战:基于QCustomPlot的装药燃面动态曲线绘制(附右键菜单/样式美化/完整源码)》](https://i-blog.csdnimg.cn/direct/221b201d8c6049afa7fa8767fdb193f4.png)