TDR真的是一个用来看阻抗跟Delay的好工具,通过一个Port的测试就可以看到通道各个位置的阻抗变化。 可是使用上其实没这么单纯,有很多细节需要非常地小心,才可以真正地看到您想看的信息!

就让我们整理3个极为重要的TDR使用小细节,让您在看TDR阻抗图时可以看到最正确的信息,使用上更为得心应手!

TDR读阻抗不是只看绝对值! 教您利用正确的方法判读阻抗!

我们很常遇到EE或是同业工程师在判读TDR阻抗时,直接透过TDR阻抗图的数值来判断对象或是设计的阻抗大小,我们必须讲,这其实是不对的!

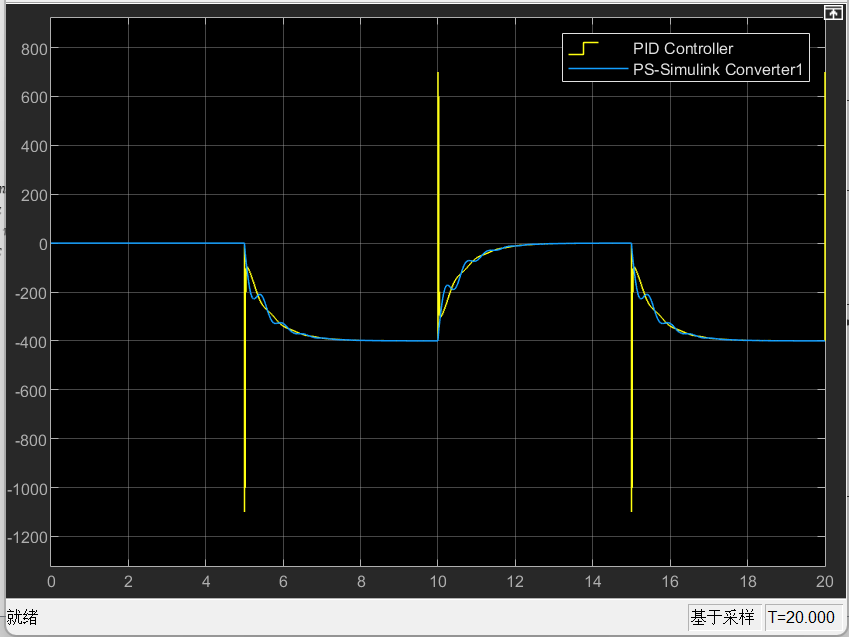

我们之前提到,传输线的TDR因为步阶波会变成稳态的关系,所以最后的阻抗会是传输线的特性阻抗加上其本身的直流电阻,因此我们会在TDR图上看到阻抗有爬坡的上升特性,而差动对又因为两两互相参考的关系,所以爬升的阻抗还会再多一倍:

透过TDR图判断传输线的真实阻抗,我们要看的是起头这个点,这个点的阻抗位置才是传输线的真实特性阻抗,后续的任何爬升都不应该视为传输线的真正阻抗。

TDR阻抗是透过相对值来判断,而不是绝对值!

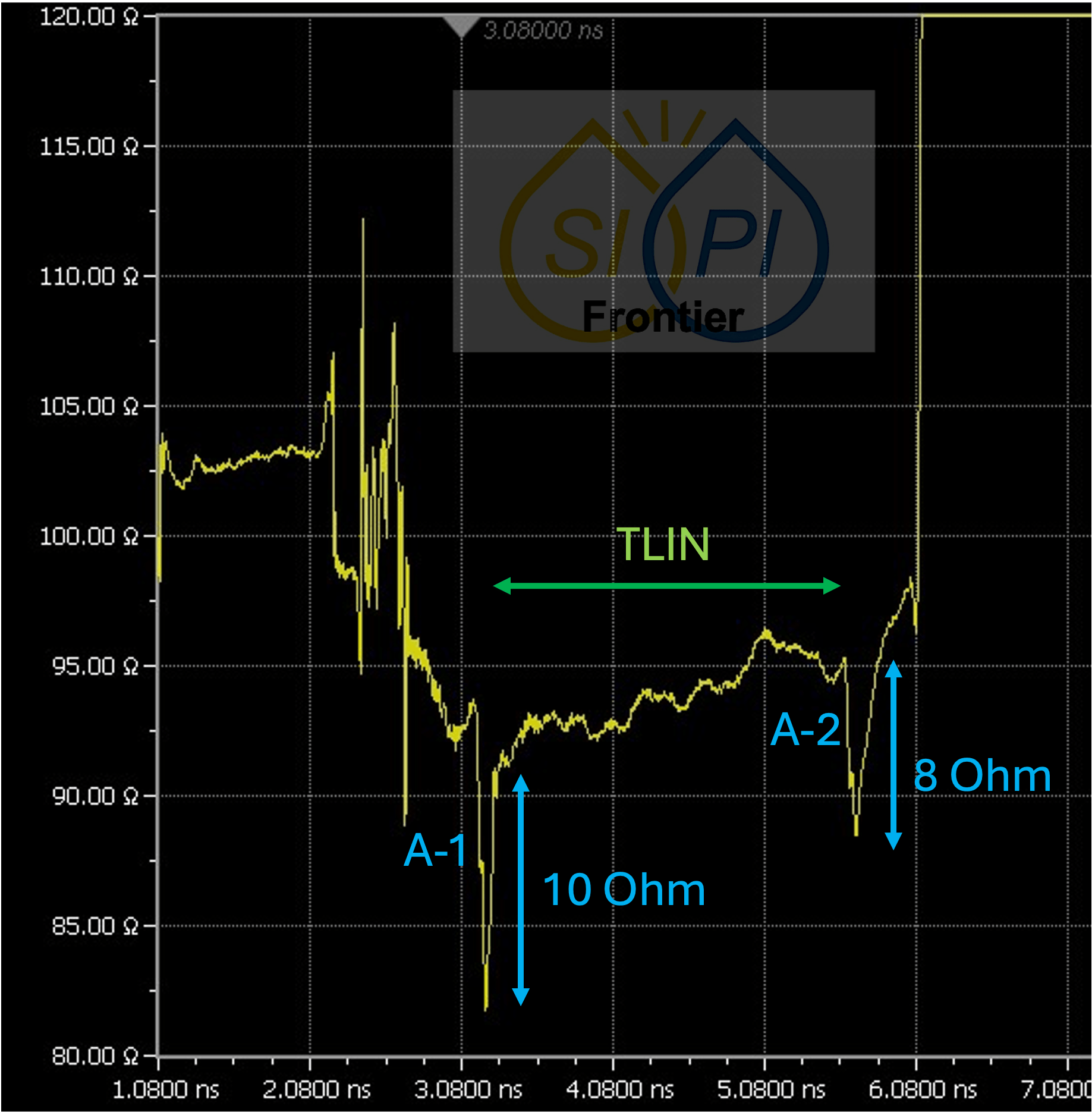

但也因为这个爬坡的特性,所以会造成通道内其他物件的阻抗判读有所变化。 下图是一张真实的TDR测试图,中间那段较为平滑的位置为传输线,前后各两个阻抗掉落点,第一个我们称作A-1,掉了10Ohm,阻抗读值为82Ohm,第二个称作A-2,掉了8Ohm,阻抗读值为87Ohm。

一般而言,大家都会觉得阻抗就是以读值为定,所以A-1的阻抗就是82Ohm,A-2则为图上显示的87Ohm,但其实并不然,由于阻抗的爬升效应,使得A-2的参考阻抗已从传输线设计的92Ohm变成大约95Ohm。 也就是说,A-1由于是在传输线的起头所掉落的,从92Ohm掉到82Ohm,我们可以说对于92Ohm的通道而言,它是82Ohm的设计; 而对于A-2来讲,由于是从95Ohm掉下来的,对于同样的92Ohm通道,它的阻抗不会是图上的87Ohm,而是84Ohm,换句话说,我们会对这条传输线的阻抗做归一化(Re-normalization)至92Ohm!

其实与其说去知道这些阻抗掉落点的真实阻抗,我们在看这些设计时,主要看的会是相对阻抗,而不是绝对阻抗,也就是到底掉了几欧姆,或是抬升了几欧姆。 尽量避免通道上阻抗的变化,以求一个Transparent的通道,将Return loss控制到最佳状况,降低反射现象,以求最佳的SI表现!

分辨率 – 注意TDR步阶波的上升时间

在使用TDR时,要非常注意分辨率(Resolution)这个非常关键的概念,它决定了你能不能看得清楚一个高速通道里的每一个细节与其带来的阻抗变化。

简单来说,TDR的分辨率可以视为最小可以分辨的空间距离,假如这个分辨率是100mil,那你就可以看到大于100mil的物件是否有剧烈的阻抗变化。

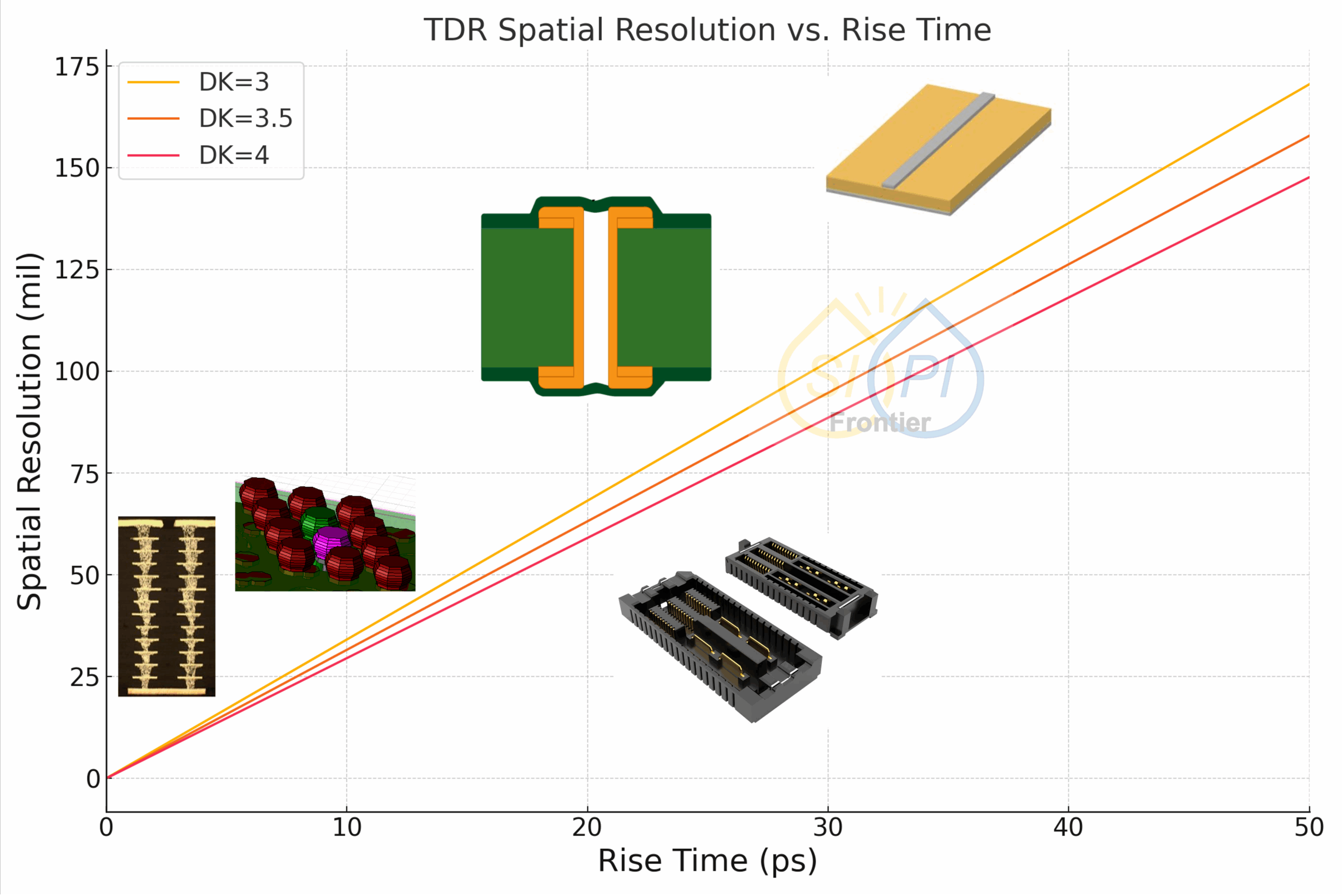

TDR的分辨率,主要受到步阶波上升时间(Rise time)的限制。 因为步阶波越快,代表它的信号前缘越陡峭,这样它就可以在更短的距离内被反射回来,让示波器或是网络分析仪接收到反射信号,我们就可以透过数据分辨出非常近的两个结构,或是看到更为细致的微小结构。

TDR分辨率的计算

TDR分辨率可以简化成这样的算法:

Resolution=v×tr2

v为电磁波在介质中的传递速度v=c/√DK,c为光速3×108m/s,tr为上升时间。

主要就是利用距离d=v \times t这个算式求得,要再除以2的原因是因为TDR是反射的原理,所以这段时间包含了讯号「来回」的距离,对我们而言只需要一半就好。

举个例吧:一般我们常用的TDR仪器或是网络分析仪的默认Rise time是35ps,在介电常数为4(DK=4)的材料里,它的TDR分辨率大约是:

3×108/√4×35/2=100mil

也就是说,大于100mil的结构才比较能被35ps的TDR给捕捉到,小于这个尺寸,或许你能看到阻抗的变化,但你不知道这个阻抗变化是来自于这个对象的哪里!

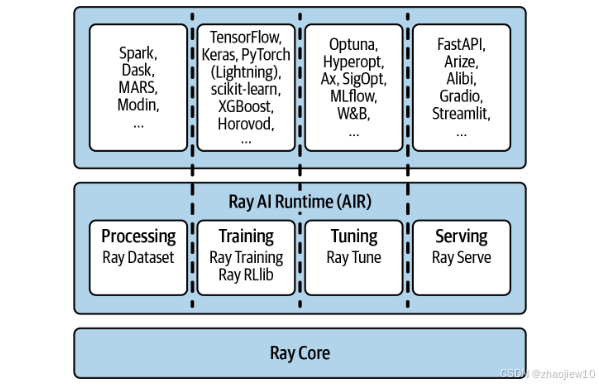

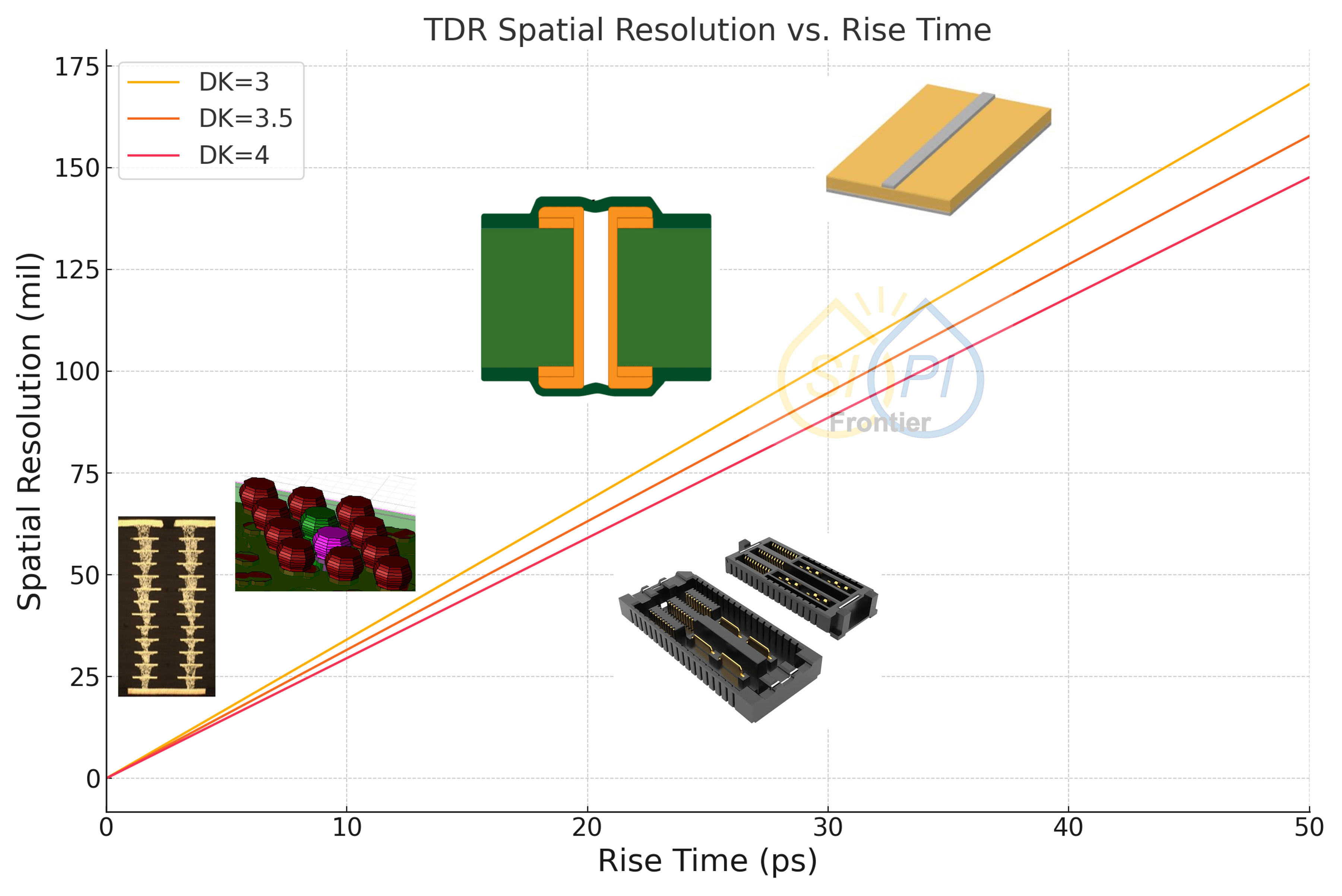

TDR分辨率 vs Rise time and DK

根据这个算式,我们整理了信号在不同DK的介质内,Rise time与Resolution的关系,并列出一些结构适用的Rise time区间,例如连接器,大概是1-2mm(40-80mil),所以Rise time小于25ps都是可以看得清楚的,而尺寸小如Solderball或是uVia,就会需要更小的Rise time,大约10ps, 也就是说系统层级上,如果要考虑到Solderball的效应,至少要到112G-PAM4以上的速度会比较明显,当然这不是说在这以下的速度不需要考虑,而是这个性价比可能不高!

总结,如果你要看穿一个Via里的小变化(特别是Via pad and Via barrel),或者想知道微型连接器的阻抗跳动,则TDR分辨率就变得非常重要。 如果分辨率不够高,那么这些问题就会被「模糊掉」,根本看不出来。 这也是为什么高速板在做TDR测试时,会选择Rise time更短的脉冲来源,例如30ps甚至20ps的TDR系统,因为你想看的变化,往往就在1mm之内。

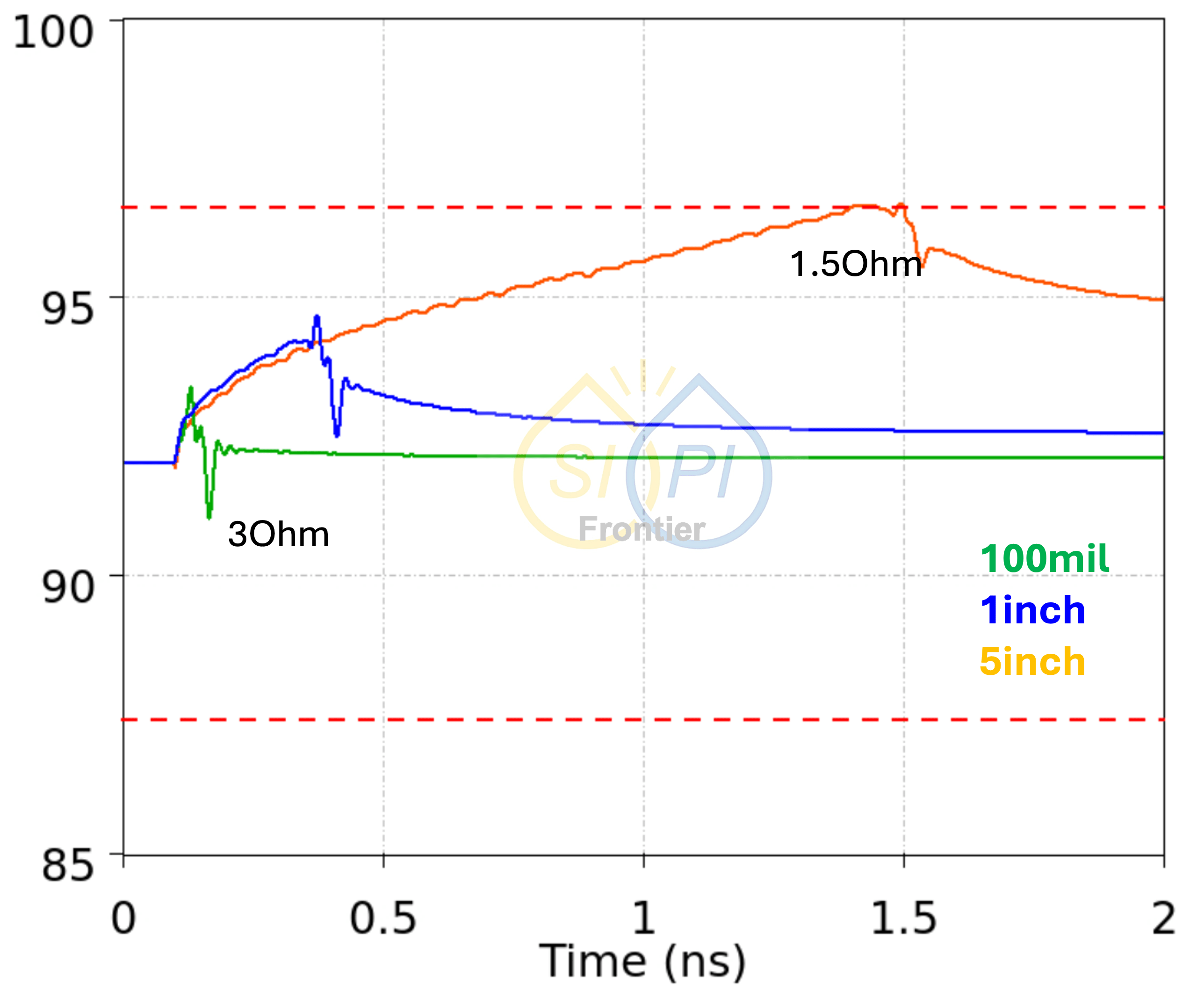

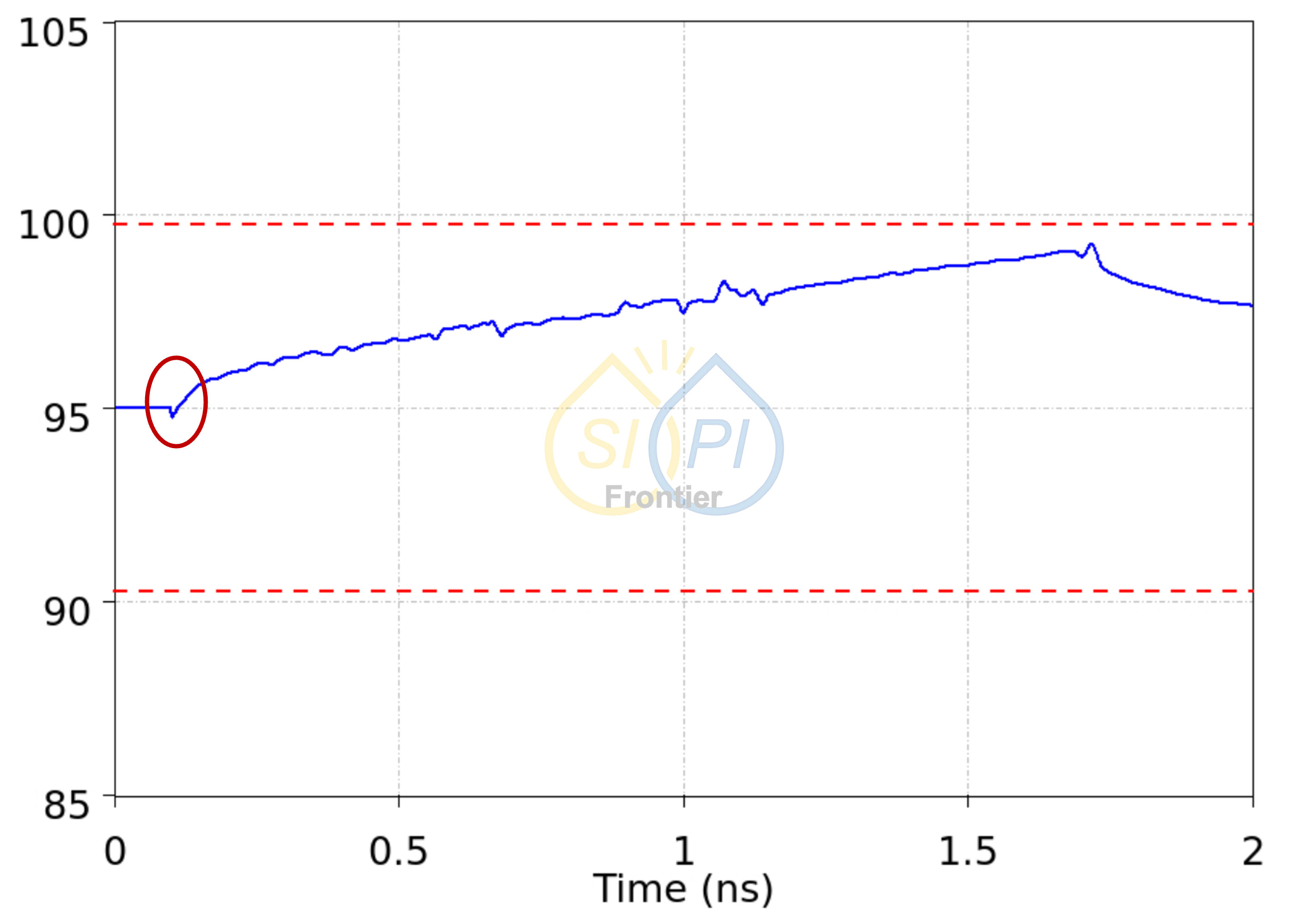

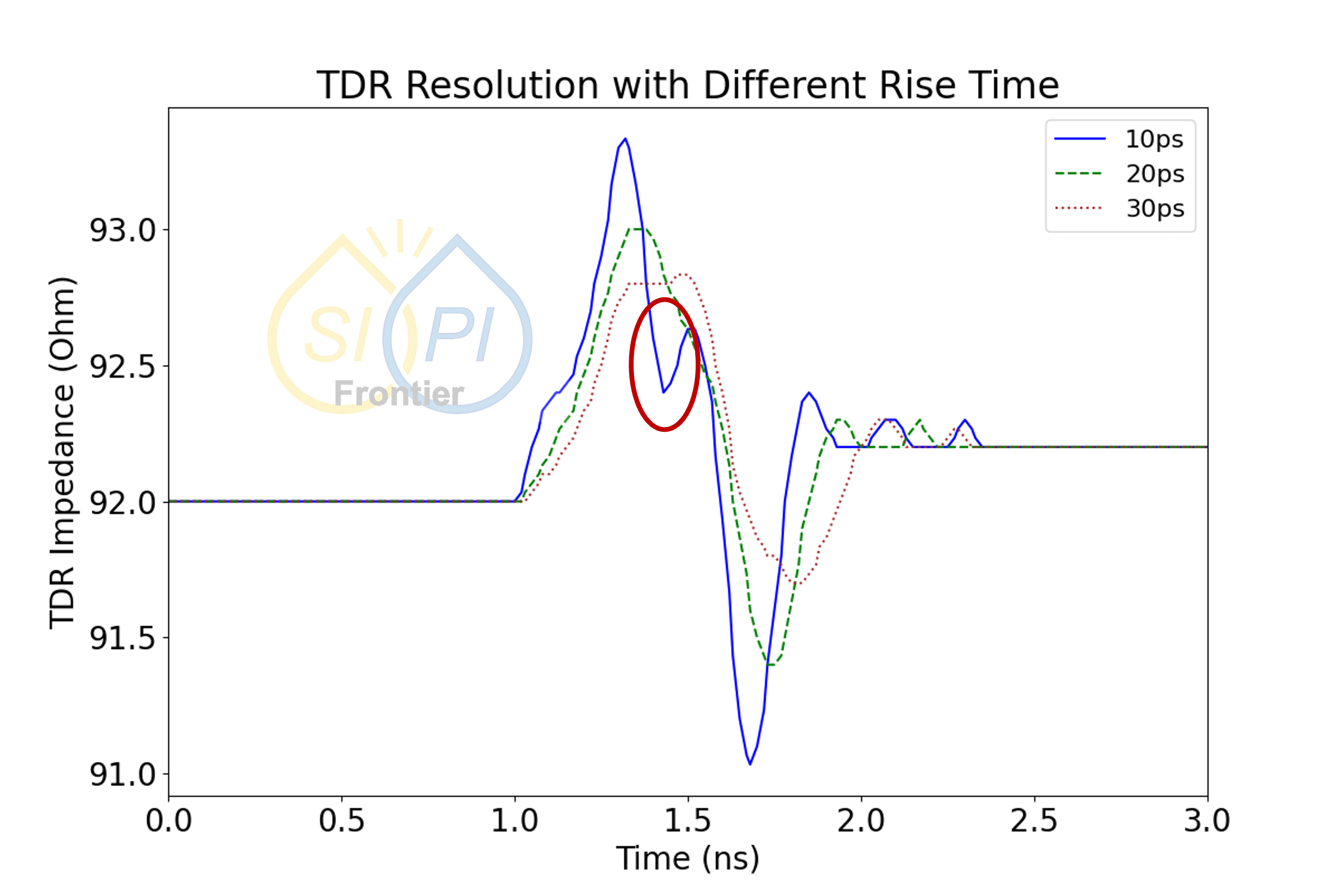

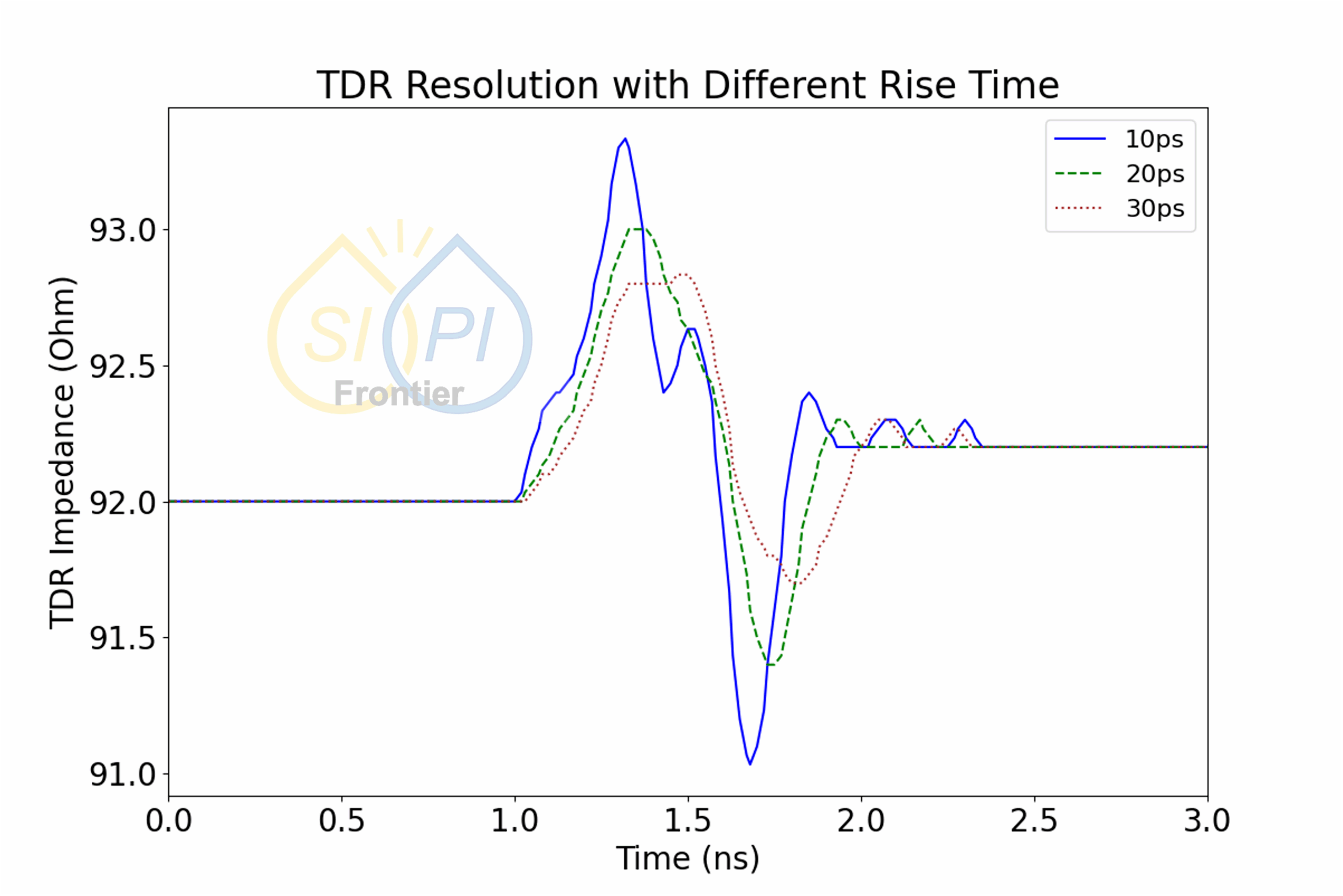

就像这张PCB Via的TDR模拟结果,10ps时就可以很明显看到在1.5ns左右有一个跳动点,而其它较慢的Rise time则没有办法看出这个地方有阻抗变化!

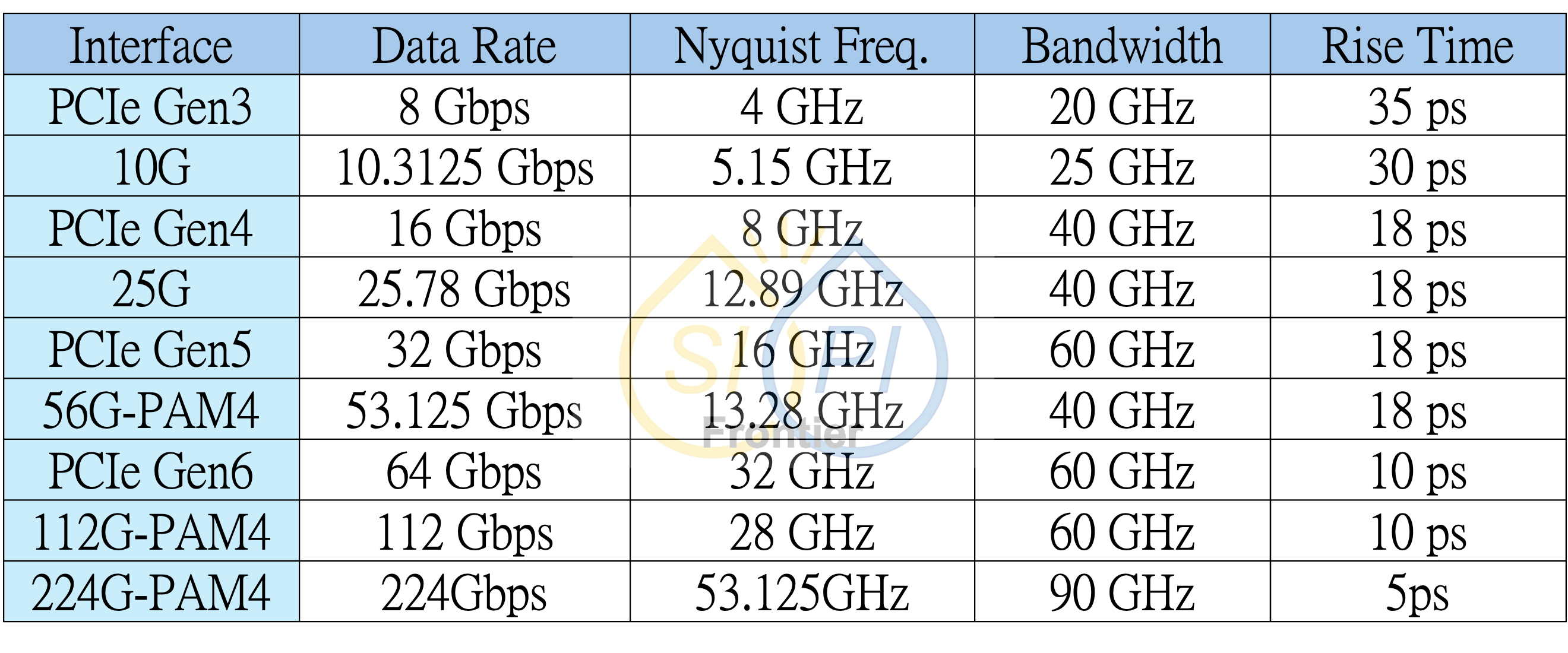

依照实际状况设定正确的Rise time

不过也不要太过勉强自己,为了要做到最好的设计,看到最细微的位置,而选用过小的Rise time,这会使得你的设计会太过Overdesign。 我们建议针对你的高速信号带宽来做设定,如下表格,列出常见的一些高速接口的Data Rate、对应的Nyquist Frequency、带宽、以及Rise time,供各位参考。

Rise time不是一成不变,变慢的Rise time导致误判TDR阻抗

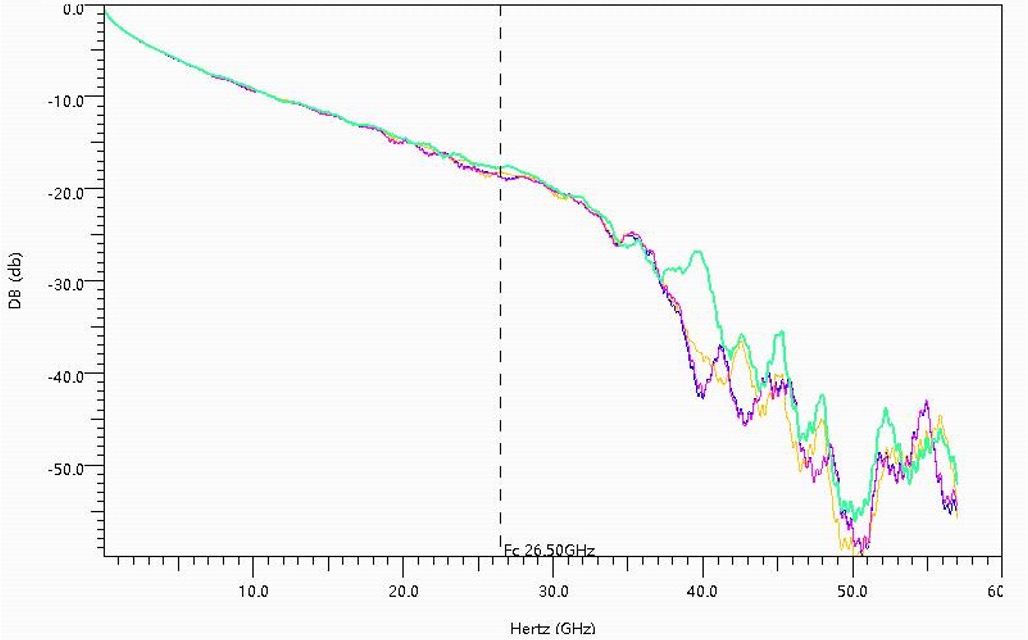

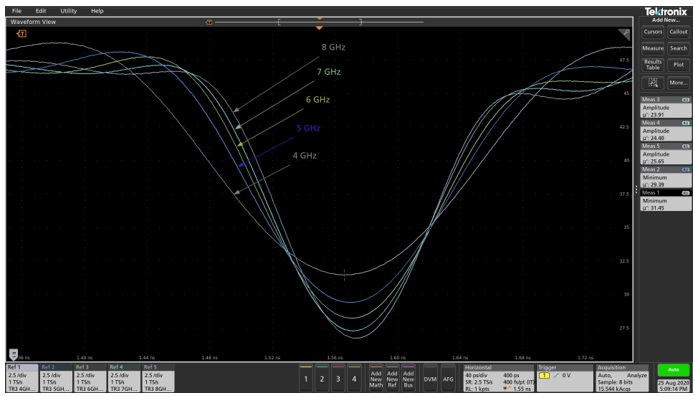

你知道高速讯号通道其实是一个低通滤波器吗? 你们看到的通道Insertion loss应该都是长这样吧? 低频能量传递几乎100%,高频损耗越来越大,能量衰减越多。

所以妥妥一个低通滤波器!

低通滤波器有一个特征:输入信号的Rise time,会随着损耗增加而上升(或者说变缓)。

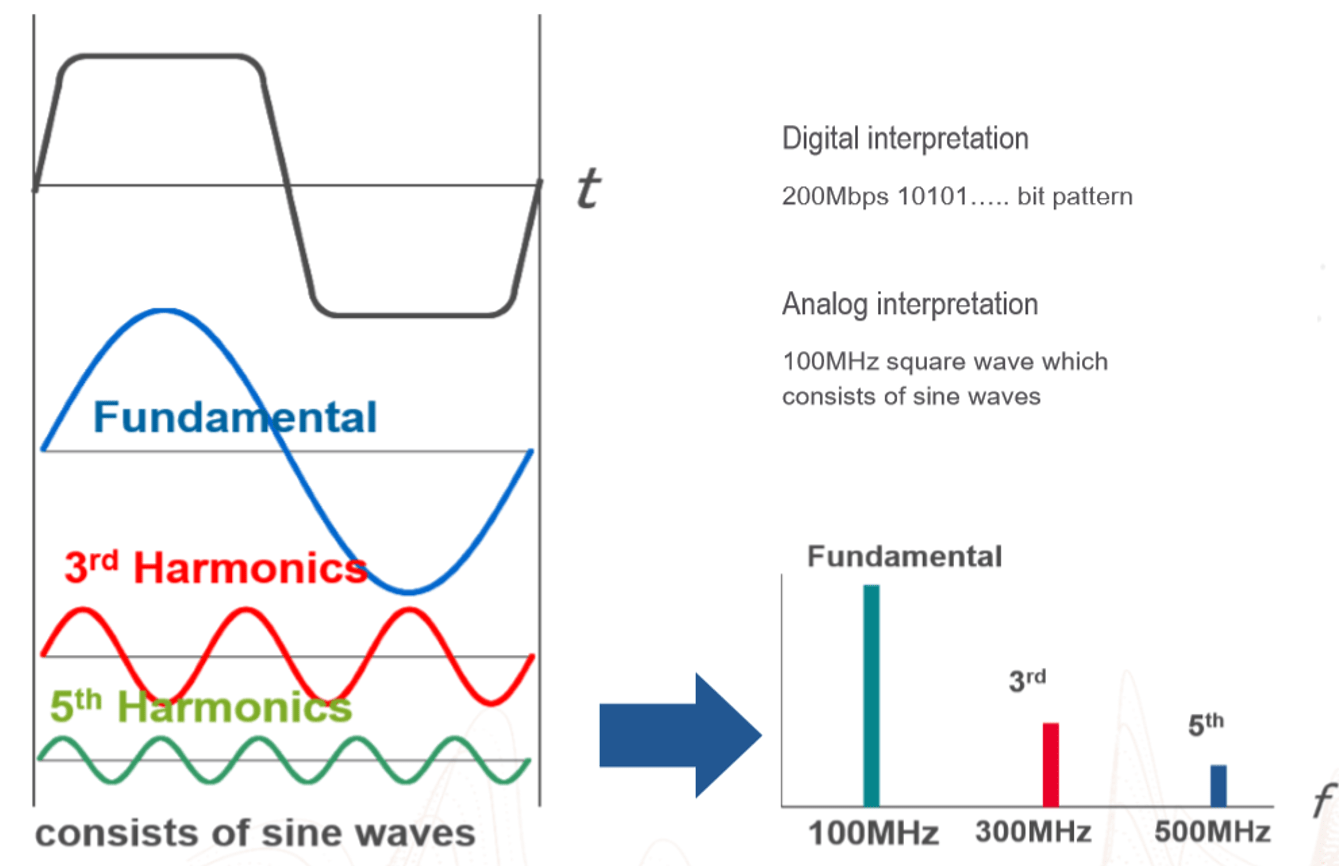

原因是讯号的高频成分是由Rise time所组成的,越快速的Rise time,则高频成分越多(也就是为什么越高速的讯号会带来更高的带宽)。 所以当高频成分被滤除时,Rise time就会变缓变慢。

高速信号的Rise time是由许多高频谐波组合而成的:

Rise time 随着通道损耗增加而变缓变慢:

再次强调,TDR测试,起头的阻抗最准确

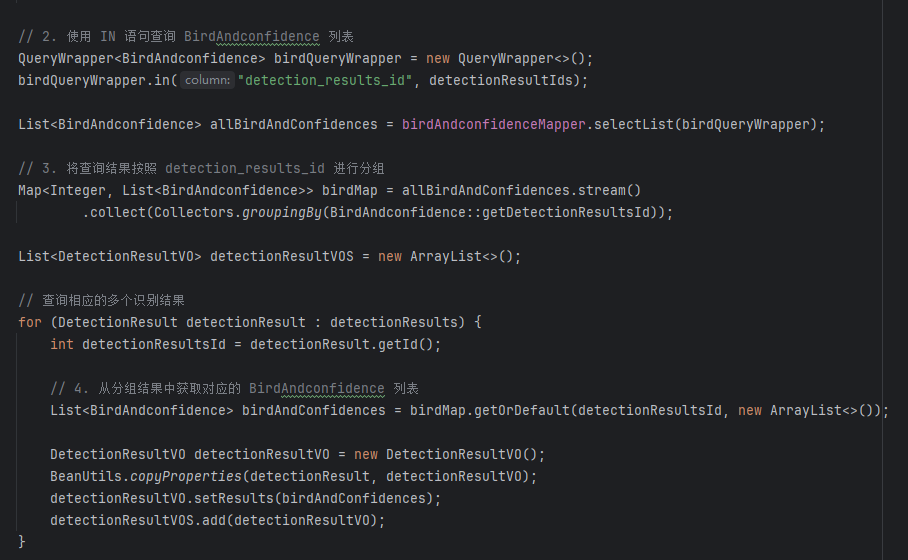

我们先来看一个简单的公式:

VTDR(t)=Vincident(t)(dvdt)∗h(t)

Vincident(t)是入射的步阶波,VTDR(t)是TDR仪器收到的反射讯号,h(t)则是待测物的Impulse response,*这个符号在做卷积(Convolution)这个动作。

不用想得太复杂,想象信号入射波跟通道的频率响应做类似相乘的动作,就可以得到反射信号。

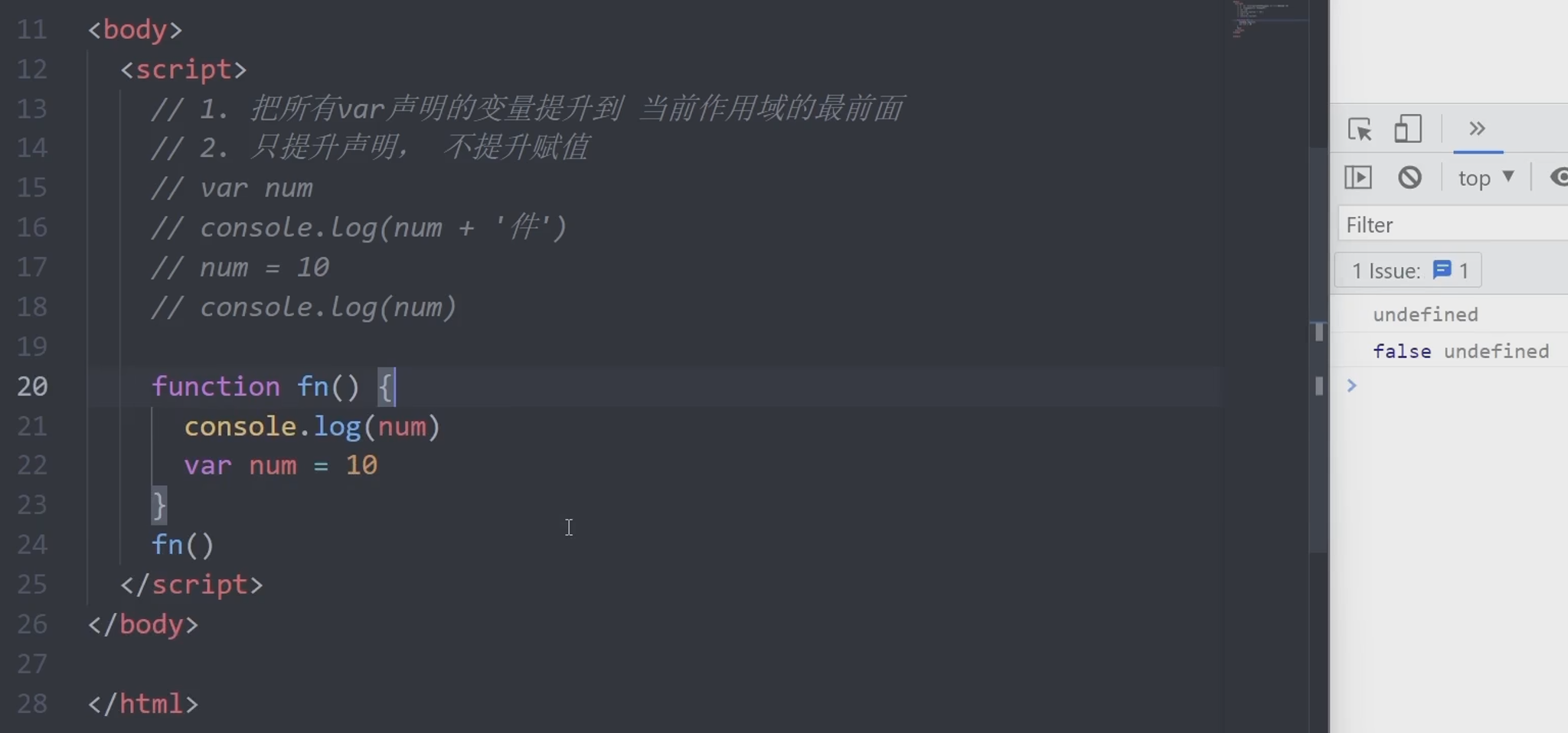

所以如果入射波的Rise time变大,则收到的反射波形的变化也会跟着变小,阻抗变化也会变小。 一样的这张图就可以看出这种现象!

我们也可以透过带宽来解析,越快的上升时间会带来较宽的带宽:

BW=0.35RT

所以当测试用探棒的带宽越宽,等效的上升时间越小,TDR就可以看得越清楚(更多的内容可以参考这里):

藉由这些观念,我们就可以知道,利用TDR做阻抗测试,最准确的时间点就是讯号刚打进去的那个点,也就是讯号的起头。 当讯号走远之后,Rise time会越来越慢,测到的阻抗变化就会越来越小,原本假设阻抗差异要5Ohm,可是Rise time变慢之后,可能就只剩4Ohm。

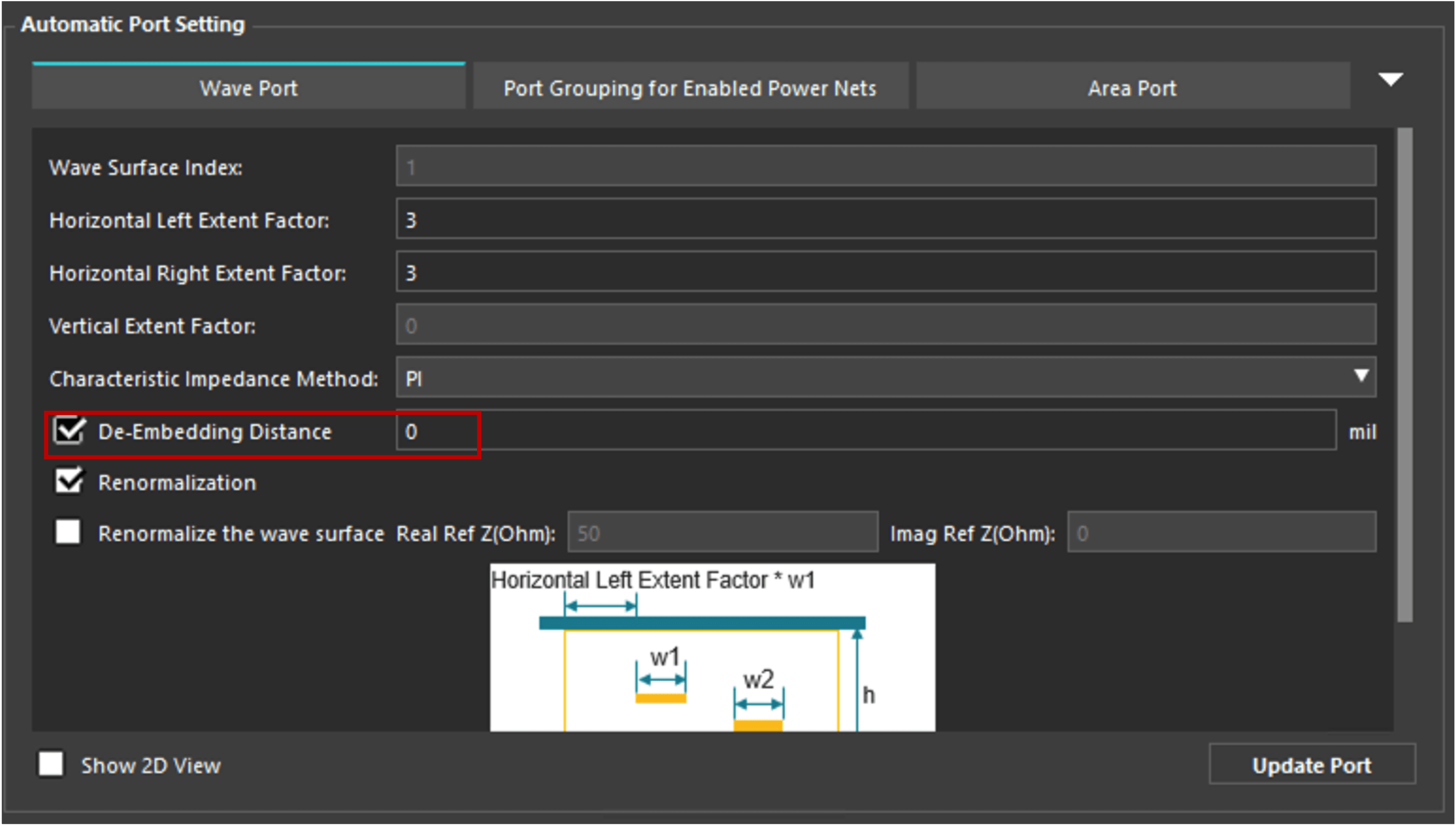

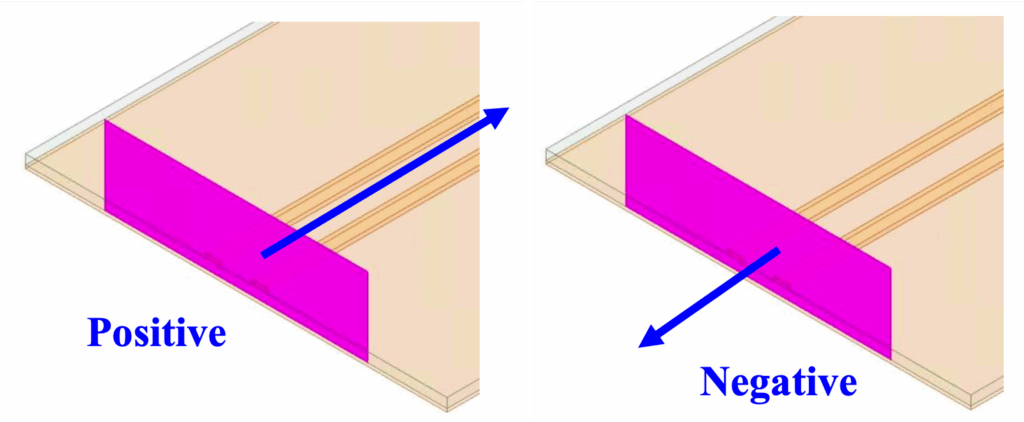

我们透过一种极为简单的模拟来看这个现象,在Clarity里头,我们跑模拟都要设定Wave port,这个Wave port有一个很好的功能叫De-embedded,预设是没开启的,当我们打开之后,可以填线长,这是在说Wave port可以平移多少走线长度,假设模拟待测物是500mil的传输线,则这个De-embedded长度如果是+300mil,那模拟结果会马上变成200mil的结果,如果我们填入-500mil,则结果会变成1inch的数据。

当我们在跑传输线时这个功能非常好用,因为这样我们就不用耗费一大堆时间在等待长传输线的模拟结果。

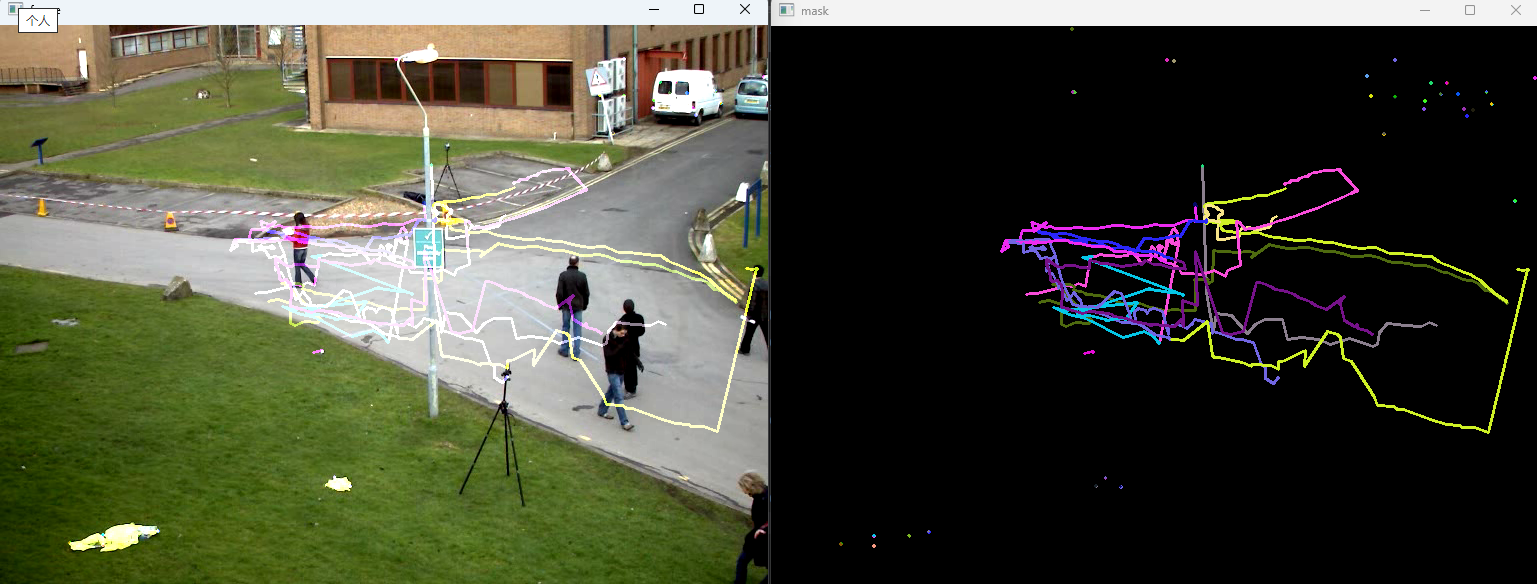

透过这种方式,我们延长了PCB via的馈入线,可以看到阻抗变化随着走线距离越长,而变得更小。