1.源码来源vivado xilinx官方实例

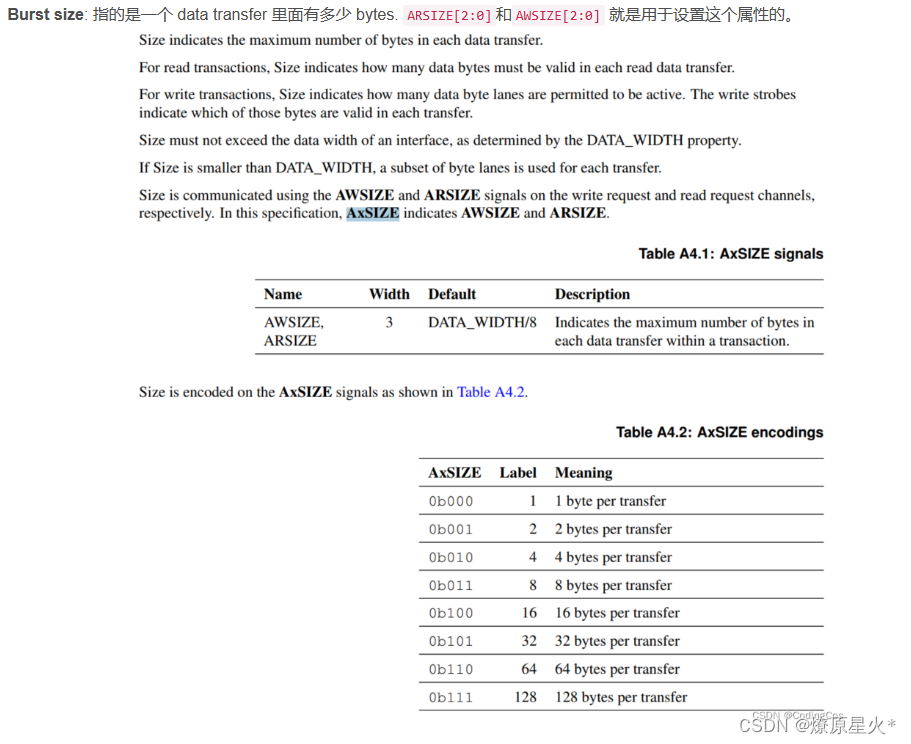

2.[2:0]M_AXI_ARSIZE:指的是一个 data transfer 里面有多少 Bytes——这里我写的是3(即2^3=8B)——8*8=64bit代表你想往axi总线的搬移数据的位宽。

3.

Burst length: ARLEN[7:0]和AWLEN[7:0] 突发传输长度是指在一次突发传输中所进行的传输(data transfer)次数,在传输完初始地址后,进行的数据传输次数就是突发传输长度。在 AXI4 中:

- INCR 类型最大支持长度为 256=FF(1111 1111)+1;——根据实际一次突发的地址偏移量(即数据量来计算)计算公式如下:——burst_size_bytes=(Burst length+1)*往axi总线的搬移数据的位宽

4.

burst_size_bytes:一次突发的数据量大小(即数据量的偏移地址)eg:4kB,512B

5.

C_M_TARGET_SLAVE_BASE_ADD:——表示突发地址的基地址:eg:0X90000000

6.

total_capacity(总的数据量):该参数官方代码是没有的——但是实际工程中使用是有的可以作为继续突发数据的条件eg:

if(axi_awaddr < ddr_buffer_capacity)

axi_awaddr <= axi_awaddr + burst_size_bytes;

![[计算机提升] 系统软件:信息类](https://img-blog.csdnimg.cn/a19c036bbc154774b88a3c87ae9d0a92.png)