可参考

基于FPGA的DDR3设计(2)DDR3各时钟频率及带宽分析 - 知乎 (zhihu.com)

DDR3的时钟频率配置要看两个手册:

1.DDR3器件的手册。

2.开发板芯片的手册

器件

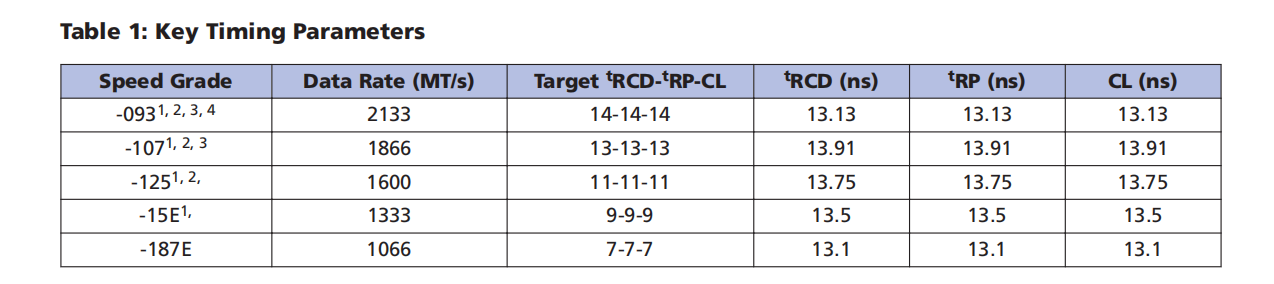

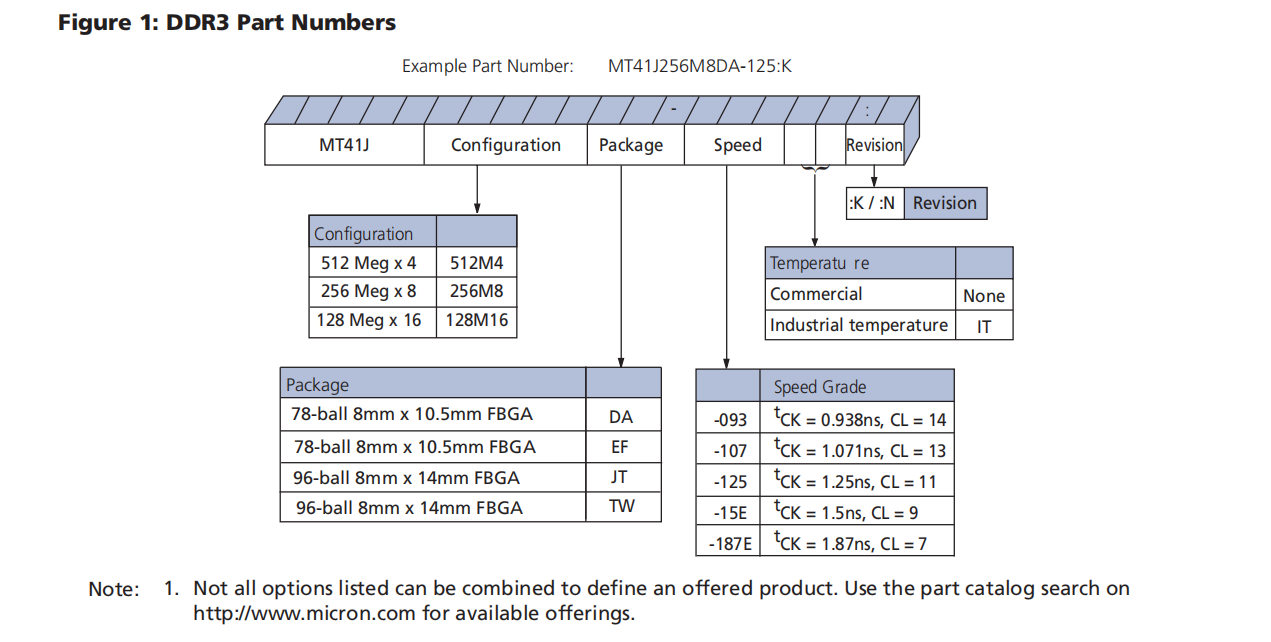

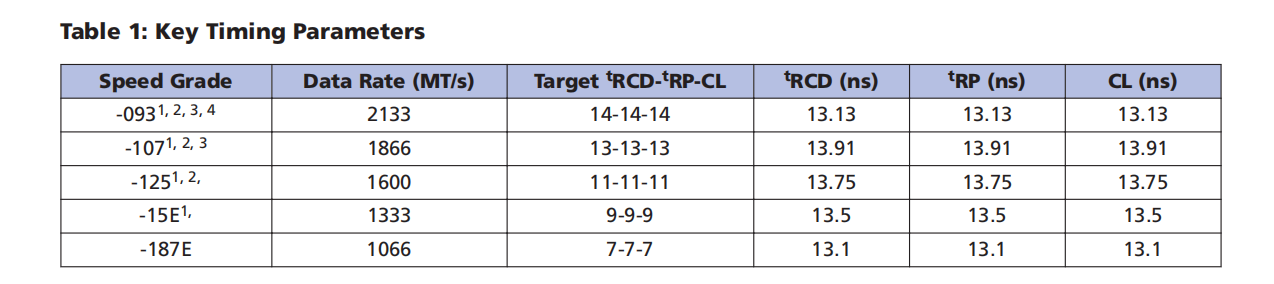

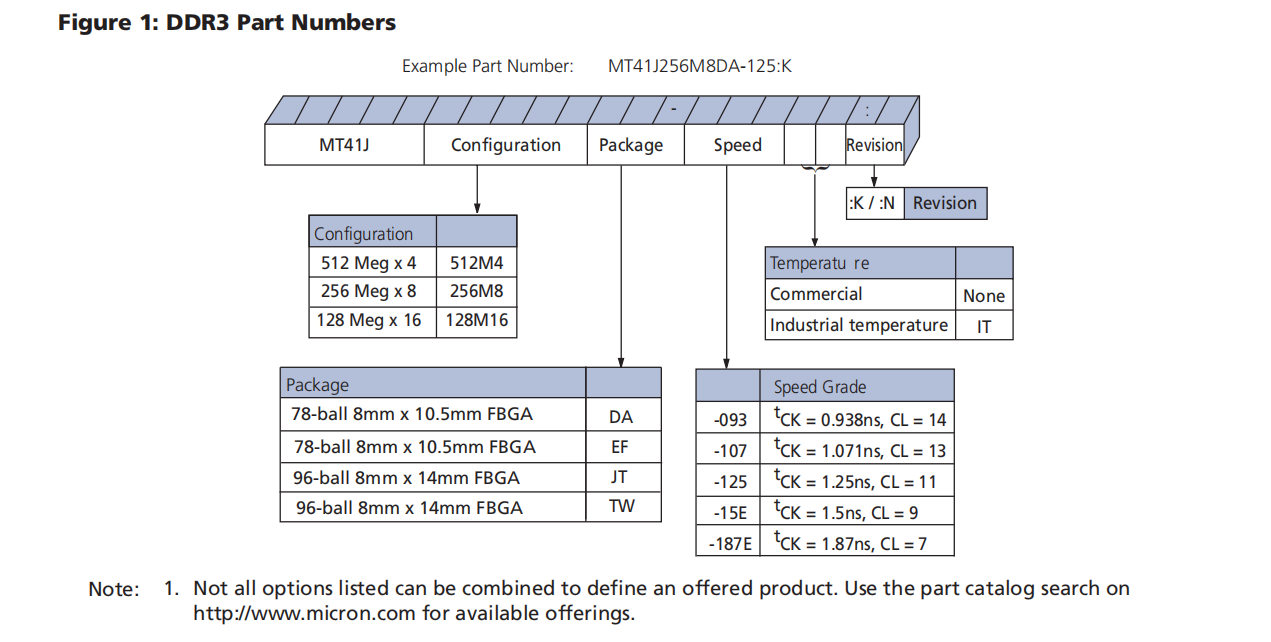

器件名称:MT41J128M16JT-125:K

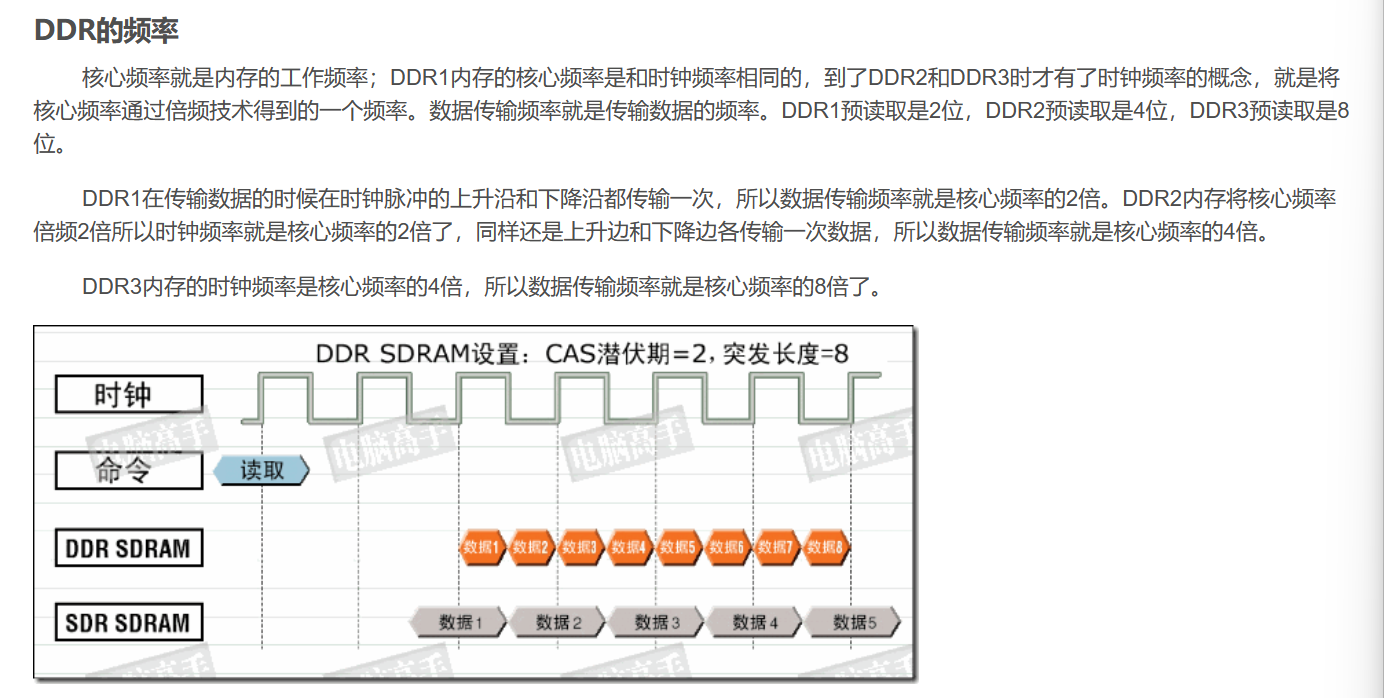

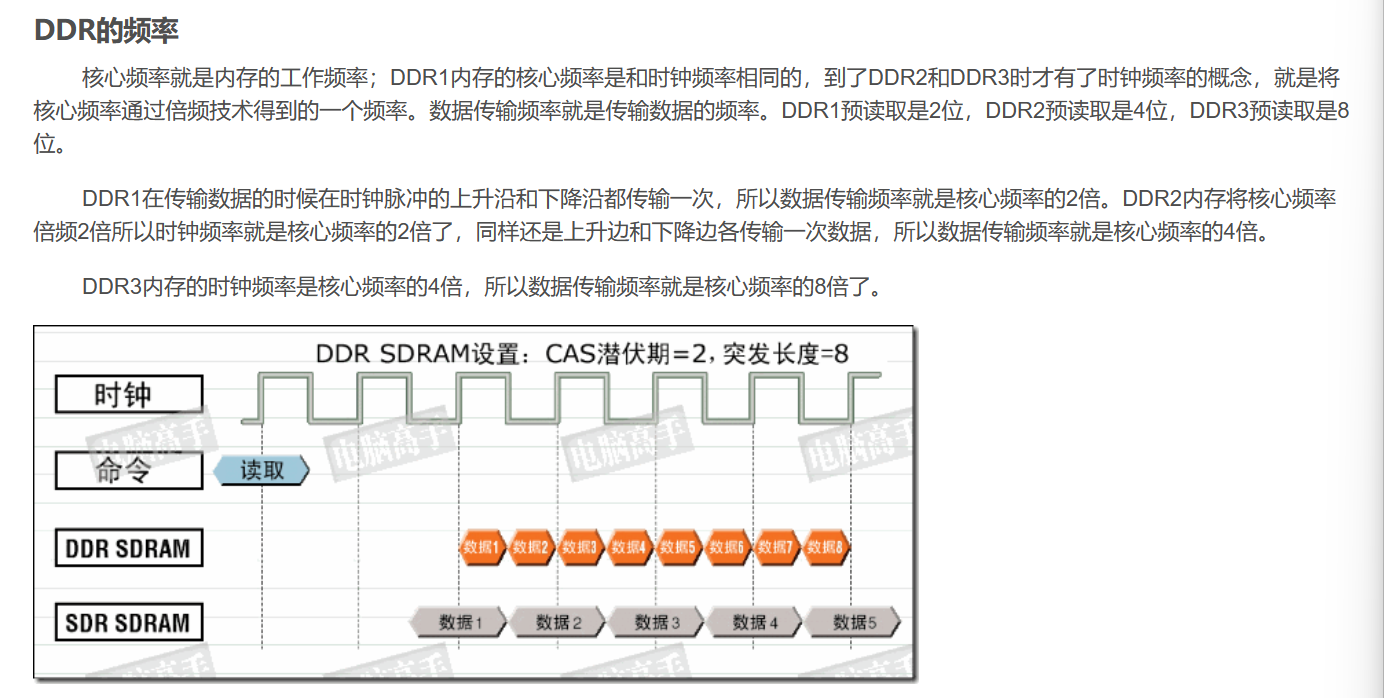

tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz;此处的IO时钟频率也就是DDR3的频率。

器件最大支持800MHZ,其中核心频率200MHZ,工作频率800MHZ。

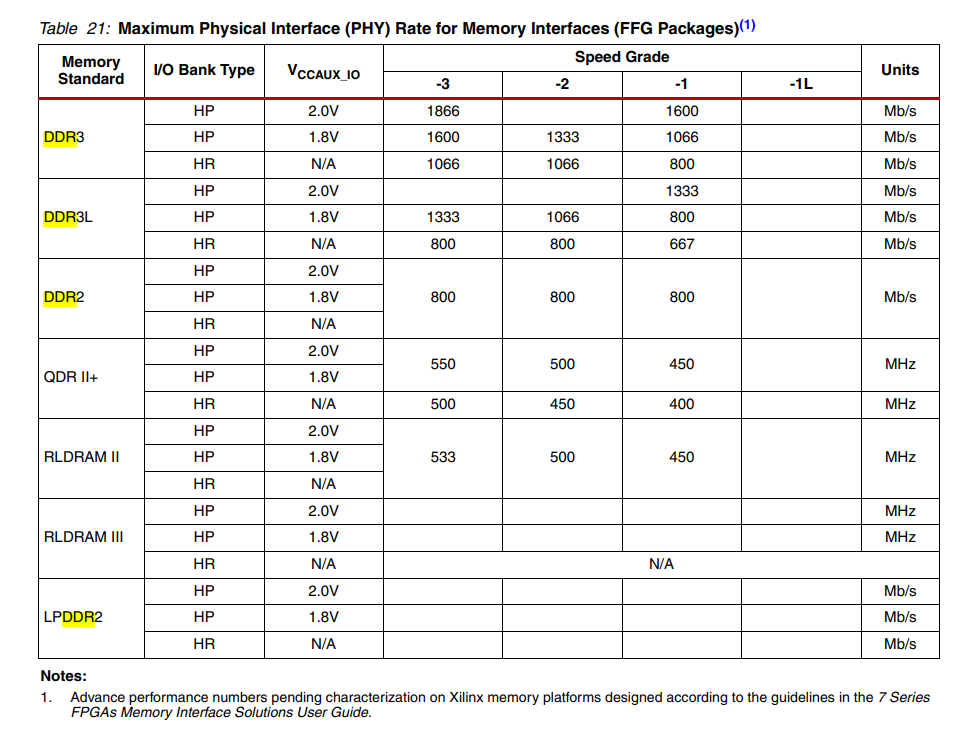

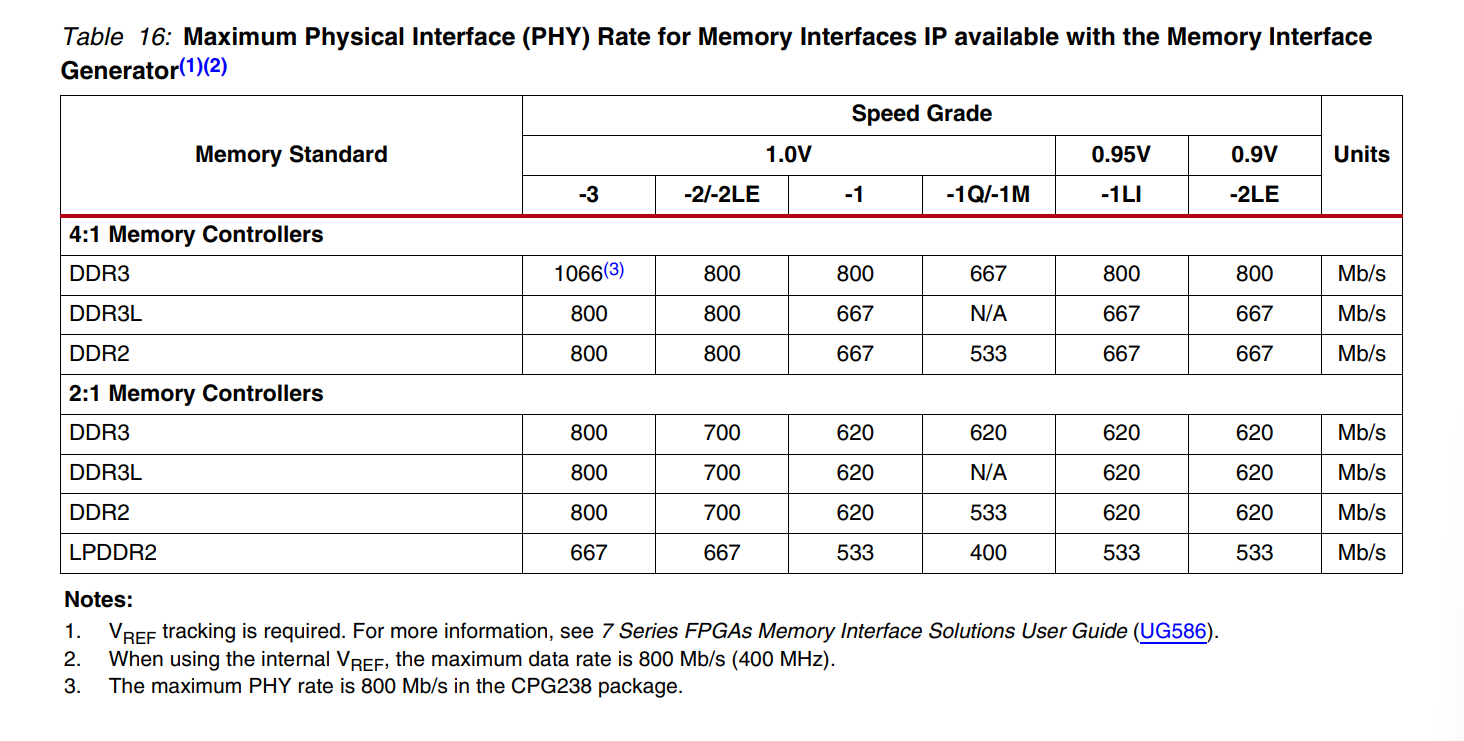

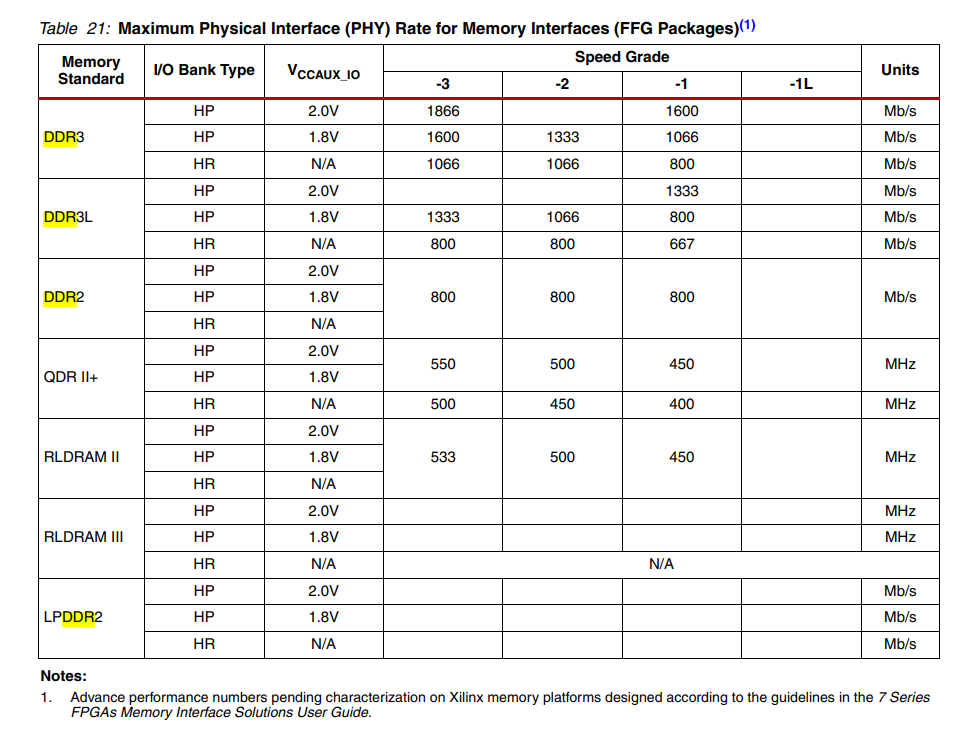

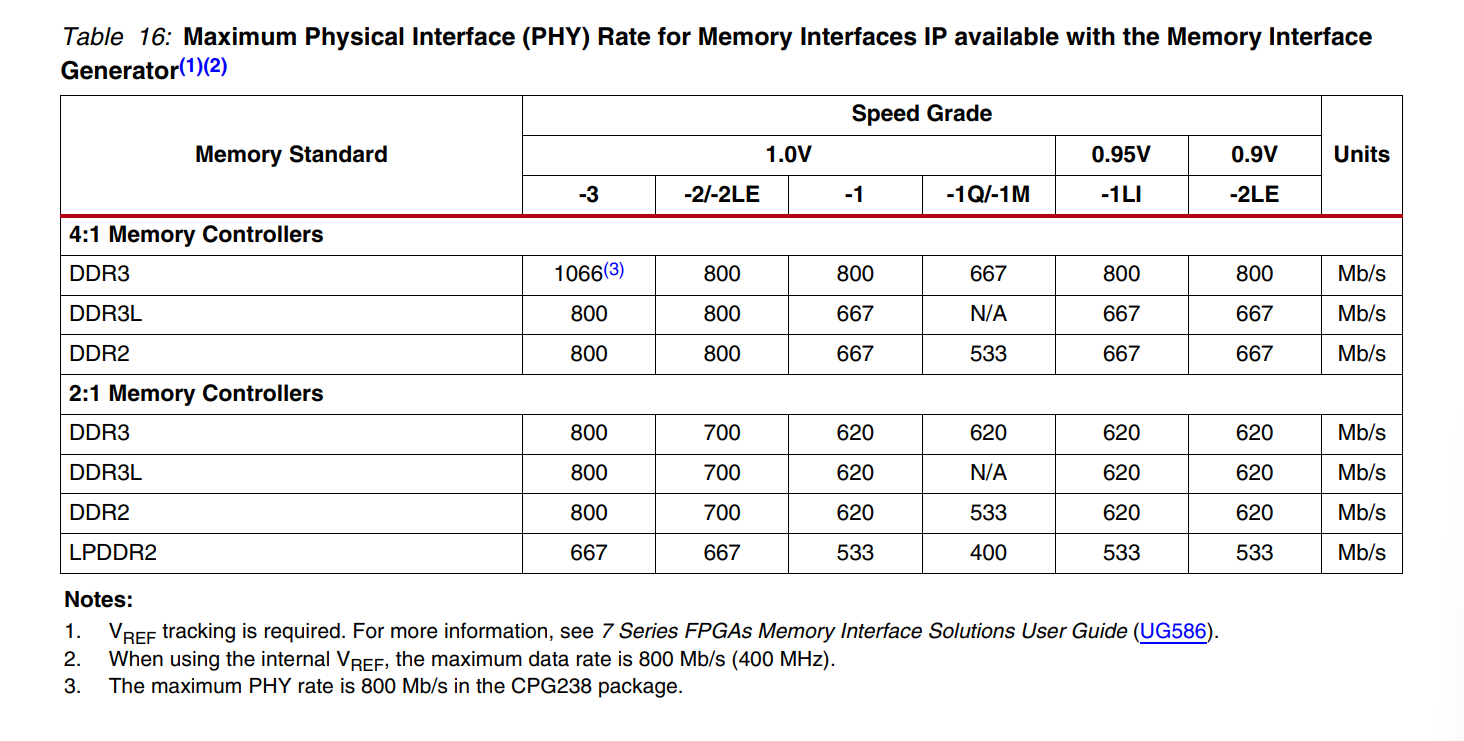

芯片

K7

A7

可参考

基于FPGA的DDR3设计(2)DDR3各时钟频率及带宽分析 - 知乎 (zhihu.com)

1.DDR3器件的手册。

2.开发板芯片的手册

器件名称:MT41J128M16JT-125:K

tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz;此处的IO时钟频率也就是DDR3的频率。

器件最大支持800MHZ,其中核心频率200MHZ,工作频率800MHZ。

K7

A7

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1121139.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!