前言

FIFO功能模块分两篇文章,本篇为同步FIFO,另一篇为异步FIFO,传送门:

Verilog功能模块——异步FIFO-CSDN博客

同步FIFO实现起来是异步FIFO的简化版,所以,本博文不再介绍FIFO实现原理,感兴趣的同学可以去看我异步FIFO的文章,基本看懂了异步FIFO,同步FIFO自然就懂了。

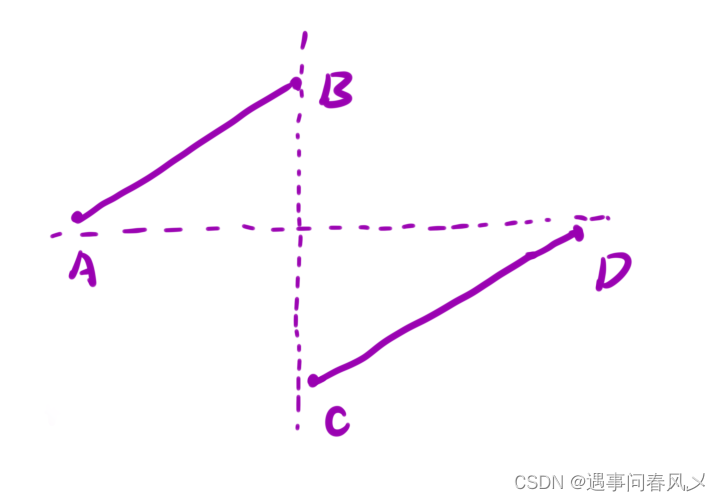

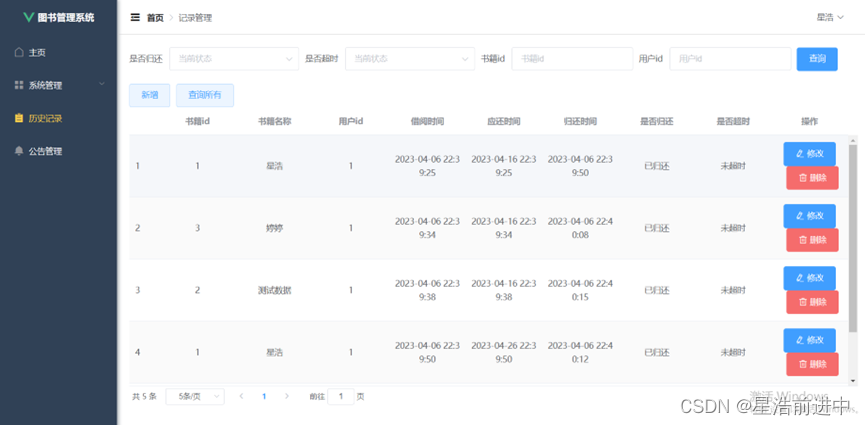

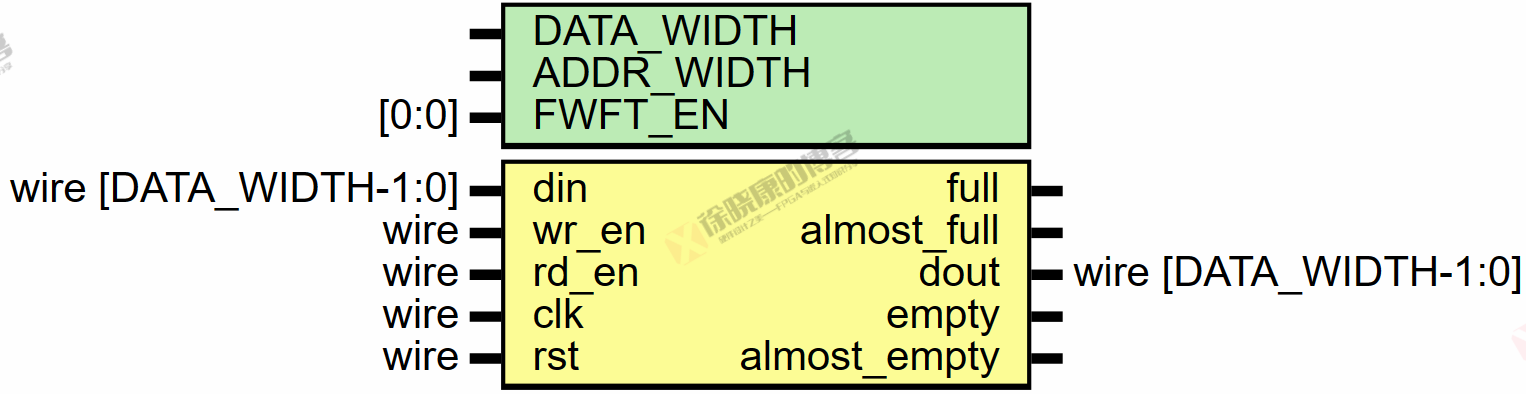

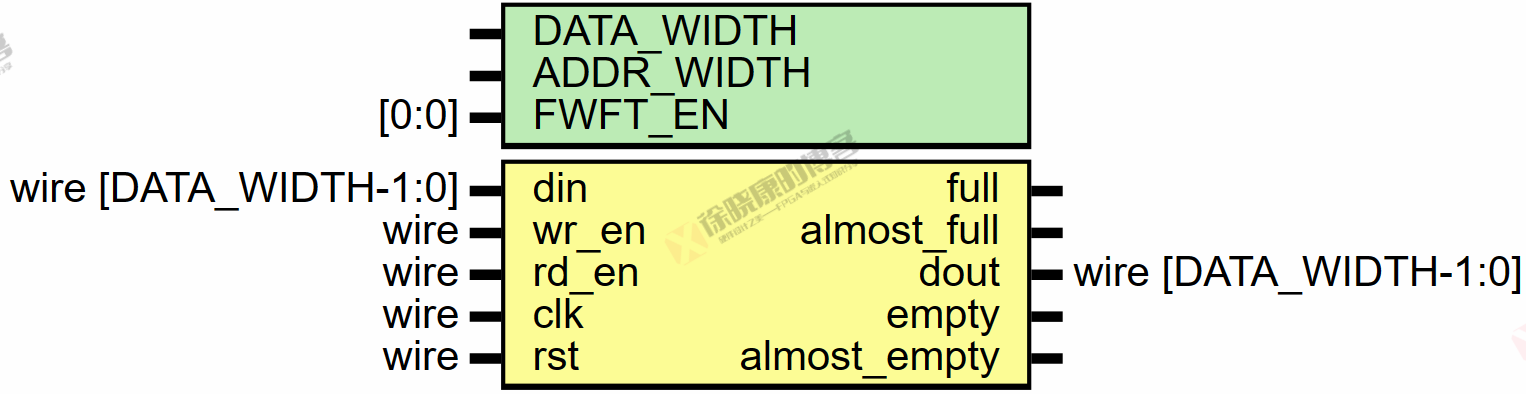

二. 模块功能框图与信号说明

信号说明:

| 分类 | 信号名称 | 输入/输出 | 说明 |

|---|---|---|---|

| 参数 | DATA_WIDTH | – | 数据位宽 |

| ADDR_WIDTH | – | 地址位宽,FIFO深度=2**ADDR_WIDTH | |

| FWFT_EN | – | First word fall-through输出模式使能,高电平有效 | |

| FIFO写端口 | din | input | FIFO数据输入 |

| wr_en | input | FIFO写使能 | |

| full | output | FIFO满信号 | |

| almost_full | output | FIFO快满信号,FIFO剩余容量<=1时置高 | |

| FIFO读端口 | dout | output | FIFO数据输出 |

| rd_en | input | FIFO读使能 | |

| empty | output | FIFO空信号 | |

| almost_empty | output | FIFO快空信号,FIFO内数据量<=1时置高 | |

| 时钟与复位 | clk | input | FIFO读时钟 |

| rst | input | FIFO读复位 |

注意:

- 信号的命名与Vivado中的FIFO IP核完全一致

- 复位均为高电平复位,与Vivado中的FIFO IP核保持一致

- 复位为异步复位

- FIFO深度通过ADDR_WIDTH来设置,所以FIFO的深度必然是2的指数,如2、4、8、16等

三. 部分代码展示

//++ 生成读写指针 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

reg [ADDR_WIDTH:0] rptr;

always @(posedge clk or posedge rst) begin

if (rst)

rptr <= 0;

else if (rd_en & ~empty)

rptr <= rptr + 1'b1;

end

reg [ADDR_WIDTH:0] wptr;

always @(posedge clk or posedge rst) begin

if (rst)

wptr <= 0;

else if (wr_en & ~full)

wptr <= wptr + 1'b1;

end

wire [ADDR_WIDTH-1:0] raddr = rptr[ADDR_WIDTH-1:0];

wire [ADDR_WIDTH-1:0] waddr = wptr[ADDR_WIDTH-1:0];

wire [ADDR_WIDTH:0] rptr_p1 = rptr + 1'b1;

wire [ADDR_WIDTH:0] wptr_p1 = wptr + 1'b1;

//-- 生成读写指针 ------------------------------------------------------------

//++ 生成empty与almost_empty信号 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

always @(*) begin

if (rst)

empty <= 1'b1;

else if (rptr == wptr)

empty <= 1'b1;

else

empty <= 1'b0;

end

always @(*) begin

if (rst)

almost_empty <= 1'b1;

else if (rptr_p1 == wptr || empty)

almost_empty <= 1'b1;

else

almost_empty <= 1'b0;

end

//-- 生成empty与almost_empty信号 ------------------------------------------------------------

//++ 生成full与almost_full信号 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

always @(*) begin

if (rst)

full <= 1'b1;

else if ((wptr[ADDR_WIDTH] != rptr[ADDR_WIDTH])

&& (wptr[ADDR_WIDTH-1:0] == rptr[ADDR_WIDTH-1:0])

)

full <= 1'b1;

else

full <= 1'b0;

end

always @(*) begin

if (rst)

almost_full <= 1'b1;

else if (((wptr_p1[ADDR_WIDTH] != rptr[ADDR_WIDTH])

&& (wptr_p1[ADDR_WIDTH-1:0] == rptr[ADDR_WIDTH-1:0])

)

|| full

)

almost_full <= 1'b1;

else

almost_full <= 1'b0;

end

//-- 生成full与almost_full信号 ------------------------------------------------------------

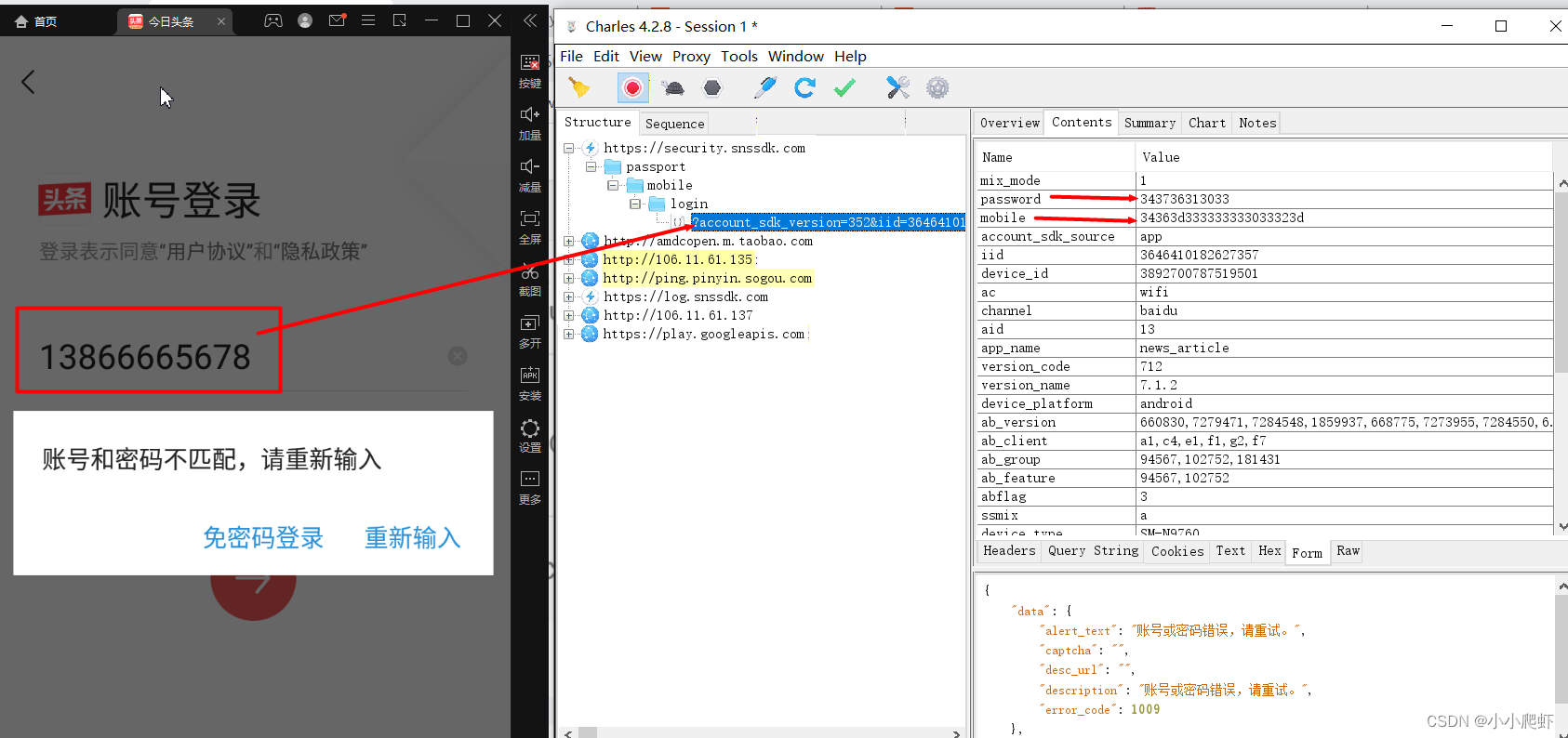

三. 功能仿真

比较以下情形中的fifo行为是否与FIFO IP核一致,

情形一:单次写单次读

情形二:写满后再读空

情形三:在读的过程中写,在写的过程中读

判断模块功能正常的依据:

- 写入数据是否按顺序正常读出

- 空信号和满信号是否正常输出。

为方便比较,编写了顶层文件,实例化了FIFO IP核与自编模块,部分代码如下:

vivado_sync_fifo vivado_sync_fifo_u0 (

.clk (clk ), // input wire clk

.rst (rst ), // input wire rst

.din (din ), // input wire [7 : 0] din

.wr_en (wr_en ), // input wire wr_en

.rd_en (rd_en ), // input wire rd_en

.dout (vivado_fifo_dout ), // output wire [7: 0] dout

.full (vivado_fifo_full ), // output wire full

.almost_full (vivado_fifo_almost_full ), // output wire almost_full

.empty (vivado_fifo_empty ), // output wire empty

.almost_empty (vivado_fifo_almost_empty)// output wire almost_empty

);

syncFIFO # (

.DATA_WIDTH (DATA_WIDTH),

.ADDR_WIDTH (ADDR_WIDTH),

.FWFT_EN (FWFT_EN )

) syncFIFO_inst (

.din (din ),

.wr_en (wr_en ),

.full (full ),

.almost_full (almost_full ),

.dout (dout ),

.rd_en (rd_en ),

.empty (empty ),

.almost_empty (almost_empty),

.clk (clk ),

.rst (rst )

);

testbench部分代码如下:

// 生成时钟

localparam CLKT = 2;

initial begin

clk = 0;

forever #(CLKT / 2) clk = ~clk;

end

// 读写使能控制

initial begin

rst = 1;

#(CLKT * 2)

rst = 0;

wr_en = 0;

rd_en = 0;

#(CLKT * 2)

wait(~full && ~vivado_fifo_full); // 两个FIFO都从复位态恢复时开始写

// 写入一个数据

wr_en = 1;

#(CLKT * 1)

wr_en = 0;

// 读出一个数据

wait(~empty && ~vivado_fifo_empty);// 两个FIFO都非空时开始读,比较读数据和empty信号是否有差异

rd_en = 1;

#(CLKT * 1)

rd_en = 0;

// 写满

wr_en = 1;

wait(full && vivado_fifo_full); // 两个FIFO都满时停止写,如果两者不同时满,则先满的一方会有写满的情况发生,但对功能无影响

// vivado FIFO IP在FWFT模式时, 设定深度16时实际深度为17, 但仿真显示full会在写入15个数据后置高, 过几个时钟后后拉低,

// 再写入一个数据, full又置高; 然后过几个时钟又拉低, 再写入一个数据置高, 如此才能写入17个数据

// 所以这里多等待12个wclk周期, 就是为了能真正写满vivado FWFT FIFO

#(CLKT * 12)

wr_en = 0;

// 读空

wait(~empty && ~vivado_fifo_empty);

rd_en = 1;

wait(empty && vivado_fifo_empty); // 两个FIFO都空时停止读,如果两者不同时空,则先空的一方会有读空的情况发生,但对功能无影响

rd_en = 0;

#(CLKT * 10)

$stop;

end

// 使用以下代码时,先注释掉上面的读写使能控制initial

// 同时读写

// initial begin

// #(CLKT * 30)

// $stop;

// end

// assign wr_en = ~full || ~vivado_fifo_full; // 未满就一直写

// assign rd_en = ~empty || ~vivado_fifo_empty; // 未空就一直读

always @(posedge clk) begin

if (rst)

din <= 0;

else if (wr_en && ~full && ~vivado_fifo_full)

din <= din + 1;

end

endmodule

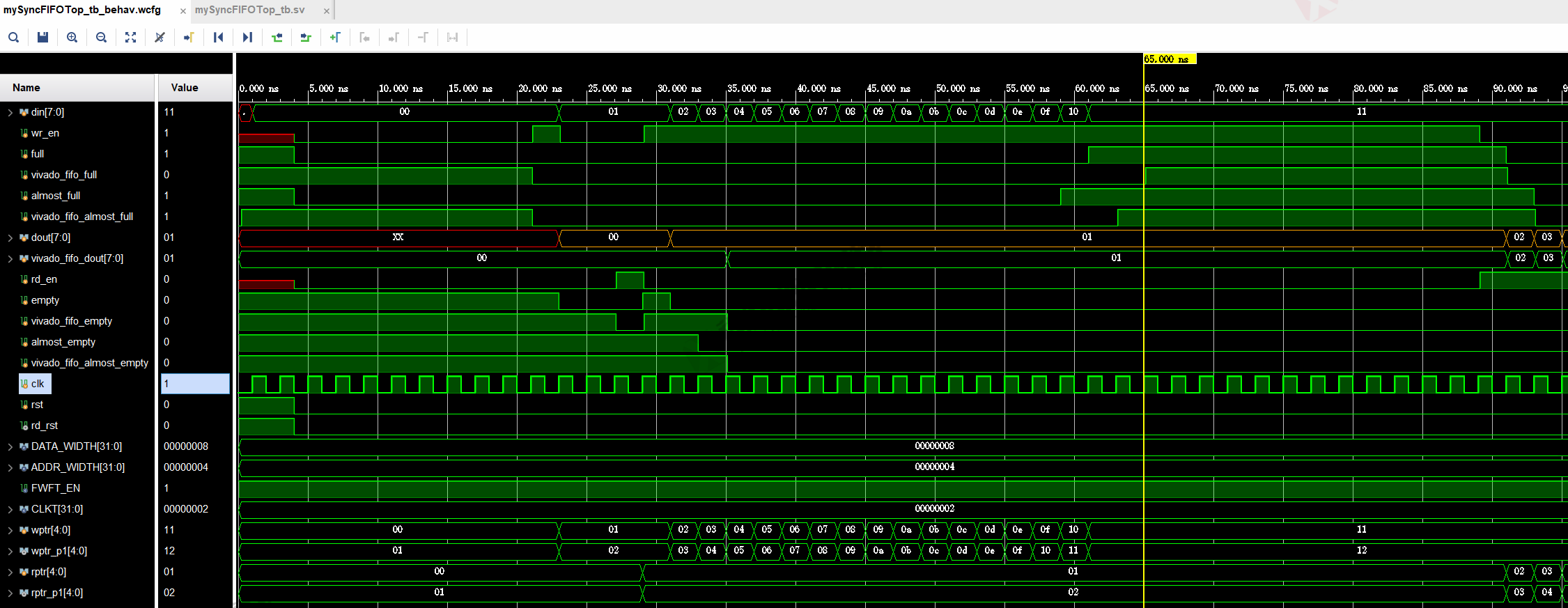

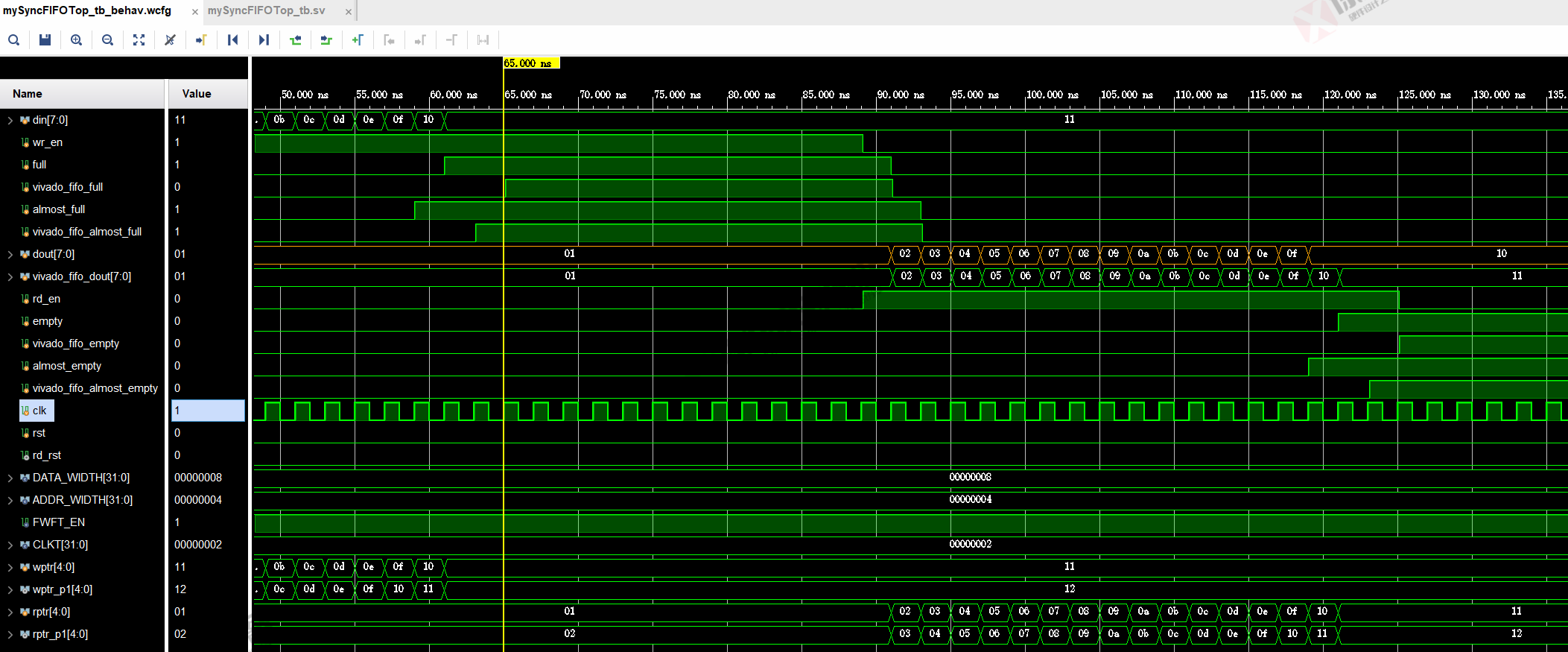

8bit,16深度,FWFT FIFO仿真,波形如下:

可以看到模块输出的自编fifo与vivado fwft fifo的写端口和读端口行为是一致的,只是可能会超前或滞后一定的clk周期。

可以看到empty拉低时,数据已经有效了,所以自编模块实现了FWFT功能,Vivado FIFO的实际深度为17,所以它多读出了一个数据,空信号更晚拉高。

因篇幅问题,其它条件下的仿真不再展示,感兴趣的同学可通过更改testbench自行验证。

- FWFT_EN改为0,注意同步修改Vivado FIFO的配置

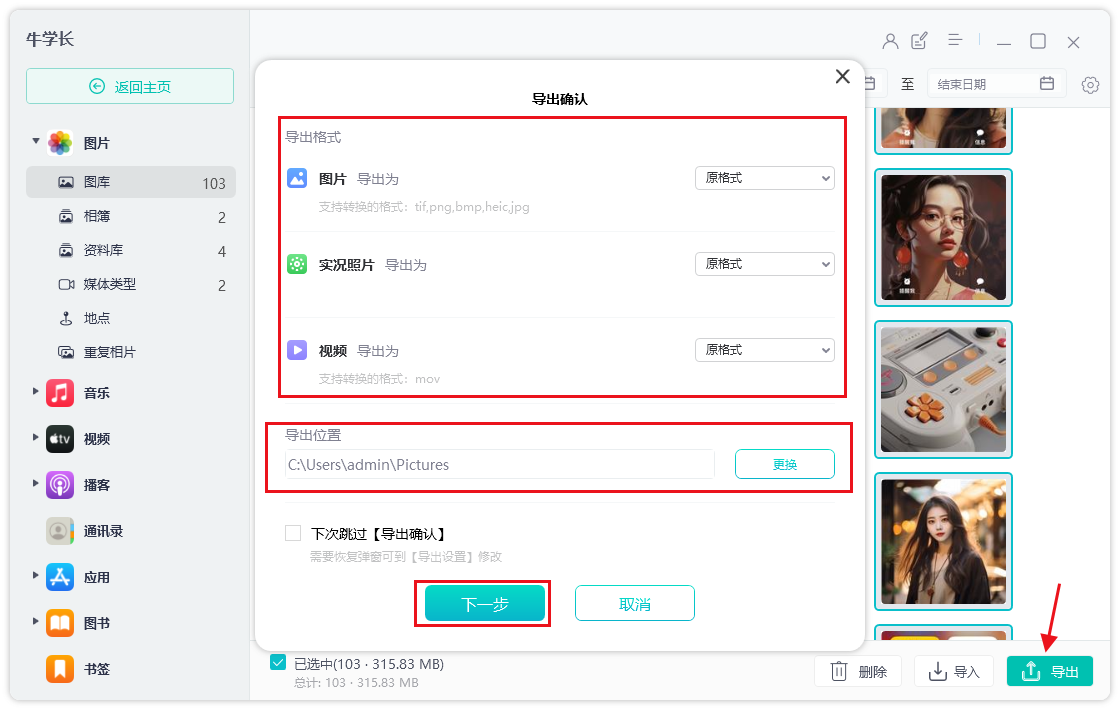

四. 工程分享

Verilog功能模块——同步FIFO,Vivado 2021.2工程。

欢迎大家关注我的公众号:徐晓康的博客,回复以下四位数字获取。

8302

建议复制过去不会码错字!

或者在我的码云仓库获取,传送门:

徐晓康/Verilog功能模块 - 码云 - 开源中国 (gitee.com)

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。

![2023年中国电子白板市场规模、竞争格局及应用领域市场结构[图]](https://img-blog.csdnimg.cn/img_convert/30f59a81dfea2739b7e6d0461e430b05.png)