文章目录

- 前言

- 一、PMOS和NMOS

- 1、NMOS

- 2、PMOS

- 3、增强型和耗尽型

- 4、两者面积大小

- 二、CMOS门电路

- 1、非门

- 2、与非门

- 3、或非门

- 4、线与逻辑

- 5、CMOS传输门

- 6、三态门

- 三、TTL电路

- 四、TTL电路 VS CMOS电路

- 五、数字电平

- 六、使用CMOS电路实现逻辑函数

- 1、上拉网络 PUN

- 2、下拉网络 PDN

- 3、实现逻辑表达式

前言

2023.9.7

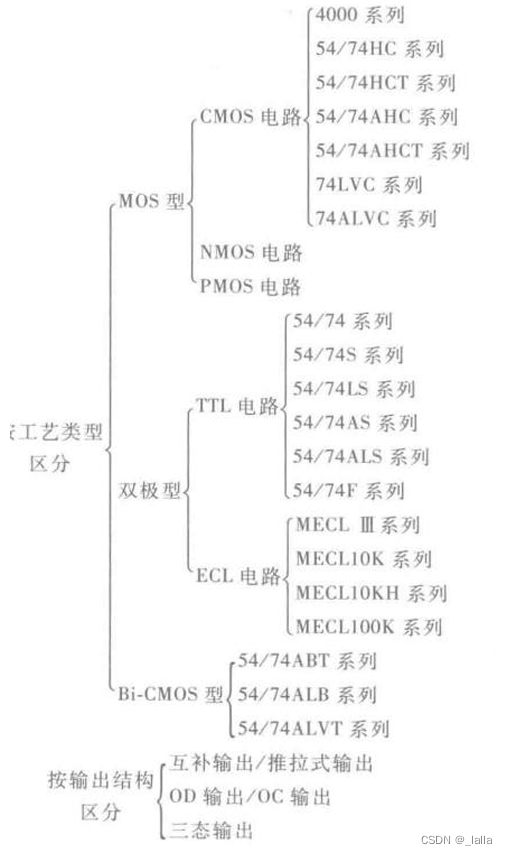

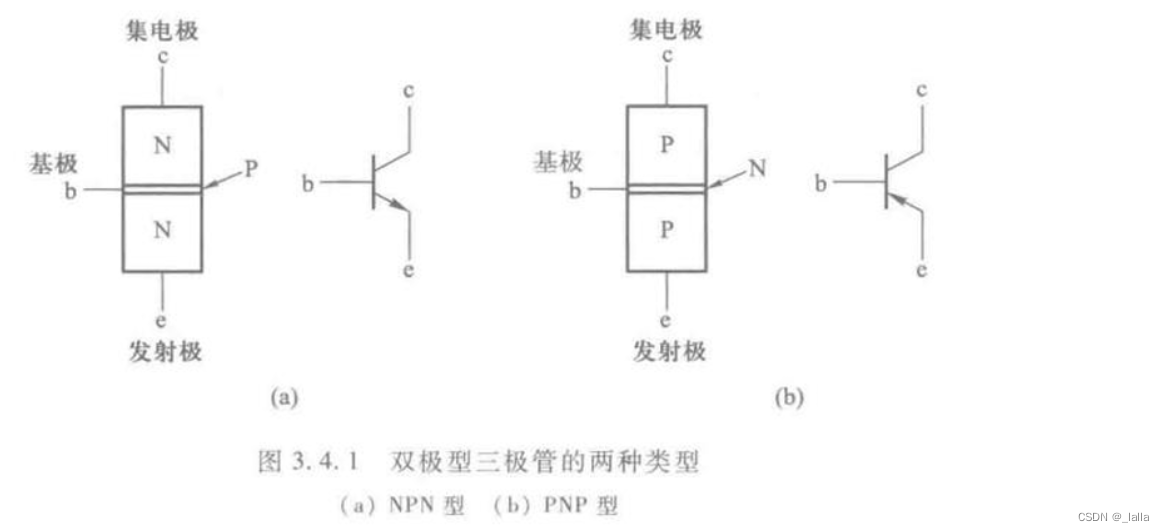

一、PMOS和NMOS

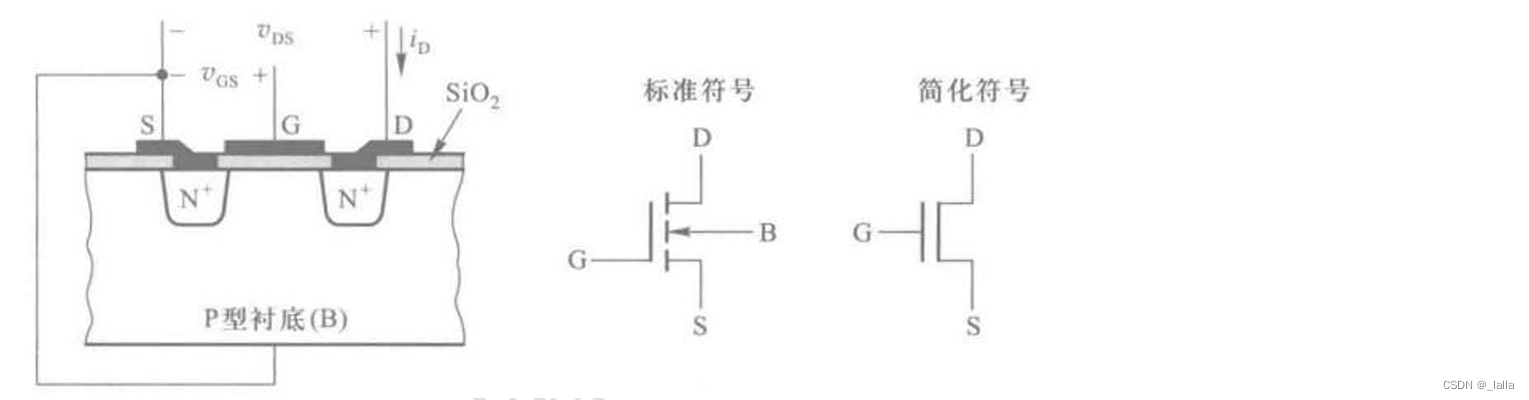

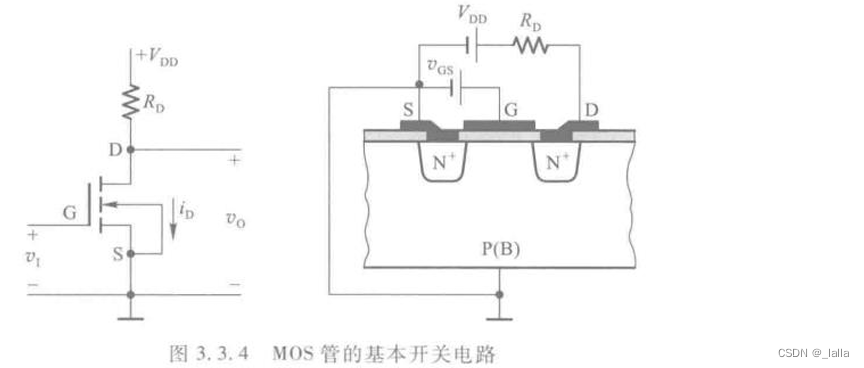

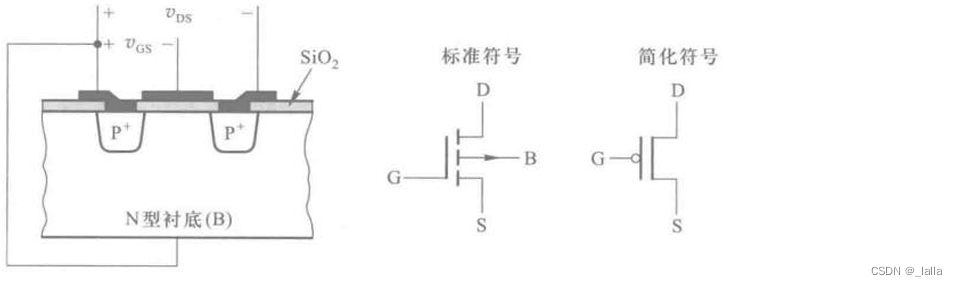

1、NMOS

截止区:VGS<VGS(th)

放大区、恒流区

2、PMOS

缺点:使用的是负电压电源,不便于和TTL电路连接,使用的少

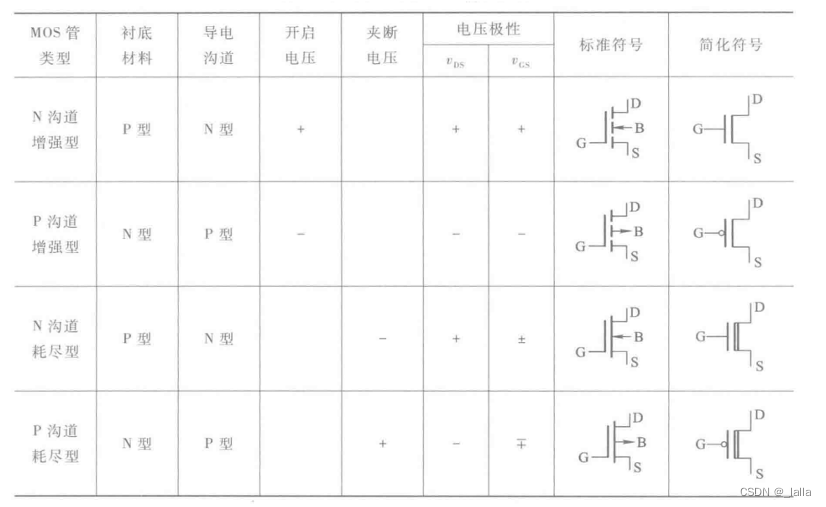

3、增强型和耗尽型

耗尽型:在栅极下面的二氧化硅绝缘层里面掺杂了正离子(NMOS),使得正常情况下导电沟道已经存在,需要施加负电压使得导电沟道消失

4、两者面积大小

如果把MOS管的面积增加,那么流过mos管的电流更大,速度也更快,驱动电路更强

笔试题1:PMOS和NMOS哪个面积更大

二、CMOS门电路

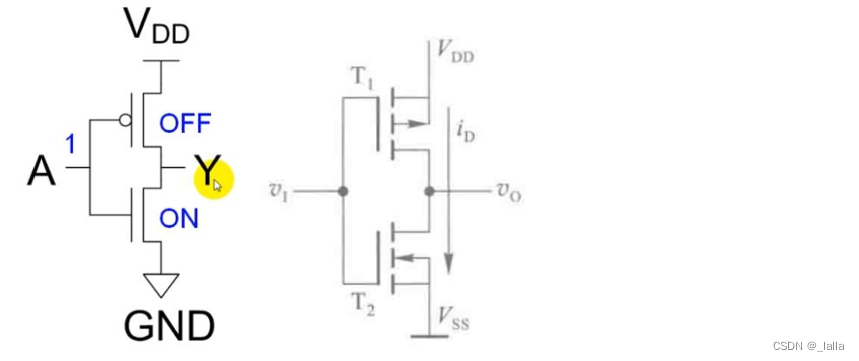

1、非门

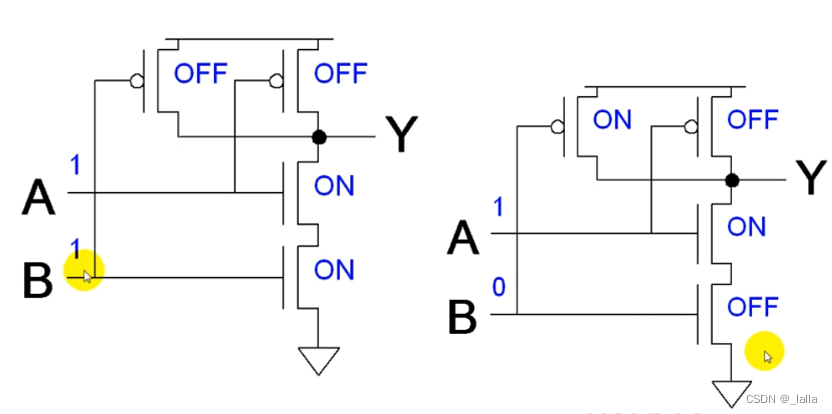

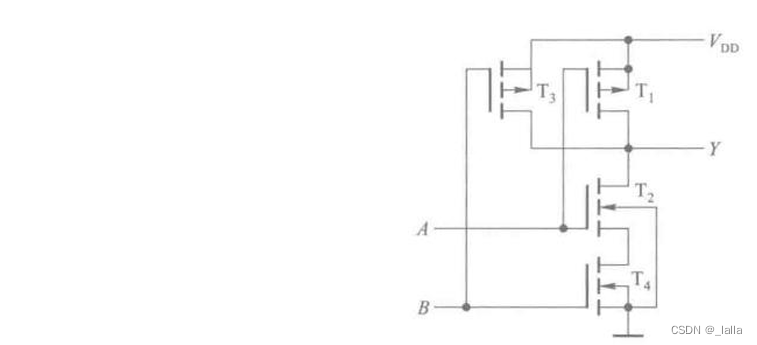

2、与非门

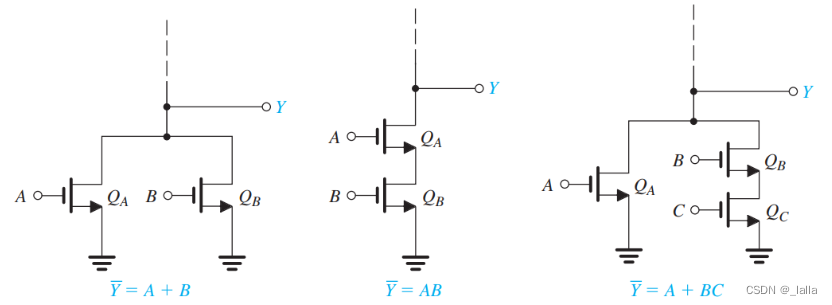

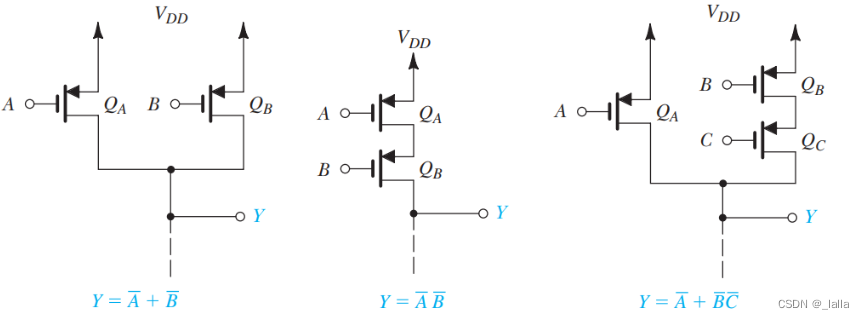

n输入的与非门:n个pmos并联 + n个nmos串联

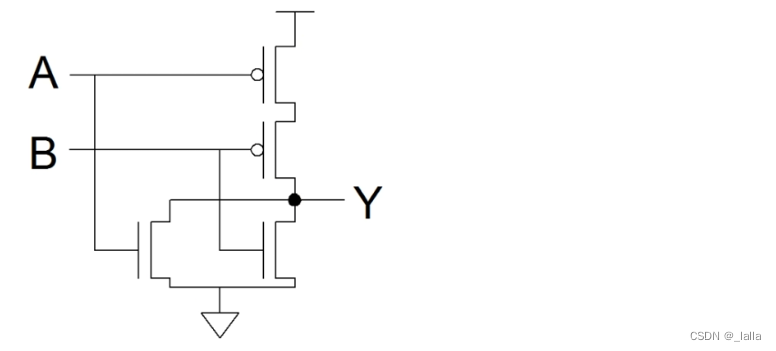

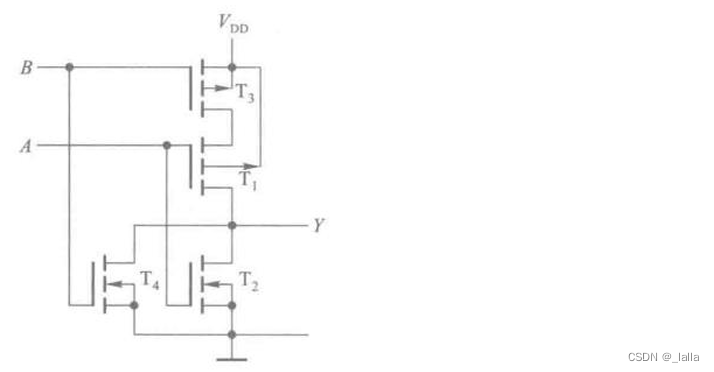

3、或非门

n输入或非门:n个pmos串联 + n个nmos并联

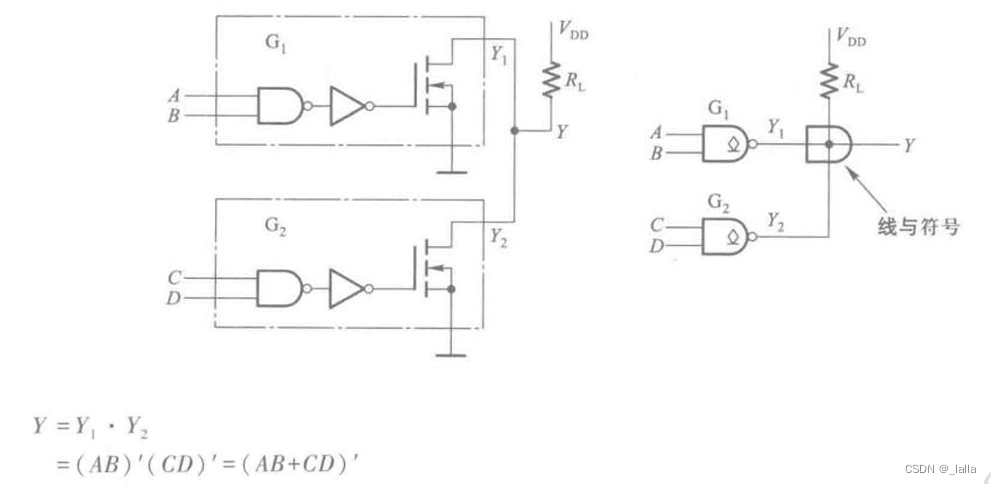

4、线与逻辑

线与:多个信号相连实现与的功能

上拉电阻:防止电流过大

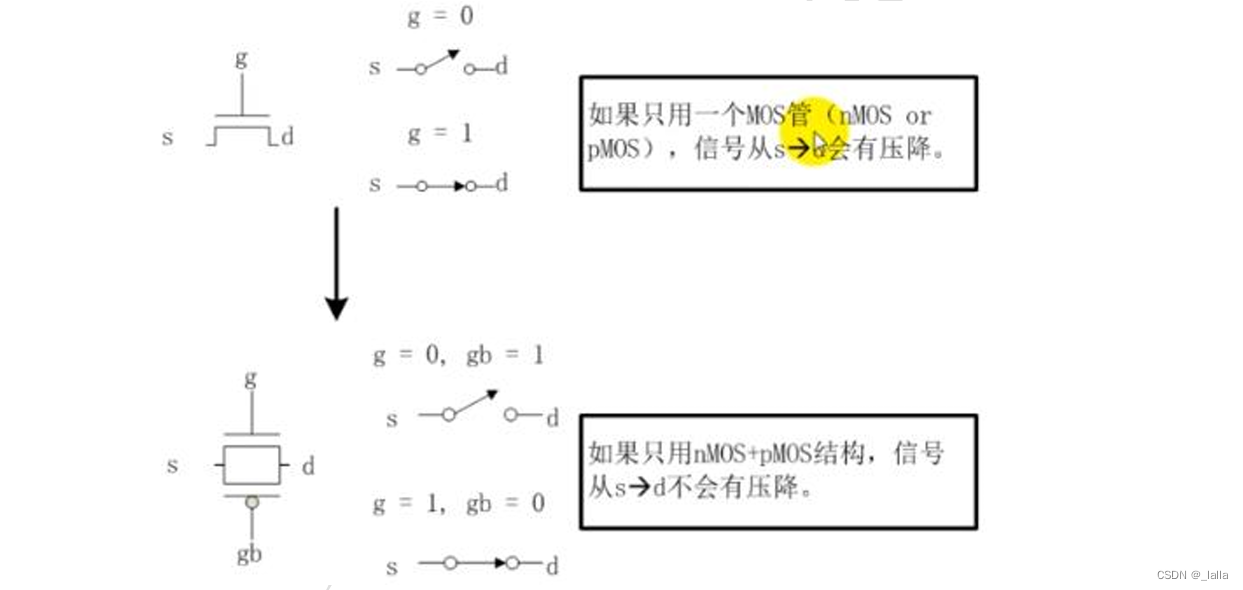

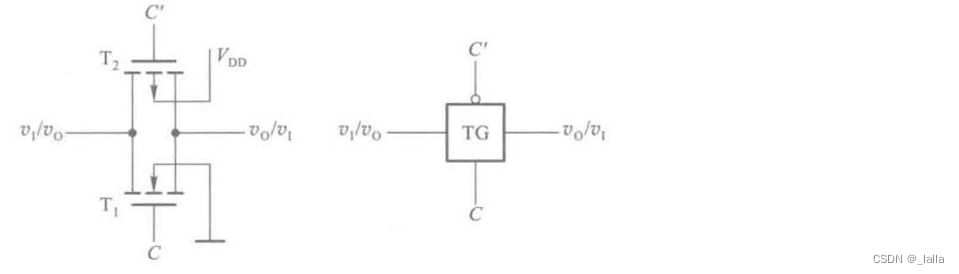

5、CMOS传输门

只用一个mos管:会存在压降

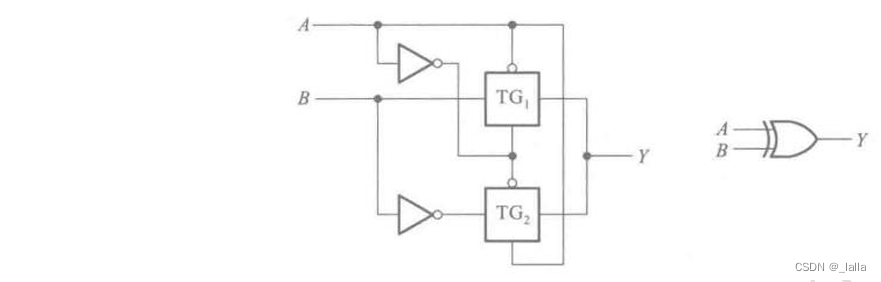

用非门和CMOS传输门实现异或电路

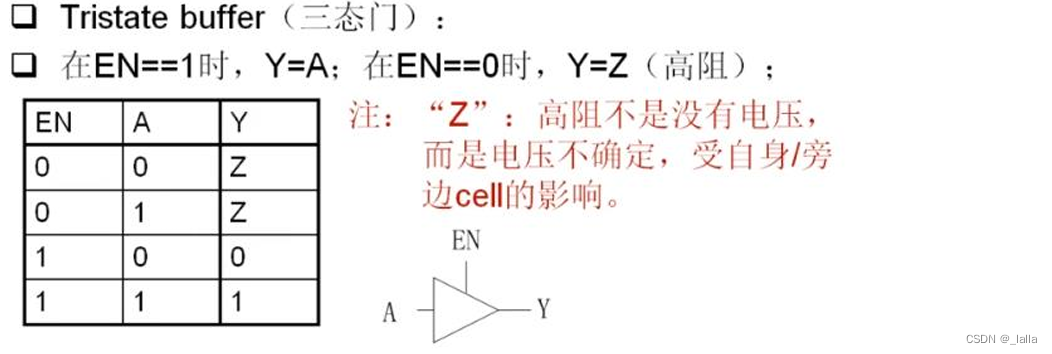

6、三态门

三态门:既不是0,也不是1,电阻很大,相当于开路

always@(din or en)begin

if(en)

dout = din;

else

dout = 1'bz;

end

//或者assign赋值

assign dout = en ? din : 1'bz;

三、TTL电路

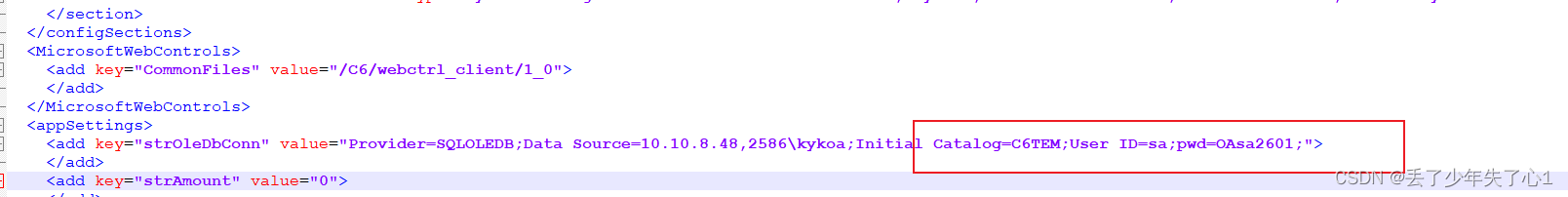

CMOS输出接口可以直接连TTL电路

TTL电路需要加上拉电阻接到CMOS端口

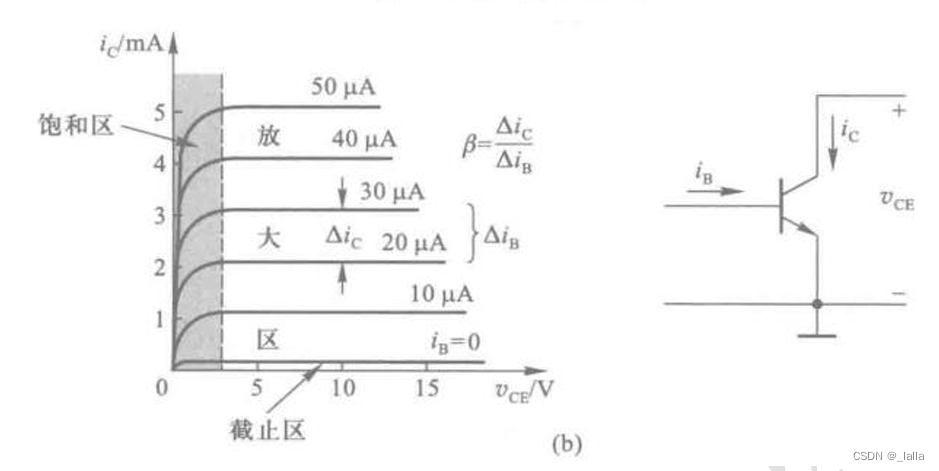

放大区:ic随着iB正比增加,系数为放大因子

饱和区:ic不再随着ib比例增加,逐渐趋于饱和

截止区:ic几乎为零

四、TTL电路 VS CMOS电路

| CMOS | TTL |

|---|---|

| 电压控器件 | 电流控器件 |

| 功耗低 | 功耗高 |

| 速度慢 | 速度快 |

| 12V、5V | 0.3~3.6V |

五、数字电平

Voh:保证输出为高电平的最小输出电压

Vih:保证输入为高电平的最小输入电压

Vil:保证输入为低电平的最大输入电压

Vol:保证输出为高电平的最小输出电压

大小关系:Voh > Vih > Vth > Vil > Vol

六、使用CMOS电路实现逻辑函数

参考链接:CMOS逻辑门电路

组成:NMOS下拉晶体管 + PMOS上拉晶体管组成

两个网络在变量的控制下做出相反的行为

1、上拉网络 PUN

可以等效为

Y = ~(A + B);

Y = ~(AB);

Y = ~(A + BC);

2、下拉网络 PDN

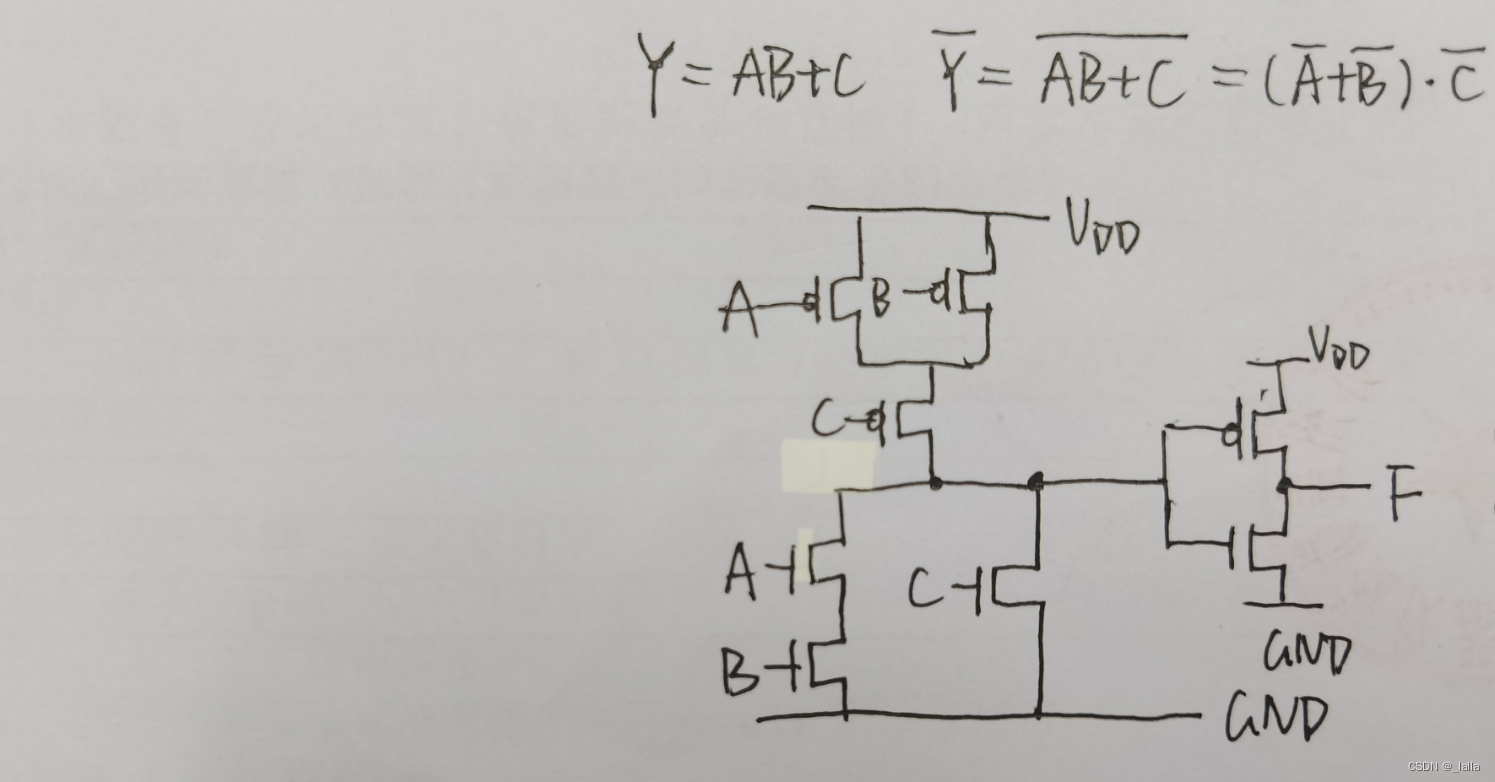

3、实现逻辑表达式

3.1 下面表达式是整体反相,因此可以用PDN来表示

PUN是变量反相

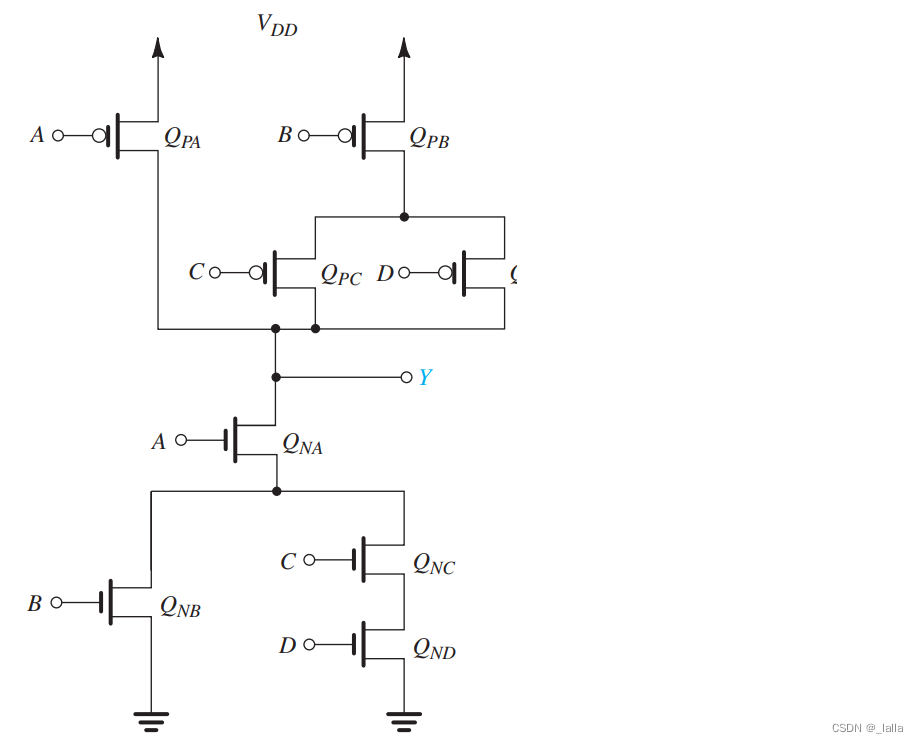

CMOS电路如下图所示:

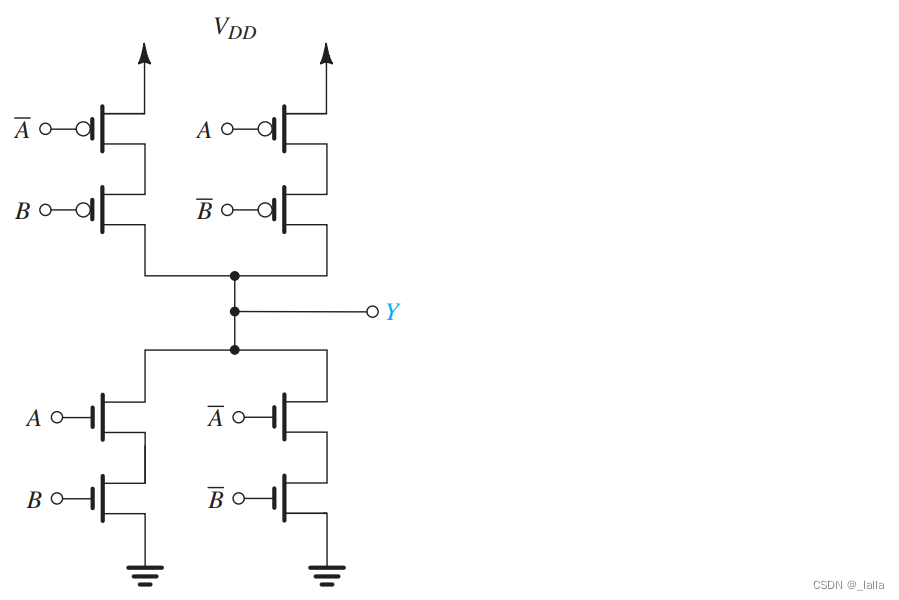

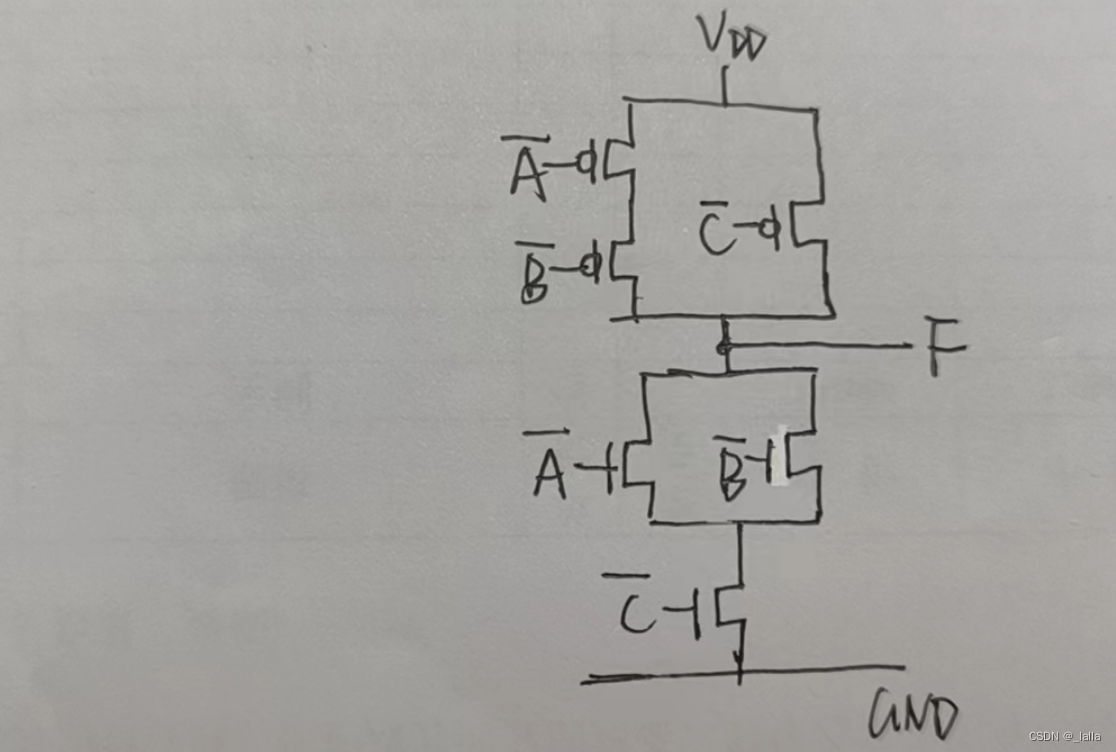

3.2 异或门实现

分析:异或门中间既不是整体取反,也不是每个都是反变量,而是有原变量和反变量夹杂在一起

CMOS电路如下图所示:

有两个变量的输入需要增加非门,因此总共需要12个mos管实现

注意:下面的电路实现不再是对偶网络,网络对偶并不是必要条件

3.3 笔试题

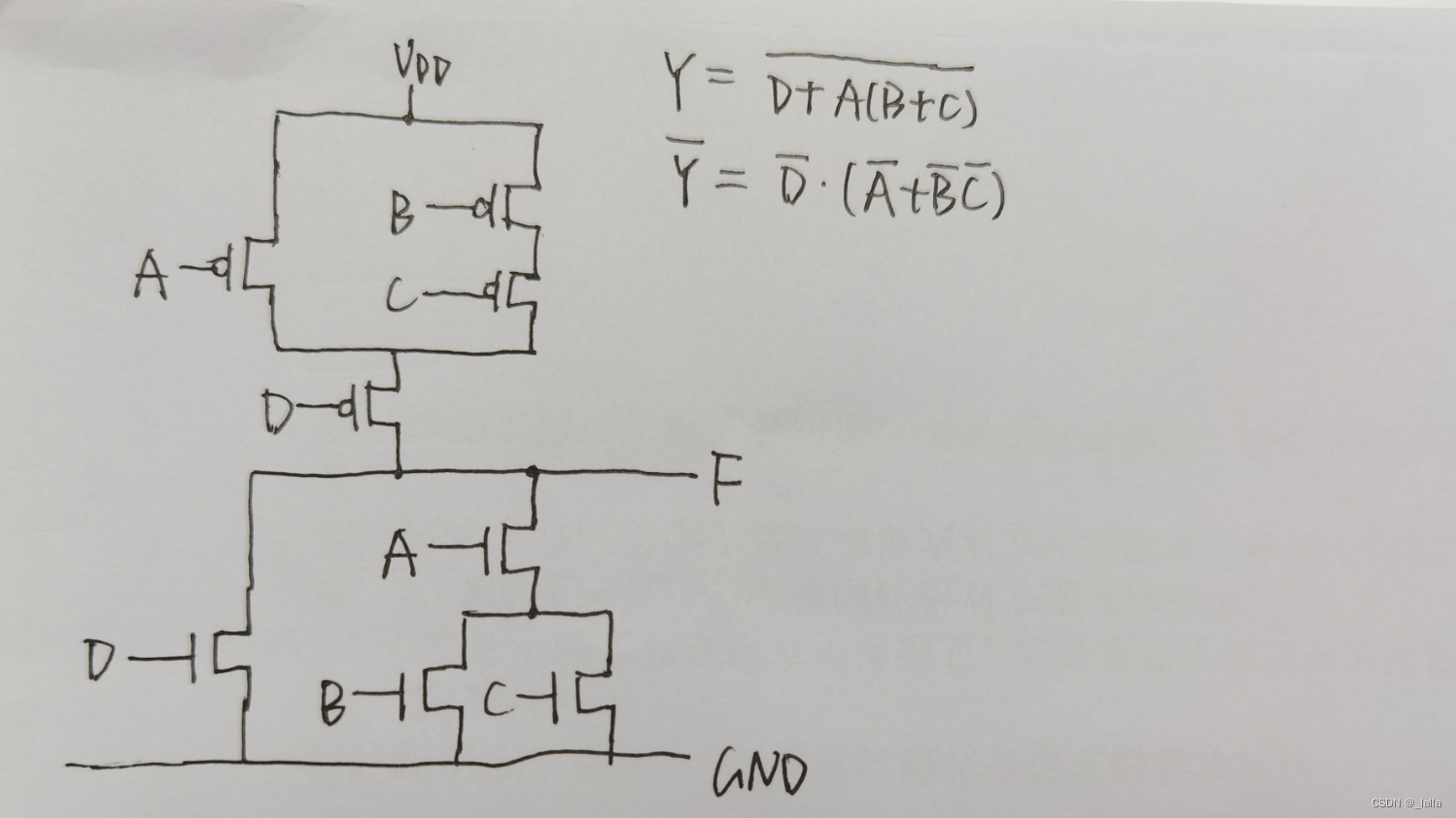

Y = ~(D + A(B + C)) //这个和上面的3.1类似,属于整体反相的那种

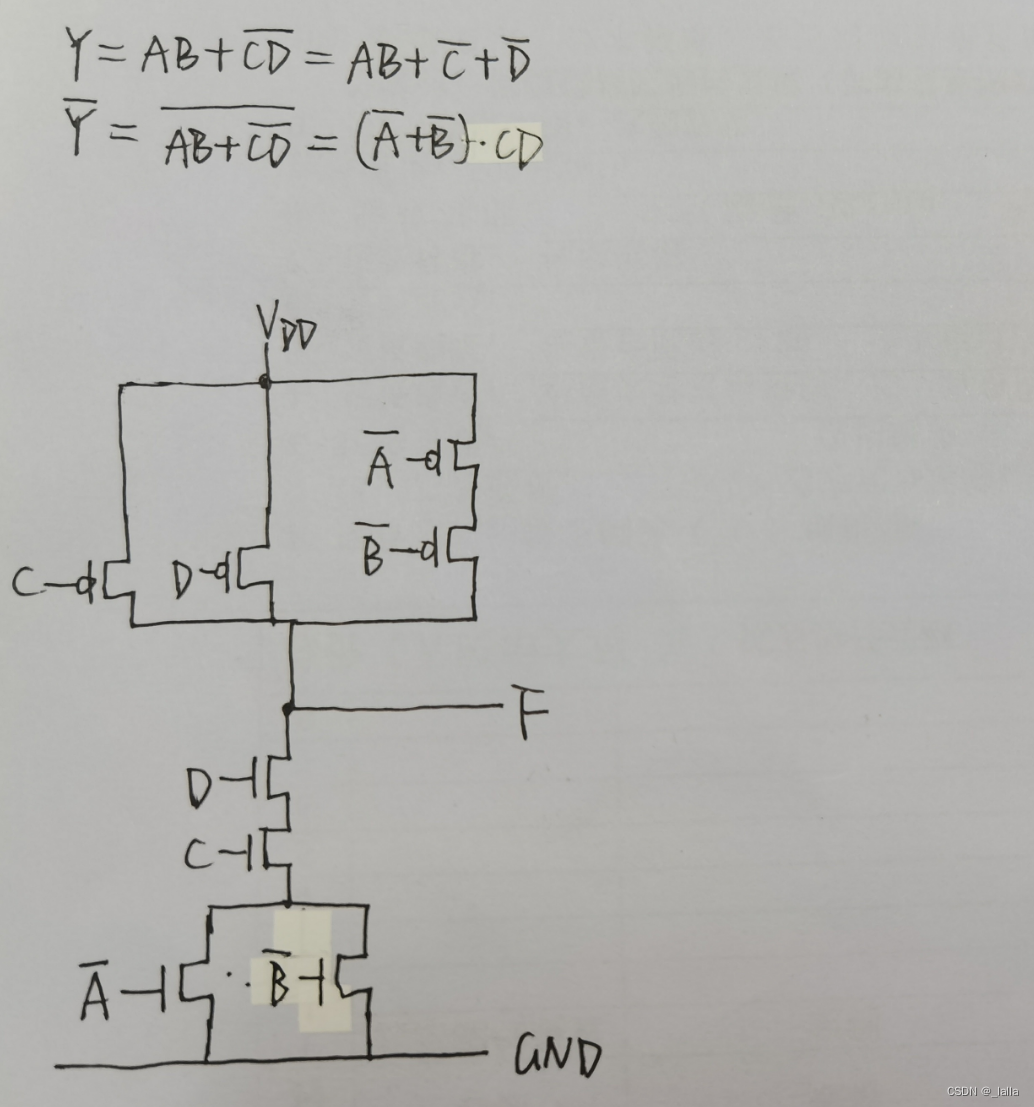

Y = AB + ~(CD)

Y = AB + C

两种方式实现:

第一种当作整体取反,最后加个非门,这样实现门电路最少

第二种 直接根据表达式分别写出上拉和下拉网络

总结:除了同时包含原变量和反变量的时候,网络不是对称的,下面这几个都还是对偶网络