文章目录

- 前言

- 一、QuestaSim使用方法

- 1、编译vlog

- 2、映射vmap

- 3、仿真vism

- 4、ifndef和define(常用)

- 5、QuestaSim的仿真界面

- 6、完整QuestaSim仿真——TCL脚本

前言

2023.8.29

一、QuestaSim使用方法

1、编译vlog

vlog:questasim的编译命令

-sv:指示vlog按照systemverilog语法进行编译,编译后会生成一个库,由于以上没有指定,缺省的库名就是work。如果要显式地指定不同的库名,可以追加选项“-work libname”。

2、映射vmap

映射逻辑库名到指定的目录

3、仿真vism

vsim:仿真的命令

-c:以命令行的形式执行,不开启图形化界面

-vopt:进行优化

-novopt:不进行优化,在调试时通常使用这个选项,这个会使得仿真速度慢一些

-classdebug:方便调试。仿真后,view的class browser中,class tree可以清晰的看到各个类的继承关系

-coverage:在仿真时产生代码覆盖率数据,功能覆盖率数据默认生成,与此项无关

-solvefaileddebug :使能输出随机化失败等更多调试信息

+UVM_TESTNAME=: 需要根据代码中不同的test,来决定仿真运行哪一个test,在top文件中则只需要启动run_test( )函数

-sv_seed:随机化种子,可以指定,-sv_seed 0;不指定,-sv_seed random;

-quiet:关闭loading信息,不显示

-l:输出仿真的log文件

-do :开始仿真后运行tcl脚本(控制文件)

-L:加载所需要的仿真库

-quiet:关闭loading的信息

vsim -c -novopt -sv_seed $SEED -l sim.log +TESTNAME=case1

4、ifndef和define(常用)

在文件开头和尾部加入如下,防止代码被重复编译

ifndef:编译命令,是if not defined的缩写,主要是根据其后的宏是否存在于当前编译空间来进行分支选择。第一次会执行下面的define,执行顶层时,该宏已经存在编译空间中,所以不会被重复编译

`ifndef MY_TRANSACTION__SV

`define MY_TRANSACTION__SV

//my_codes

`endif

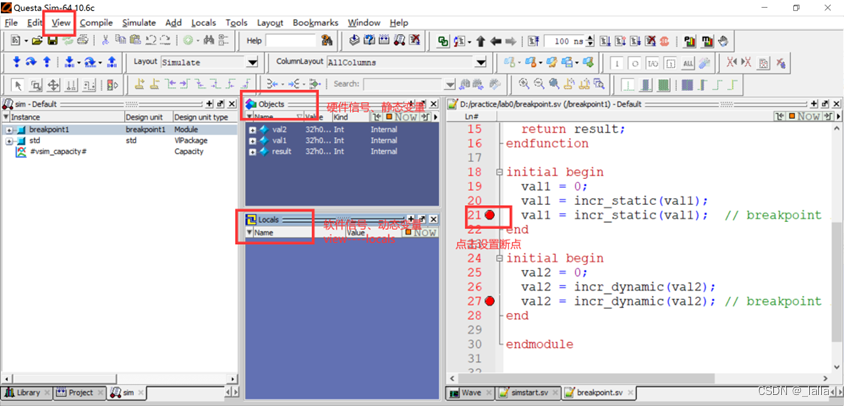

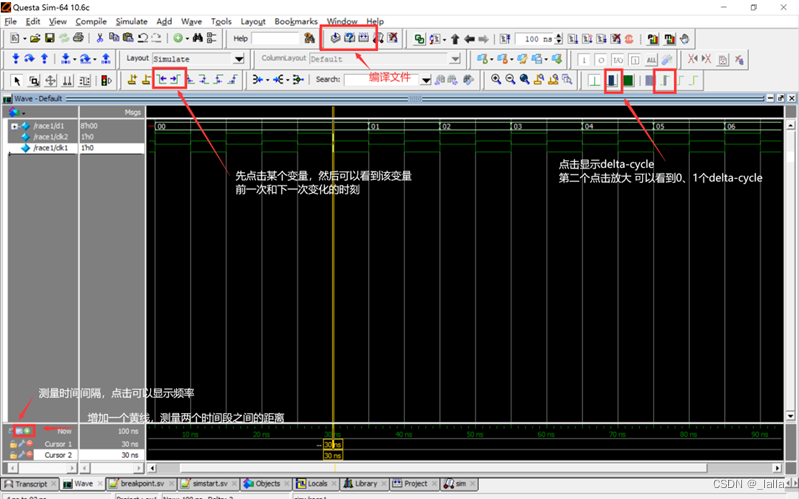

5、QuestaSim的仿真界面

6、完整QuestaSim仿真——TCL脚本

这里用的是do文件,直接在命令行执行即可

do sim.do

quit -sim //退出当前的仿真

clear //清除

vlib ./lib //创建库到一个文件夹,默认库的名字为work

vlib ./lib/work

vmap work ./lib/work //映射逻辑库到物理目录,这个库名称可以修改

vlog -sv -work work ./rtl/adder.v //编译设计文件,把编译文件放到这个目录下

vsim -novopt -c work.adder_top -cover -sv_seed +TIMESCALE=$testname -l xx.log //仿真,adder_top为顶层的名字

log -r /*

run -all

![省级智慧农业大数据平台项目规划建设方案[195页Word]](https://img-blog.csdnimg.cn/img_convert/efb3c31ad5ad8afa95e1c4d97bea4649.jpeg)