目录

- 1、英飞凌-AURIX-TC3XX 片上总线通信架构

- 1.1、SRI-系统资源互连结构

- 1.1.1、SRI简介

- 1.1.2、SRI 的特征:

- 1.1.3、SRI 结构相比于前一代产品主要的区别:

- 1.1.4、SRI Crossbar 点对点连接机制

- 1.1.5、SRI主机和SRI从机的连接情况

- 1.2、系统外设总线

- 1.3、BBB-系统骨干总线

1、英飞凌-AURIX-TC3XX 片上总线通信架构

AURIX 2G 系列单片机的片上通信实验Xbar(Cross Bar Interconnect)系统,基于SRI结构发展而来,具有一下三个独立的片上通信方式:

系统资源互连结构(SRI- System Resource Interconnect Fabric )

系统外设总线(SPB-System Peripheral Bus )

系统骨干总线(BBB- Back Bone Bus)

片上总线通信架构图:

1.1、SRI-系统资源互连结构

1.1.1、SRI简介

SRI结构将TriCore CPUs、DMA模块和其他高带宽请求者连接到高带宽内存和其他资源,用于指令获取和数据访问。SRI结构由一个或多个Crossbar 组成,它可以将SRI域中的所有访问者连接起来,承载着域中SRI主机和SRI从机之间的数据交换的任务。这些 Crossbar 支持单次和突发的数据传输,如果有对各 Crossbar ,则他们通过 S2S桥接器连接。SRI Crossbar 支持不同 SRI-Master 和 SRI-Slave 代理之间的并行处理以及从SRI主机到SRI从机的流水线请求。

1.1.2、SRI 的特征:

支持单个和突发的读取和写事务;

通过原子读取修改写事务;

承载着域中

SRI主机和SRI从机之间的数据交换的任务;针对每个

SRI从属服务器的仲裁器,具有单独的配置;从

SRI主机传输的所有地址和控制信息的EDC(错误检测代码)。

1.1.3、SRI 结构相比于前一代产品主要的区别:

①、现在的总线可以包含一个或多个独立的

Crossbar;②、将

SRI Crossbar仲裁方案简化为两级轮询

连接到同一交叉条的SRI代理(主代理和从代理)形成一个SRI域。AURIX™TC3xx平台家族成员中至少有一个甚至更多的SRI域。例如,TC39xB有三个域:带有4个cpu的域0,带有2个cpu的域1,以及具有ADAS和调试功能的ED 域。S2S桥的特殊之处在于它们存在于两个领域中。由于S2S桥接,所有SRI主机都可以直接寻址(访问)大多数SRI从机,不管主机和从机是否在同一 SRI 域上。S2S 桥是单向的,所以需要在两个SRI 域之间以相反的方向放置两个S2S桥来实现双向功能。它们透明地传输所有的SRI事件类型(无需更改主标记或地址),旨在降低引入网桥连接后两个域之间传输的延迟。

1.1.4、SRI Crossbar 点对点连接机制

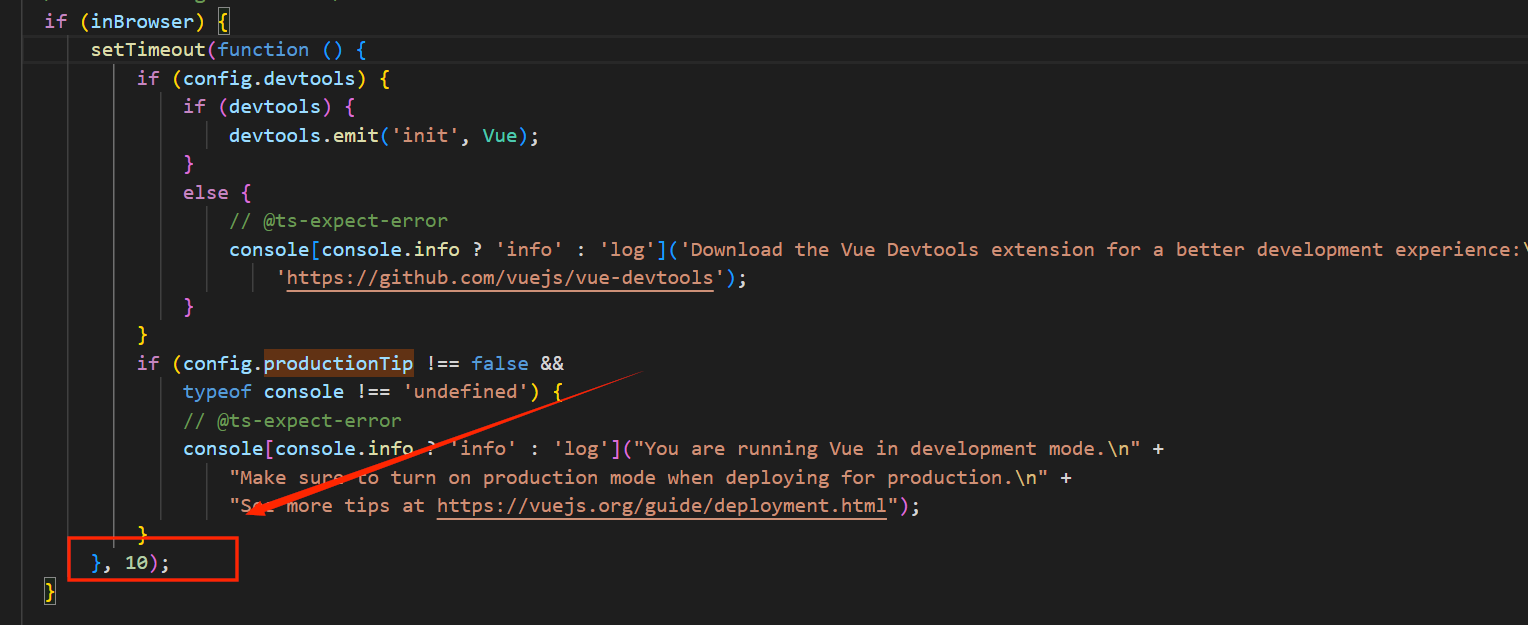

如图 SRI 通信机制:

(MCI表示主机接口用来连接主机、SCI从机接口用来连接从机)

SRI结构包含控制和状态寄存器,他们影响MCI优先级和SCI的控制信息并提供相关的错误消息。每个连接的SRI从机模块和启用的读/写数据通道的基础结构都各自有一个仲裁器,SRI结构将始终至少包含一个提供管理功能的从机,该管理从机允许访问SRI结构控制和状态寄存器,也可以在没有从机处理时进行错误响应。SRI结构提供的仲裁功能允许每个SRI从机对应的SRI主机优先级配置都不同。

1.1.5、SRI主机和SRI从机的连接情况

SRI主机可以同时连接不同的SRI从机,通过优先级和仲裁器进行控制。每个SCI都有一个关联的仲裁器,除了仲裁多个请求之外,还可以进行错误捕获,在设备检测到的错误(某些错误由主机检测到)的情况下捕获事务信息,并通过中断路由器(INT)将状态通知系统,出于系统级诊断和安全考量,错误情况下的SRI错误ID和 TransactionID将被记录。

1.2、系统外设总线

SPB总线将中、低带宽外围设备连接到TriCore CPUs、DMA模块和其他SPB主机上。

SPB主机捕获直接连接到SRI结构,是通过SFI_F2S桥接器访问SRI相关的资源。SFI-F2S桥以FPI协议总线为基础,实现了转发到SRI结构的单向总线桥,该桥支持SPB上的所有FPI协议总线为基础,实现了转发到SRI结构的单向总线桥,该桥支持SPB上的所有FPI传输以及实现它们所需的SRI Fabric 传输,对于传输对象的地址和SPB主机的TAG都是透明的。出于性能原因,从SPB主机到SRI资源的写入操作将设备为Post Write模式,该模式意味着从SPB主机通过SFI_F2S桥进行的写操作时,先在SPB上完成,其结果通过SFI_F2S桥在SRI上自动执行。如果SRI写入操作导致错误,则错误信息不会传递回SPB总线,错误情况将留给接收SRI从机,以按配置中断或发出警报。

1.3、BBB-系统骨干总线

BBB总线将TriCore CPUs、DMA模块和SPB主站与ADAS相关资源连接。SRI主机不会直接连接到BBB,而是通过SFI_S2F桥接器访问BBB连接的资源。SFI_S2F桥是一种单向总线桥,支持SRI结构的所有SRI传输以及实现它们所需的FPI总线传输配置,该桥对于传输对象的地址和SRI主机的TAG都是透明的。出于性能原因,由SRI向BBB传输的资源的写操作设置为Post Write 模式,SFI_S2F桥能够缓冲多个Post Write结果。该模式意味着从SRI主机通过SFI_S2F桥进行的写操作时先在SRI Fabric上完成,并稍后由SFI_S2F在BBB上自动执行。如果写操作在BBB总线上导致错误,则错误信息不会传递回SRI结构,错误状态由BBB的控制逻辑(BBB上的BCU)检测到并按配置中断或发出警报。

![[附源码]Python计算机毕业设计高校图书馆网站Django(程序+LW)](https://img-blog.csdnimg.cn/512a6908ffb040d08dd12031ddba4d99.png)

![[ vulhub漏洞复现篇 ] struts2远程代码执行漏洞s2-052(CVE-2017-9805)](https://img-blog.csdnimg.cn/5cfdbe7e9aee4b9295d73991cdac021a.png)

![[附源码]Node.js计算机毕业设计高校国防教育管理系统Express](https://img-blog.csdnimg.cn/5e63e7e9e6b64a868f4d235cb95bf32d.png)