文章目录

- ARM64 Reset

- 1.1.1 reset 运行级别

- 1.1.2 warm reset 寄存器

- 1.1.3 PSCI Suspend/Resume

ARM64 Reset

ARMv8-A支持两种复位,冷复位和热复位。两者主要区别是冷复位会将debug 功能模块也一同复位,热复位在默认情况则不会复位 debug 功 能模块。

处理器收到复位信号后,依据处理器的具体实现进入所支持的 最高EL(可能是EL3/EL2,甚至EL1),SP寄存器也使用的是对应 EL下的寄存器。

复位后程序起始执行地址是预先定义的,直接从这个预先定义的地址处开始执行。RVBAR_ELx 寄存器保存着这个预先定义的起始执行地址。

1.1.1 reset 运行级别

Reset 时 PE 进入最高的异常级别,运行状态

Reset后最高异常级别可以选用任何一种运行状态cold reset由输入信号配置,warm reset由RMR_ELx.AA64配置- 如果

reset后最高异常级别选用A64,则:- 选用

SP_ELx; - Reset向量的执行地址由厂商定义,

RVBAR持有向量地址。

- 选用

1.1.2 warm reset 寄存器

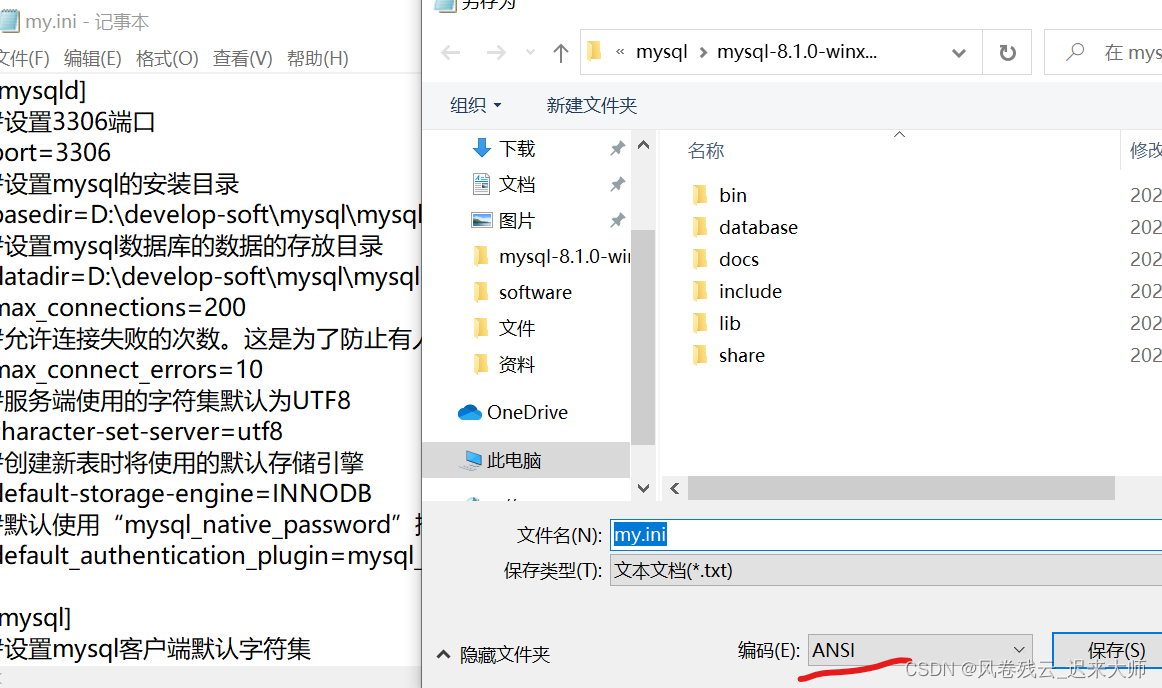

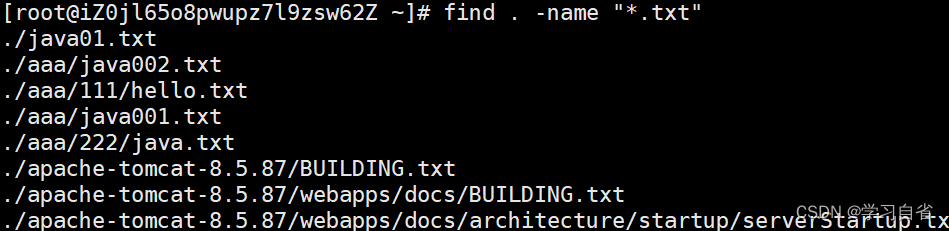

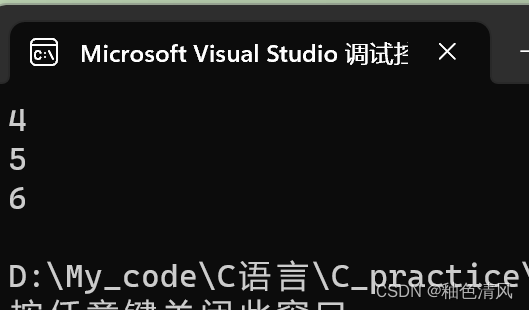

ARMv8 中只要配置 RMR_EL3 寄存器,系统就会进入warm reset,如下参考代码:

...

ldr x1, =vector_table

msr vbar_el3, x1

...

warm_reset:

mov x0, xzr

mov x0, #3

msr rmr_el3, x0

isb

dsb sy

1: wfi

b 1b

.balign 0x800

vector_table:

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

bl warm_reset

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

.balign 0x80

b .

在 AARCH32 状态下 RMR 是 CP15协处理器的寄存器,通过以下指令访问

MRC P15, 0, <Rt>, C12, C0, 2; Read RMR into Rt

MCR P15, 0, <Rt>, C12, C0, 2; Write Rt to RMR

RMR 是 RMR_EL3 在32模式下的映射,写此寄存器将触发热复位。

系统在 cold reset 过程中,可以在 ATF 中配置 RVBAR_EL3 来指定 CPU 的 warm reset vector 的地址,warm reset 的时候 cpu 执行的函数地址就来自于这个寄存器。那么Reset vector base addr不再局限于 00000000 / FFFF0000了。在实现 ARMv8 SoC的时候:通过 RVBARADDR signal 指定任意地址。

1.1.3 PSCI Suspend/Resume

系统进入 suspend 之后,会通过 PSCI 接口进入 ARM lib 库文件,然后进入bl32,系统从 UDR 出来之后,走的应该也是 warm reset,因为系统在 cold reset 的时候已经配置好了 RVBAR 寄存器了。

如果系统走的是cold reset,那么BL1->BL2->bl31_entrypoint

系统从 UDR 模式出来的时候,一般是在 ATF 中跳转到 kernel,不会在走 uboot流程:

- 一方面是因为

uboot的主要功能是启动加载kernel,在cold reset的过程中完成了使命。 - 另外一方面是因为

UDR出来之后系统走的是bl32_warm_entrypoint,在这个函数流程中不会进入uboot。