牛客网Verilog刷题——VL43

- 题目

- 题目解析

- 答案

题目

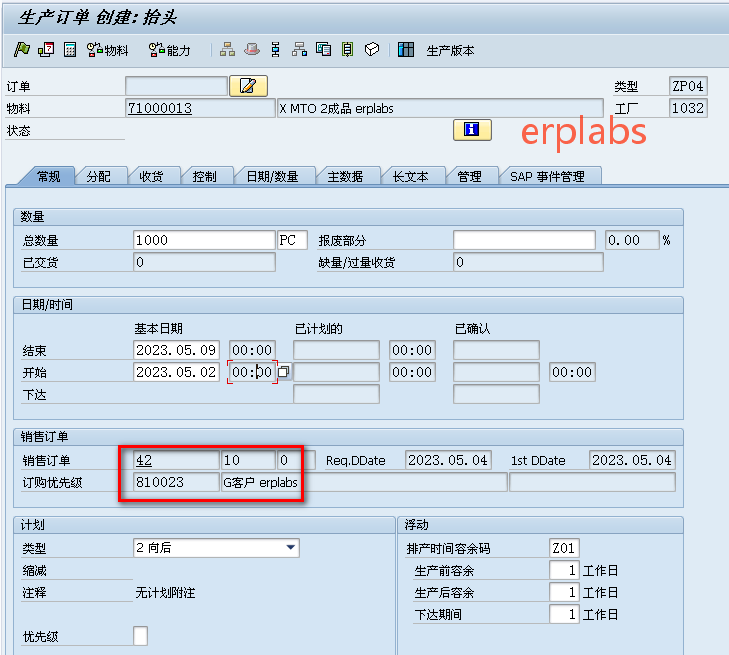

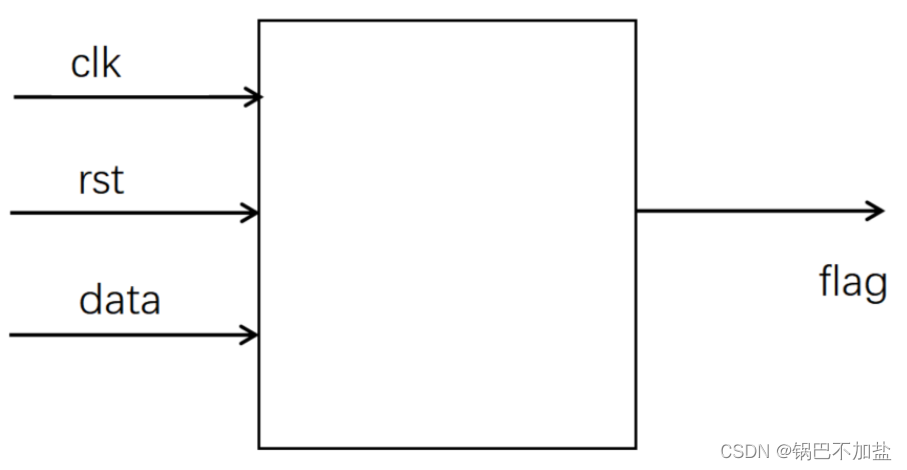

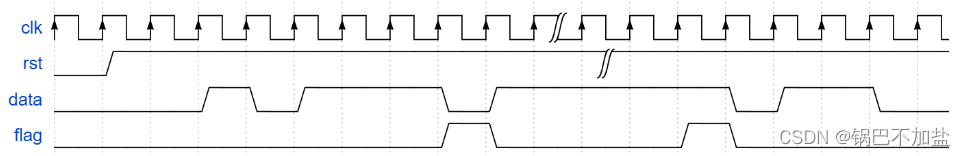

如图所示为两种状态机中的一种,请根据状态转移图写出代码,状态转移线上的0/0等表示的意思是过程中data/flag的值。

要求:

1、 必须使用对应类型的状态机

2、 使用三段式描述方法,输出判断要求要用到对现态的判断

注意rst为低电平复位

输入输出描述:

| 信号 | 类型 | 输入/输出 | 位宽 | 描述 |

|---|---|---|---|---|

| clk | wire | Intput | 1 | 系统时钟信号 |

| rst | wire | Intput | 1 | 异步复位信号,低电平有效 |

| data | wire | Intput | 1 | 输入数据 |

| flag | reg | Output | 1 | 输出标志位 |

题目解析

三段式状态机中,现态curr_state与次态next_state均为寄存器类型变量,现态curr_state(状态机第一段)用时序逻辑,表示当前状态;次态next_state(状态机第二段)用组合逻辑,表示下一个状态;状态机第三段用时序逻辑,输出一些使用状态机控制的数据等。

答案

`timescale 1ns/1ns

module fsm1(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

//*************code***********//

reg [3:0] curr_state;

reg [3:0] next_state;

localparam S0 = 4'b0001;

localparam S1 = 4'b0010;

localparam S2 = 4'b0100;

localparam S3 = 4'b1000;

//第一段

always @(posedge clk or negedge rst)

if(!rst)

curr_state <= 4'b0001;

else

curr_state <= next_state;

//第二段

always @(*)

case(curr_state)

S0:

if(data==1'b0)

next_state = S0;

else

next_state = S1;

S1:

if(data==1'b0)

next_state = S1;

else

next_state = S2;

S2:

if(data==1'b0)

next_state = S2;

else

next_state = S3;

S3:

if(data==1'b0)

next_state = S3;

else

next_state = S0;

endcase

//第三段

always @(posedge clk or negedge rst)

if(!rst)

flag <= 1'b0;

else

case(curr_state)

S0:

if(data==1'b0)

flag <= 1'b0;

else

flag <= 1'b0;

S1:

if(data==1'b0)

flag <= 1'b0;

else

flag <= 1'b0;

S2:

if(data==1'b0)

flag <= 1'b0;

else

flag <= 1'b0;

S3:

if(data==1'b0)

flag <= 1'b0;

else

flag <= 1'b1;

endcase

//*************code***********//

endmodule