前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载

示例:加法器

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ.前置知识

0x00 半加器

0x01 全加器

Ⅱ. Verilog实现

0x00 注意事项

0x01 一位全加器

0x02 串行加法器

Ⅰ.前置知识

0x00 半加器

能对两个1位二进制数进行相加求和及进位的逻辑电路称为半加器。或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

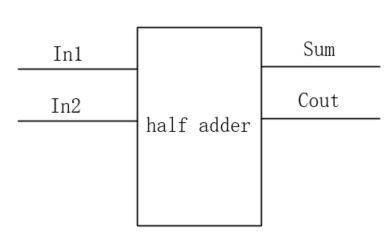

下图为半加器的方框图:

其中:In1、In2分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

根据二进制数相加的原则,得到半加器的真值表如下表:

| 信号输入 | 信号输出 | ||

| In1 | In2 | S | C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

0x01 全加器

全加器其实就是考虑到进位的加法器。

| 全加器输入 | 全加器输出 | |||

| A | B | Cin | BCDout | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

真值表:

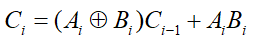

逻辑表达式:

由于两个半加器可以构成一个全加器,所以在这里进位Ci还可以表示为:

Ⅱ. Verilog实现

0x00 注意事项

本次实验中,涉及到了子模块和主模块的编写。

在主模块中(顶层文件),对子模块进行调用,从而满足设计

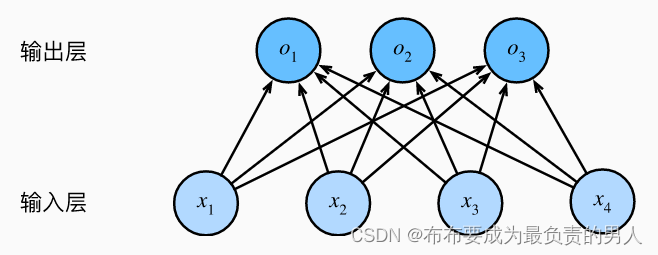

下面以加法器为示例,介绍子模块和主模块的编写和调用:

1、设计子模块

参考程序:

程序文件一:

module FA1(input A,input B,input Cin,output reg Cout,output reg S);

always @(A or B or Cin)begin

{Cout,S}=A+B+Cin;

end

endmodule程序文件二:(选用,自定义)

module UserAND(a,b,z);

input a,b;

output z;

assign z=a&b;

endmodule 以上程序也可自行进行设计修改;

2、设计主模块: (顶层文件)

module EX5_Top(input [1:0] IA,input [1:0] IB,output [1:0] sum,output C );

wire ct;

//子模块的调用,例如其中FA1为子模块名称,FD0和FD1为在顶层文件中引用的名称。

FA1 FD0 (.A(IA[0]),.B(IB[0]),.Cin(0),.Cout(ct),.S(sum[0]));

FA1 FD1 (.A(IA[1]),.B(IB[1]),.Cin(ct),.Cout(C),.S(sum[1]));

Endmodule3、编译文件并查看RTL视图(如图参考)

0x01 一位全加器

设计代码:

module ADD_Top(input [1:0] IA,input [1:0] IB,output [1:0] sum,output C );

wire ct;

ADD FD0 (.A(IA[0]),.B(IB[0]),.Cin(0),.Cout(ct),.S(sum[0]));

ADD FD1 (.A(IA[1]),.B(IB[1]),.Cin(ct),.Cout(C),.S(sum[1]));

endmodule

module ADD(input A,input B,input Cin,output reg Cout,output reg S);

always @(A or B or Cin)begin

{Cout,S}=A+B+Cin;

end

endmodule

仿真设计代码:

module sim_ADD_Top( );

reg [1:0] IA;

reg [1:0] IB;

wire [1:0] sum;

wire ct;

ADD_Top uu1(IA,IB,sum,ct);

initial {IA,IB}=4'b0000;

always

#100{IA,IB}={IA,IB}+1;

endmodule点击Vivado的“Run Simulation”菜单,进入仿真调试模式,可以在仿真输出窗口看到仿真时序波形

波形图:

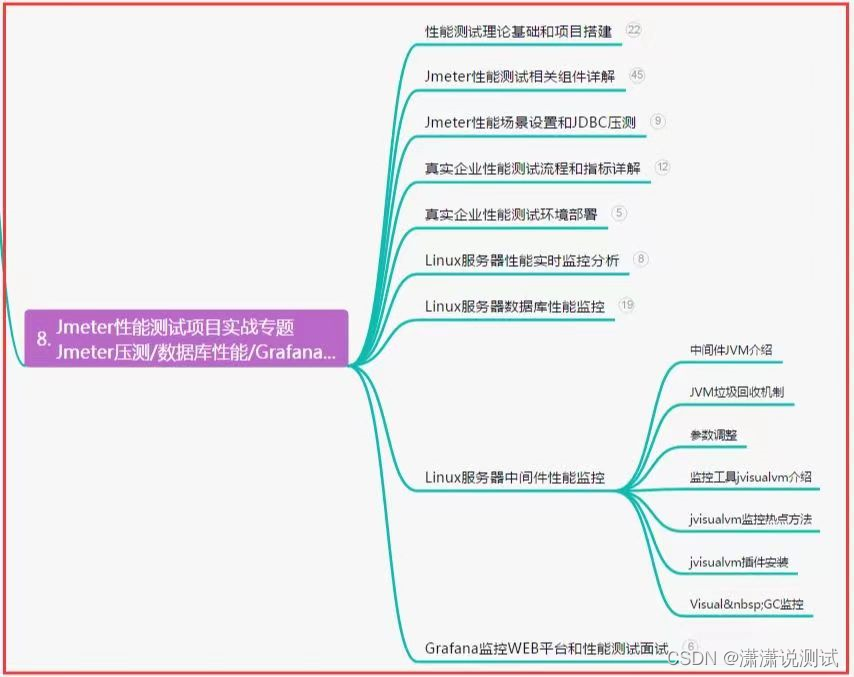

0x02 串行加法器

在理解了半加器与全加器的基础上,采用模块化的设计方法,我们可以通过四个全加器来实现四位串行加法器的设计

设计代码:

`timescale 1ns / 1ps

module M_4bit_adder(S,C3,A,B,C_1);

input [3:0] A,B;

input C_1;

output [3:0] S;

output C3;

wire C0,C1,C2;

fulladder u0(S[0],C0,A[0],B[0],C_1);

fulladder u1(S[1],C1,A[1],B[1],C0);

fulladder u2(S[2],C2,A[2],B[2],C1);

fulladder u3(S[3],C3,A[3],B[3],C2);

endmodule

module halfadder(S,C,A,B);

input A,B;

output S,C;

xor(S,A,B);

and(C,A,B);

endmodule

module fulladder(S,C,A,B,Cin);

input A,B,Cin;

output S,C;

wire S1,D1,D2;

halfadder HA1(.S(S1),.C(D1),.A(A),.B(B));

halfadder HA2(.S(S),.C(D2),.A(S1),.B(Cin));

or g1(C,D2,D1);

endmodule

仿真设计代码:

module sim_ADD();

reg [3:0] A,B;

wire [3:0] S;

wire C3;

M_4bit_adder uu1(S,C3,A,B,0);

initial {A,B}=8'b0000_0000;

always

#100 {A,B}={A,B}+1;

endmodule波形图:

添加硬件约束并连接实验电路板,

参考管脚分配如下:

| 程序中管脚名 | 实际管脚 | 说明 |

| A(0) | N4 | 拨动开关 SW1 |

| A(1) | M4 | 拨动开关 SW2 |

| B(0) | R2 | 拨动开关 SW3 |

| B(1) | P2 | 拨动开关 SW4 |

| SUM(0) | K2 | LED 0 |

| SUM(1) | J2 | LED 1 |

| C | J3 | LED 2 |

实验电路板实现:

![C国演义 [第十一章]](https://img-blog.csdnimg.cn/abf028a942814cc6a9e041e6b8314b86.png)