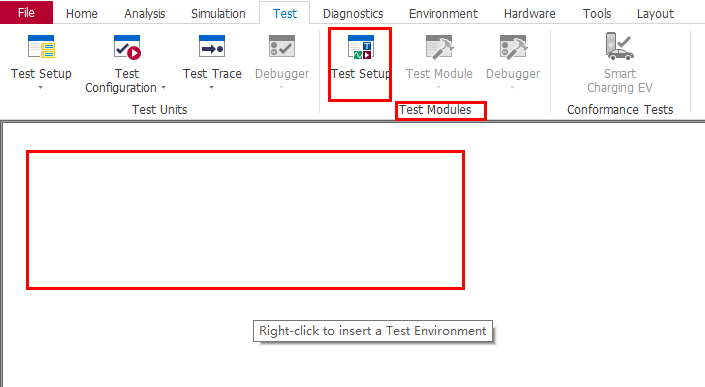

代码1:

`timescale 1ns/10ps

module d_trigger(

d,

clk,

q);

input d;

input clk;

output q;

assign q=~d;

endmodule

//testbench

module d_trigger_tb;

reg clk;

reg d;

wire q;

d_trigger d_trigger(

.d(d),

.clk(clk),

.q(q)

);

initial begin

d<=0;clk<=0;

#1000 $stop;

end

always #10 begin clk<=~clk;d<=~d;end

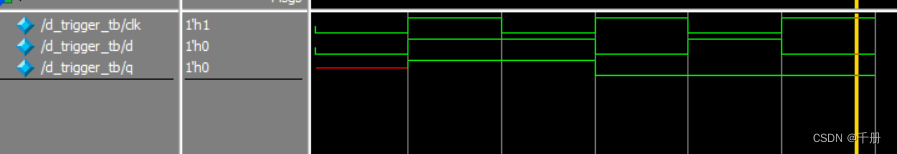

endmodule实验波形

貌似没什么问题

代码二:

`timescale 1ns/10ps

module d_trigger(

d,

clk,

q);

input d;

input clk;

output reg q;

always@(posedge clk)

begin

q<=d;

end

endmodule

module d_trigger_tb;

reg clk;

reg d;

wire q;

d_trigger d_trigger(

.d(d),

.clk(clk),

.q(q)

);

initial begin

d<=0;clk<=0;

#10 clk<=1;d<=1;

#10 clk<=0;d<=1;

#10 clk<=1;d<=0;

#10 clk<=0;d<=1;

#10 clk<=1;d<=0;

#10 $stop;

end

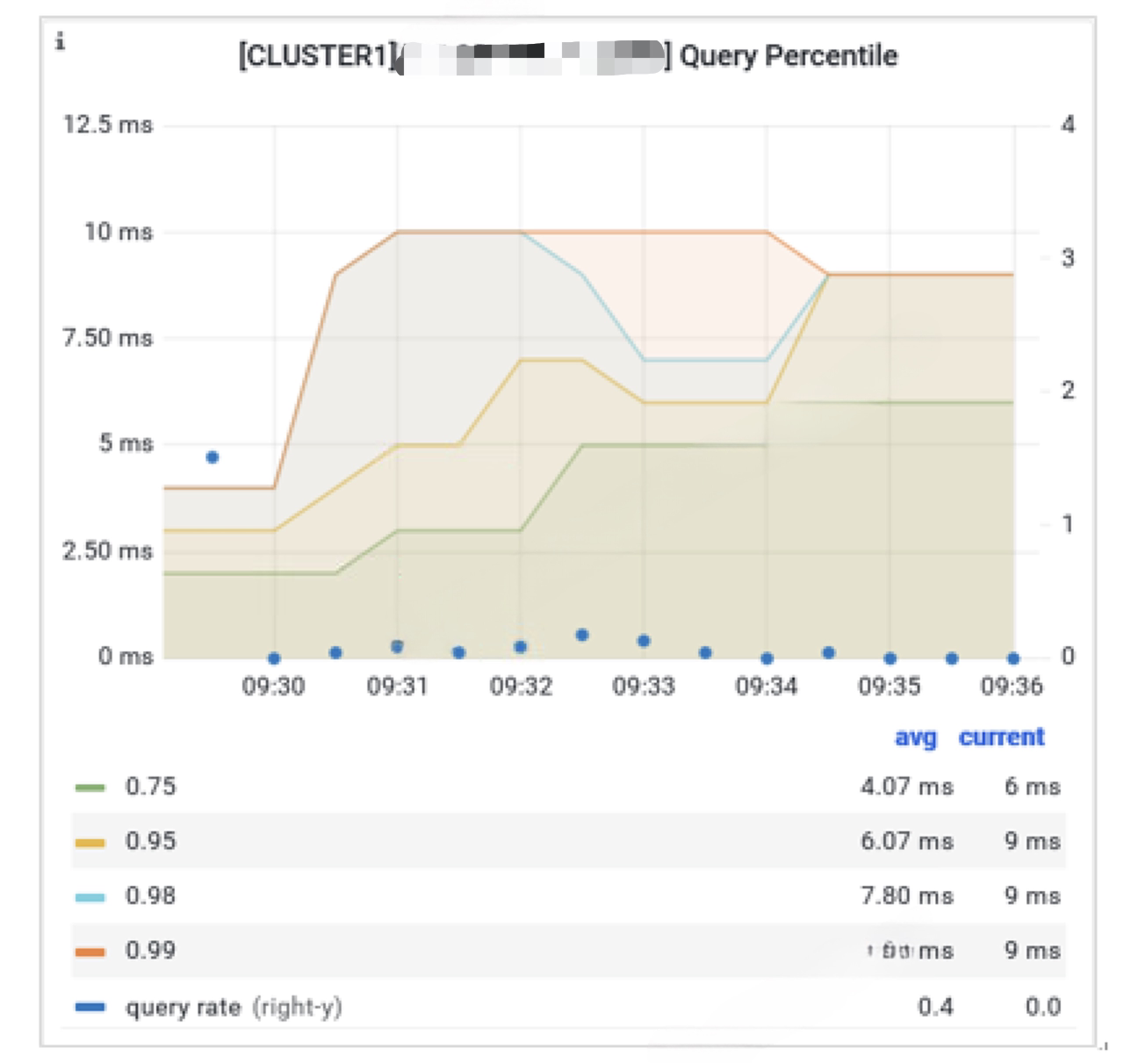

endmodule实验波形: