3.1

系统需求分析

3.1.1

系统功能设计要求

本硬件处理平台的主要任务有三类,一是数据采集,包括采集惯性测量元件

的输出信号,接收外部系统校正信息,如

GPS

信息等;二是数据处理与计算,包

括惯性测量元件的误差补偿、初始对准、导航参数解算和在线校正滤波等;三是

导航数据输出,包括导航参数输出以及与主控设备信息交换等。

本硬件电路系统要实现的具体功能包括

(

1

)对三路加速度计模拟信号进行高精度模数转换;

(2)定时采集三路陀螺仪的数字量信号;

(3)定时采集一路

GPS

信号及其秒脉冲时基信号;

(4)定时采集一路气压计数字信号;

(5)定时采集两路里程脉冲信号;

(6)定时采集

5

路测温传感器数字信号;

(7)将所得到的信号进行导航解算处理以及将各种数据进行打包,分别经过

一路

CAN

接口、一路

RS232

接口和一路

RS422

接口输出。

3.1.2

系统性能设计要求

1

、输入电源为单路直流电压源,电压范围是

18V

~

36V

,最大电流

1A

。

2

、

AD

转换要求

(

1

)输入信号形式为

X

、

Y

、

Z

三路加速度计输出的模拟电流信号;

(2)输入范围

±8

mA

;

(3)线性度

<1.0×10

4

;

(4)对称性

<1.0×10

4

;

(5)数据分辨率不低于

24

位,实际测试精度不低于

18

位;

(6)加速度计模数转换电路带宽不低于

100Hz

。

3

、接收五路测温传感器的数字信号,信号更新率为每秒一次。

4

、输入信号接口形式

(

1

)七路总线输入

a.

三路异步串行总线

RS422

,波特率软件可设置,需光耦隔离,总线接收缓

冲区不小于

256

字节;

b.

两路异步串行总线

RS232

,波特率软件可设置,需光耦隔离,接收缓冲区

不小于

256

字节,分别用于接收

GPS

信号和气压计信号;

c.

一路异步串行总线

RS422

,波特率软件可设置,需光耦隔离,全双工工作

模式,用于接收信号和发送指令信息,总线接收缓冲区不小于

256

字节;

d.

预留一路异步串行总线

RS422

,波特率软件可设置,需光耦隔离,全双工

工作模式,总线接收缓冲区不小于

256

字节。

(2)两路里程计输入信号

里程计为方波信号,低电平最大为

1

V

高电平为

4.5

V

~

12

V

,信号频率不大于

10

KHz

,由板卡处理器对其进行计数。其中一路信号用作行车信号,高电平脉冲

累加,低电平不计数,另一路信号用作倒车信号,高电平脉冲递减,低电平不计

数。

5

、输出信号接口形式

(

1

) 一路

RS422

通用异步串行通讯接口,全双工传送,双端隔离,波特率

允许软件更改;

(2)一路

RS232

通用异步串行通讯接口,双端隔离,通讯波特率允许软件

更改;

(3)一路

CAN

通讯接口,满足标准

CAN

总线协议,允许软件对发送数据

的波特率进行控制,

FIFO

缓冲区大小不小于

64

字节。

3.2

系统总体设计概述

3.2.1

系统各模块概述

本系统要求包括丰富的外设接口和高精度的数据采集,同时还具备强大的数

据处理能力,以满足实际应用对精度和实时性的双重要求。

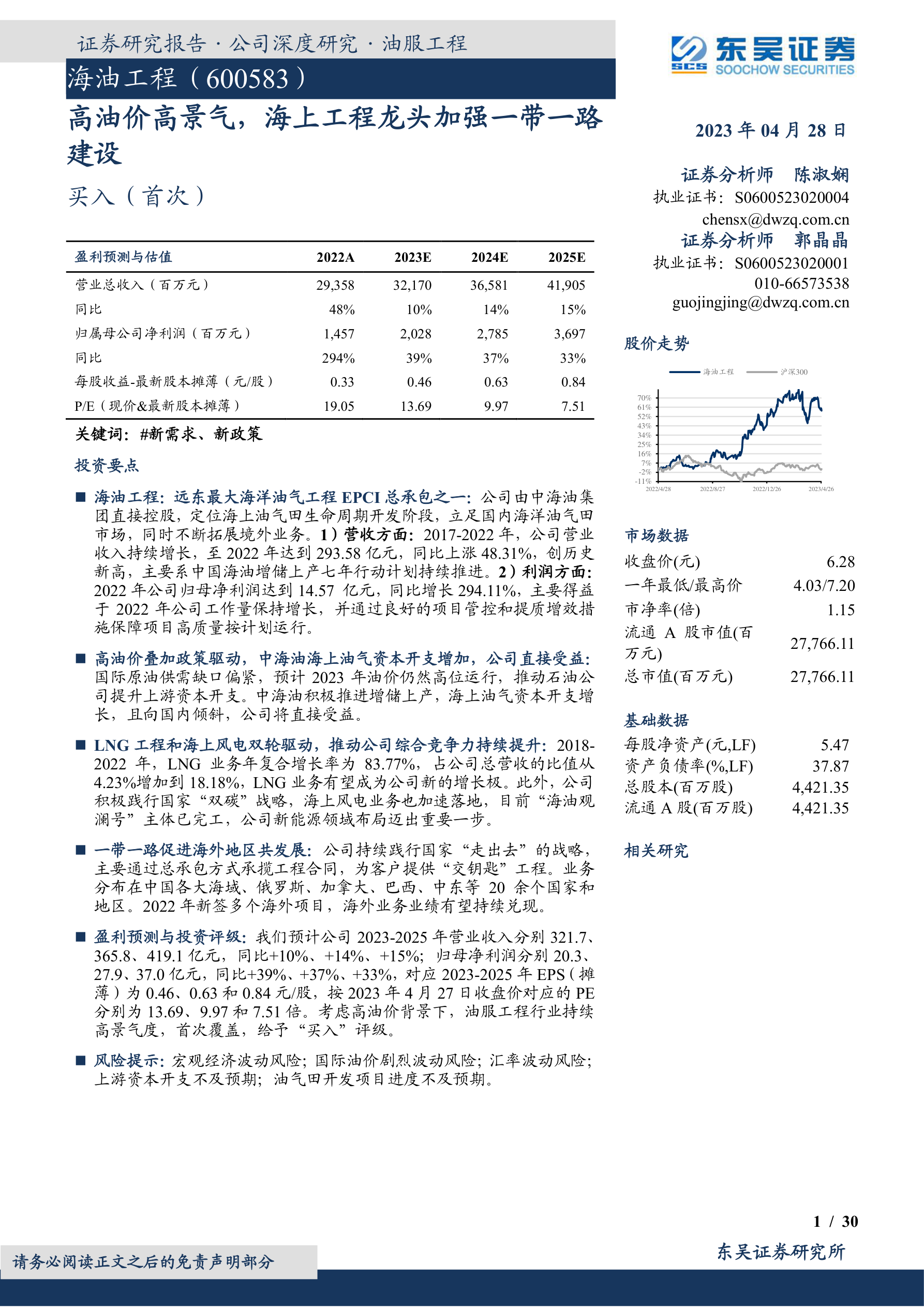

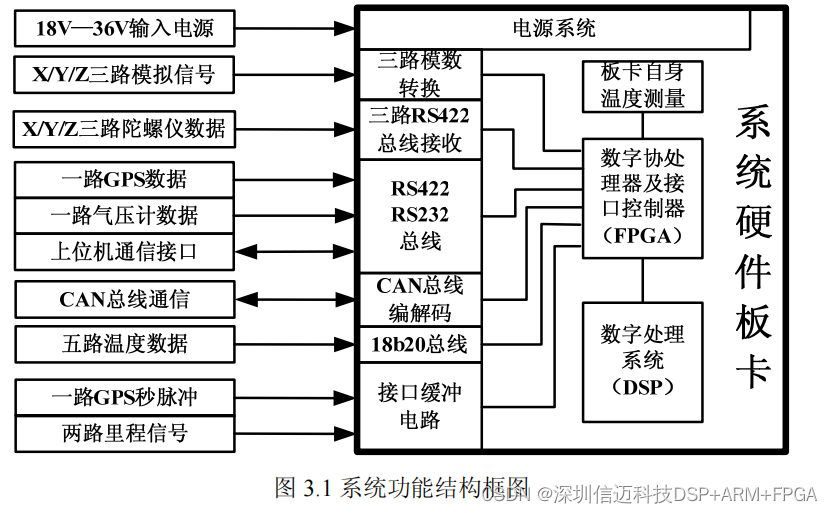

系统功能框图如图

3.1

所示,其主要的模块有

(

1

)电源模块。其主要作用是把外部输入的

18

V

~36

V

的电压源转换成系统

所需的各种电压,并对电源进行监控和管理;

(2)外设通信模块。主要作用是跟外部设备进行通信接口;

(3)模数转换模块。其主要作用是接收外设输入的三路电流信号,并对其进

行高精度的采集与转换,再把转换得到的数据发送给处理器,以便做进

一步的处理;

(4)板卡测温模块。其主要作用是测量板卡自身的温度,用于对板卡进行温

度补偿校正;

(5)数据处理模块。其主要作用是接收外设发送的信息,并对其做相应的处

理,然后把结果通过总线接口发送出去。它主要包含两个子模块即

FPGA

为核心的数字信号协处理器和

DSP

核心运算处理器。

3.2.2

处理器架构

实时信号处理系统中,低层的信号预处理算法处理的数据量大,对处理速度

要求高,但运算结构相对比较简单,适于用

FPGA

进行硬件实现。高层处理算法

所处理的数据量较低层算法少,但算法的控制结构复杂,适于用运算速度高、寻

址方式灵活、通信机制强大的

DSP

芯片来实现。采用

DSP+FPGA

的数字硬件系

统就可以把二者优点结合一起,兼顾速度和灵活性,既满足底层信号处理要求,

又满足高层信号处理要求

[21]

。

DSP+FPGA

系统最大的优点是结构灵活,具有较强

的通用性,适合于模块化设计,从而能够提高算法效率;同时其开发周期较短,

系统容易维护和扩展,适合实时信号处理。

DSP+ FPGA

系统的核心由

DSP

芯片和

FPGA

芯片组成。另外还包括一些外

围的辅助电路,如存储器、先进先出(

FIFO

)器件及

FLASH

存储器等。

FPGA

电路与

DSP

相连,利用

DSP

处理器强大的

I/O

功能实现系统内部的通信。从

DSP

角度看,

FPGA

相当于它的协处理器,外部电路辅助核心电路进行工作。

DSP

和

FPGA

各自带有

RAM

,用于存放处理过程所需要的数据及中间结果。

FLASH

存

储器中存储了

DSP

执行程序和

FPGA

的配置数据。

FIFO

器件则用于实现信号处

理中常用到的一些操作,如延迟线、顺序存储等。

DSP

的外围电路主要是

FLASH

、存储器和

SRAM

,需要完成相应的电路设

计。它需要连接的连线主要包括

DSP

模式选择、时钟模式选择、

JTAG 接口和电

源等。

FPGA

外围电路主要包括用于配置的

PROM

、

FLASH

、模数转换和

FIFO

器件等。除了这些电路需要设计外还需设计的电路包括

FPGA

模式选择、全局时

钟、

JTAG

接口、输出

/

输入接口、测试口和电源等。

3.3

主要器件选型

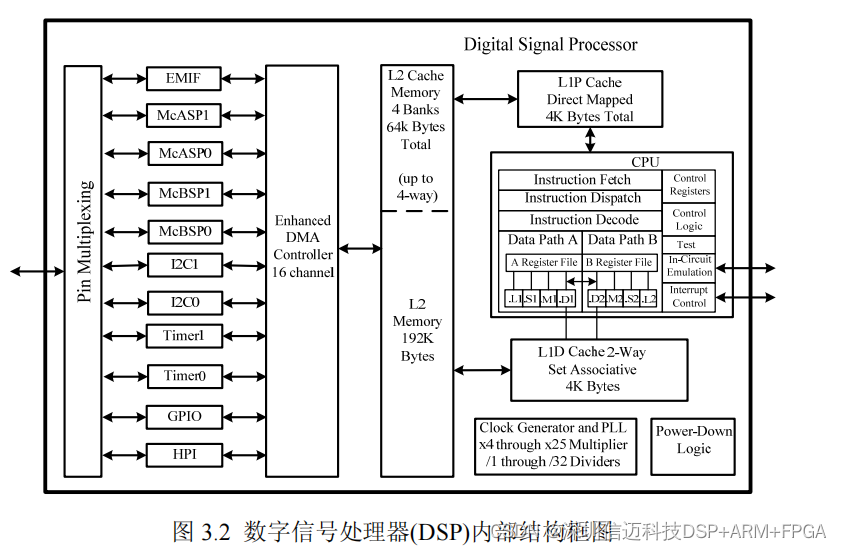

3.3.1 DSP

选型

由于本系统需要进行大量的实时信号处理,所以

DSP

芯片必需具有强大的数

据运算能力,同时为了保证导航定位的精度,需要进行大量的浮点运算。

针对以上要求,本设计中的

DSP

选取美国德州仪器公司(

TI

)生产的

TMS320C6713GDPA

。

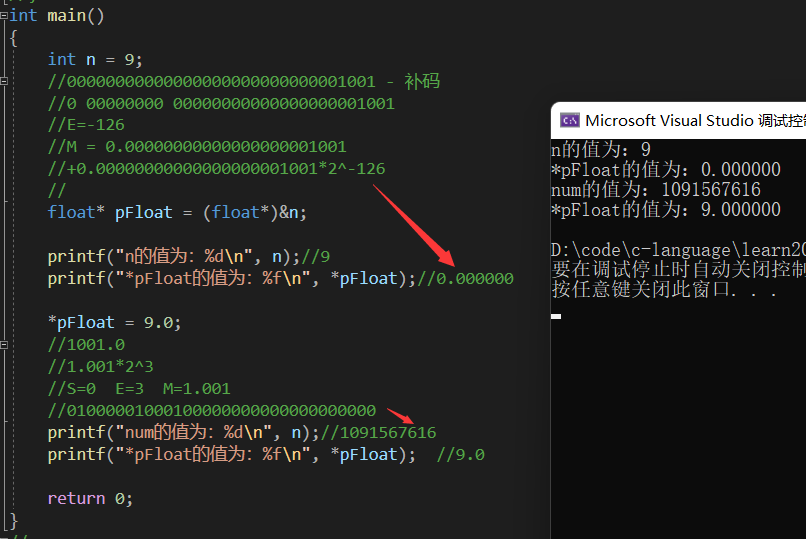

TMS320C6713

是

32

位浮点

DSP

,最高工作主频可达

300

MHz

,处理速度高达

2400MIPS

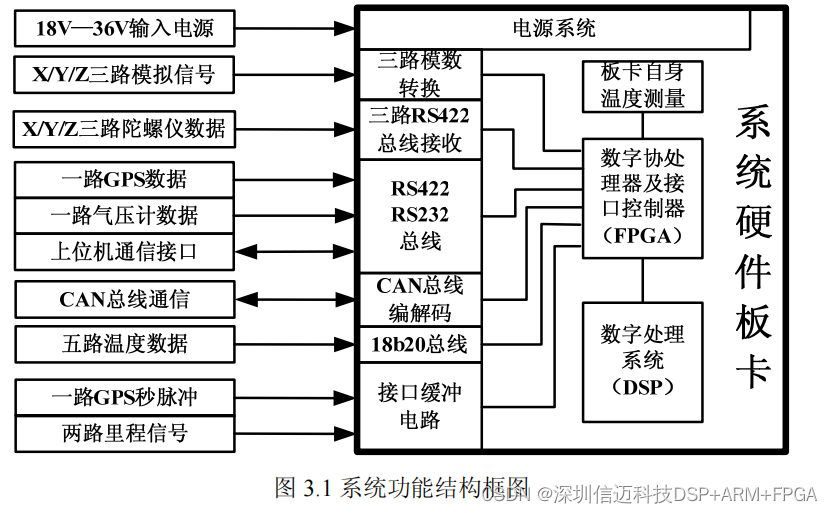

。如图

3.2

所示,该

DSP

使用

2

级缓存架构,第

一级是一个程序缓存(

L1P

)和一个高速数据缓存(

L1D

),容量都是

4KB

。第二

级是一个程序和数据共享的存储器,容量为

256KB

,其中的

64KB

可以配置成高

速缓存和寄存器,剩下的

192KB

可以配置成内部的静态存储器(

SRAM

)。片内

有丰富的外设资源,其中含有两个多声道音频串行接口(

McASP

)、两个多通道

缓冲串行接口(

McBSP

)、两组

I2C

总线、一组通用的输入

/

输出接口(

GPIO

)、

两个

32

位通用定时器和一个

16

位主机接口(

HPI

)。此外,

TMS320C6713

还有

32

位的外部并行总线接口(

EMIF

),分为

4

个存储空间(

CE0

~

CE3

),每个存储

空间的寻址范围为

256M

字节,可以访问

8

位、

16

位或

32

位数据宽度,每个空

间均可与

SDRAM

、

SBSRAM

及其它的异步外设实现无缝接口

[22]

。

TMS320C6713

主要特点是

[23]

:

(

1

)采用超长指令字(

VLIW

)结构,单指令字长为

32

位,指令包里有

8

个

指令,总字长达到

256

位。程序运行时通过专门的指令分配模块,可以将每个

256

位的指令包同时分配到

8

个处理单元,并由

8

个单元同时运行。

(2)采用二级缓冲处理,

4KByte

直接匹配的程序缓冲

L1P

,

4KByte

可匹配

的数据缓冲

L1D

,

256Kbyte L2

额外匹配内存。

32

位外部存储器接口,可无缝连

接

SRAM

、

EPROM

、

Flash

、

SBSRAM

和

SDRAM

。

(3)丰富的外设,包括

DMA

,

EDMA

,扩展总线,具有主机口和

I/O

端口

操作等功能,多通道缓冲串口,其通过配置能和多种串行通信接口通信,两个

32

位通用定时器等。

(4)内核有两套相同的运算核心,可以并行运行。

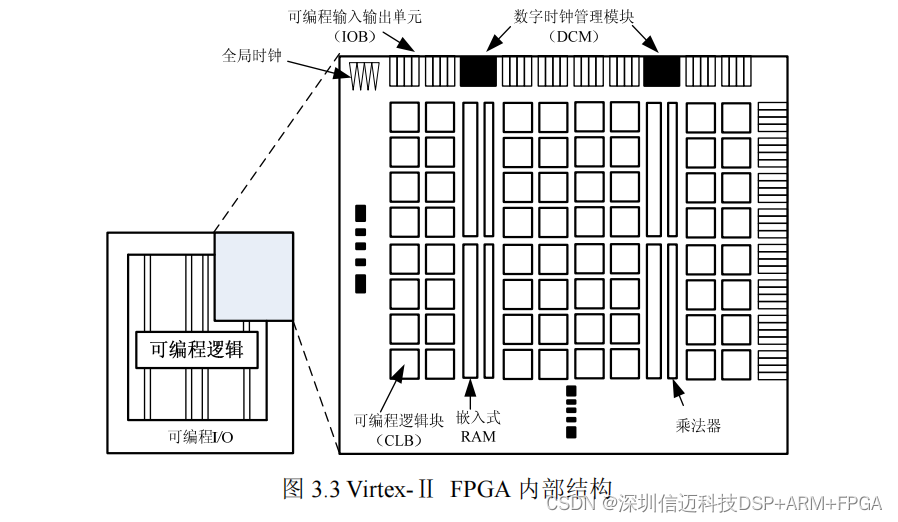

3.3.2 FPGA

选型

FPGA

是一种可由用户根据所设计的要求,在现场由自己配置和定义的高密

度专用数字集成电路,属于一种特殊的

ASIC

(专用集成电路)芯片。

FPGA

具有

寄存器资源丰富和容量大的优点,适合于实现数据密集型的系统,并且可以进行

SOPC

(可编程偏上系统)设计。

FPGA

主要优点包括

(

1

)

FPGA

的用户现场可编程的特性大大缩短了设计周期,使产品的上市时

间大大缩短,适合现代的市场竞争需求。

(2)芯片的规模越来越大,其单片逻辑门数量已达上千万门,能实现的功能

也越来越强。可以大大减少印刷电路板的空间和降低系统功耗。从而实现高可靠

性和高密度的系统集成。

(3)

FPGA

可以反复编程,重复使用,没有前期投资风险,且可以在开发系

统中直接进行系统仿真,所以可以极大地减少工艺实现的损耗。

Xilinx

公司是世界上最大的

FPGA

供应商之一。

Xilinx

的主流

FPGA

分为两

大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如

Spartan

系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,

如

Virtex

系列。

Virtex-

Ⅱ

系列是

Xilinx

公司近几年研发的具有高性能、高速度和

低功耗特点的新一代

FPGA

。该系列

FPGA

基于

IP

核和专用模块设计,能够为电

信、无线电、网络、视频和数字信号处理领域的应用提供完整的解决方案。

本系统中

FPGA

主要用于逻辑控制和协处理,为了便于系统功能升级,经过

比较和筛选,本设计选取了

Xilinx

公 司

Virtex

系列的

FPGA

芯 片

XC2V1000-5FG256I

。该

FPGA

是

256

管脚

BGA

封装,可用的输入输出接口(

I/O

)

有

172

个,内核电压为

1.5

V

,

I/O

电压为

3.3

V

,工作温度范围是

-40°C

~

+100°C

,

系统门密度为

1M

,内嵌专用硬件乘法器,内嵌的

720Kbit

的块存储器(

BlockRAM

)

可以配置成

RAM

、

FIFO

和双口

RAM

,以及包含

8

个数字时钟管理模块(

Digital

Clock Manager DCM

)频率可高达

420MHz

[24]

。足够满足本采集系统的各项功能

设计要求和系统功能的扩展升级。

如图

3.3

所示,该

FPGA

芯片主要由六部分组成,包括:可编程输入输出单

元、基本可编程逻辑单元、完整的时钟管理、嵌入式块

RAM

、丰富的布线资源、

内嵌的底层功能单元和内嵌的专用硬件模块

[25]

。

3.3.3 ADC

选型

ADC

芯片的选择是关系到整个数据采集系统性能指标的关键。基于大动态范

围,高精度和低噪声的考虑,经过比较分析,本系统选用

TI

公司的

ADS1282

作

为本系统的

ADC

器件。

ADS1282

是一款针对工业应用、具极高性能的

31

位

∑-

△

型模数转换器。该

转换器具有稳定四阶

∑-

△

调制器,因而具有非常良好的噪声和线性特性。该调制

器的输出既可以和片上的数字滤波器联合使用,也可旁路输出。数字滤波器可通

过编程来选择不同的滤波器组合方式。片上多路选择器(

MUX

)既可提供用于测

量的附加外部输入,也可用于内部自检电路。片上可编程放大器(

PGA

)具有极

低的噪声和高输入阻抗。同时,片上的增益及失调检测寄存器可支持系统校准功

能

[26]

。

ADS1282

的额定工作温度范围为

-40

℃

~

+85

℃

,适用于能源探测、地震检

测和高精度仪器仪表等要求苛刻的工业应用领域。

ADS1282

的主要特点有

(

1

)高分辨率:在高精度模式,数据输出率为

250 SPS

时信噪比(

SNR

)达

130

dB

,而在低功耗模式,数据输出率为

250 SPS

时信噪比(

SNR

)也可达

127

dB

;

(2)高精度:总谐波失真(

THD

)为

-122

dB

,积分非线性(

INL

)为

0.5

ppm

;

(3)具有低噪声可编程放大器(

PGA

):

5

/

nV H

z

,放大倍数为

1~64

;

(4)具有双通道多路选择输入(

MUX

)功能;

(5)具有超量程快速检测功能的固有稳定

4

阶

△

-∑

调制器;

(6)灵活的片内数字滤波器:可选择 Sinc+FIR+IIR 滤波的不同组合方式, 其中 FIR 滤波方式可编程设置为线性或最小相位响应,数据输出率可在 250 SPS 至 4 KSPS 之间选择;

(7)低功耗:在高精度模式下其功耗为

25

mW

,在低功耗模式下的功耗为

17

mW

,待机模式下为

90

μ

W

,而掉电模式下仅为

10

μ

W

;

(8)具有片上失调及增益校准引擎。

![[JAVA]前后端分离智慧校园电子班牌系统源码微信带小程序](https://img-blog.csdnimg.cn/f97c98f2384c442b84b65ef406454797.png)