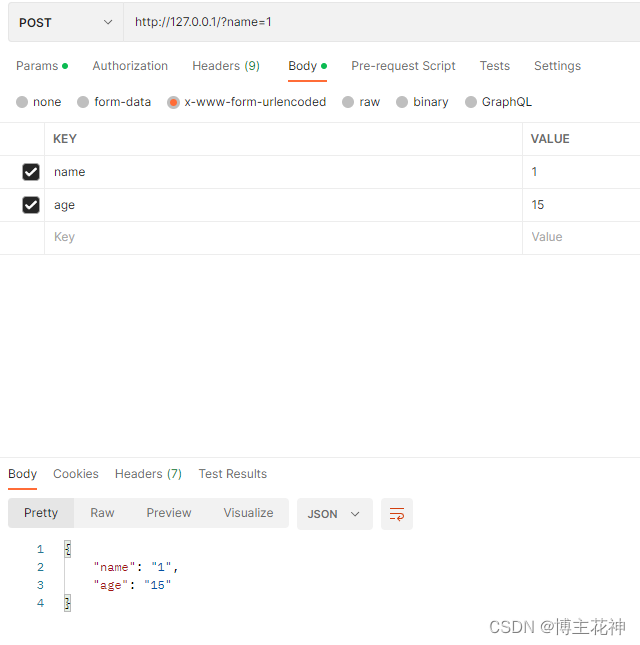

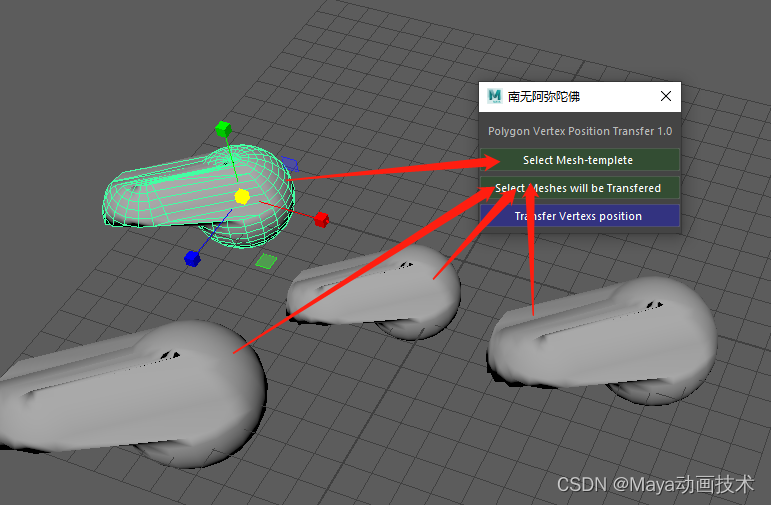

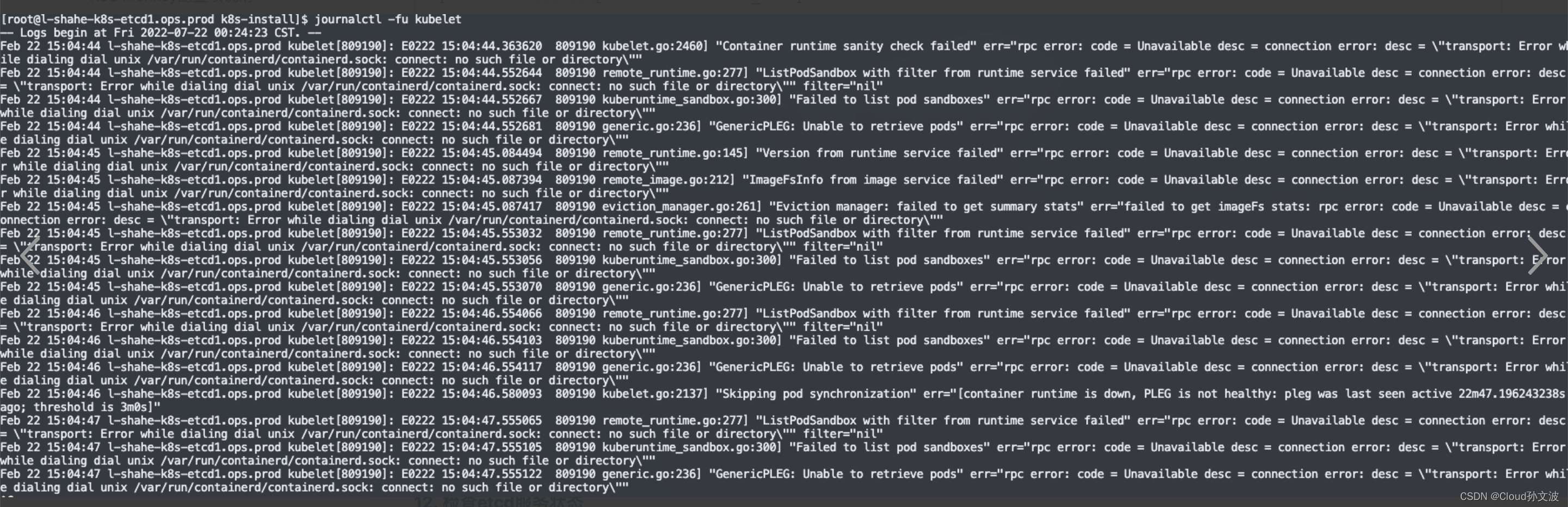

由于QPSK系统下变频之后的信号中频为720MHz,信息符号速率为500Mbps,因此,采用传统的串行解调方案已无法在FPGA中实现解调。因此,本方案采用基于APRX并行架构实现对高速率的QPSK解调。如图1所示,为并行全数字QPSK接收机实现架构。

图1 并行全数字QPSK接收机实现架构

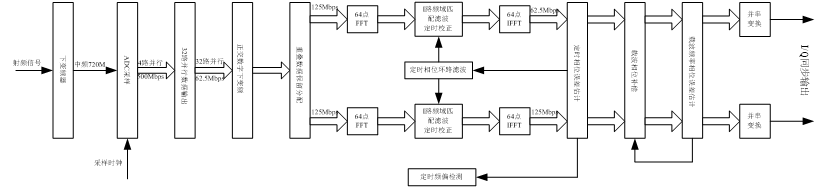

1 高速频域匹配滤波器算法及实现

1.1高速频域匹配滤波器的设计

由数字信号处理相关知识可知,时域作卷积运算等效于频域作乘积运算,由交迭/存储技术可知,实际中数字信号处理只能作循环卷积。而匹配滤波器实际是一个线性卷积过程,而线性卷积可以通过基于DFT的频域滤波器实现。但

![[SCOI2005]骑士精神(C++,启发式搜索)](https://img-blog.csdnimg.cn/img_convert/bb9e313d87be36e97239d793a1e19951.png)