作为光刻机核心单元之一,超精密工件台主要负责实现快速扫描、上下片、精密定位、调平调焦等功能。目前,较为成熟的方案大多采用 VME

并行总线架构来建立超精密工件台控制系统,由于随着系统性能要求的提升,VME

总线以及相应的处理器已无法满足需求,所以必须设计一种新型工件台控制系统。

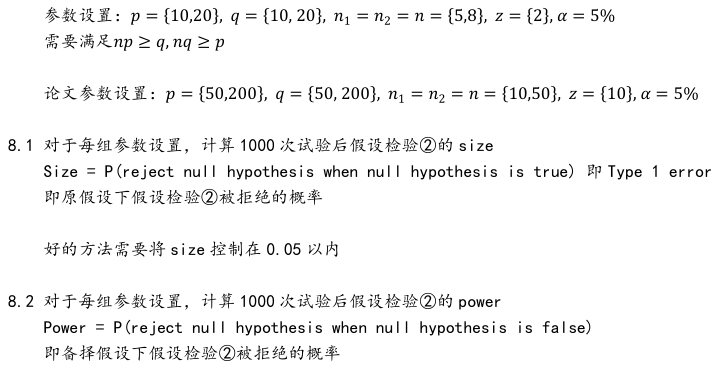

2.1

系统设计需求分析

2.1.1

工件台系统总体介绍

如图

2-1

所示,步进扫描投影型光刻机的工件台主要由测量硅片台、曝光硅片台和掩模台三大部分构成,硅片台和掩模台之间为透视系统。在曝光过程中,控制系统需要对硅片台、掩模台通过激光干涉仪进行高精密位置测量,并对多个自由度进行控制与调节,实现工件台精确定位运动。

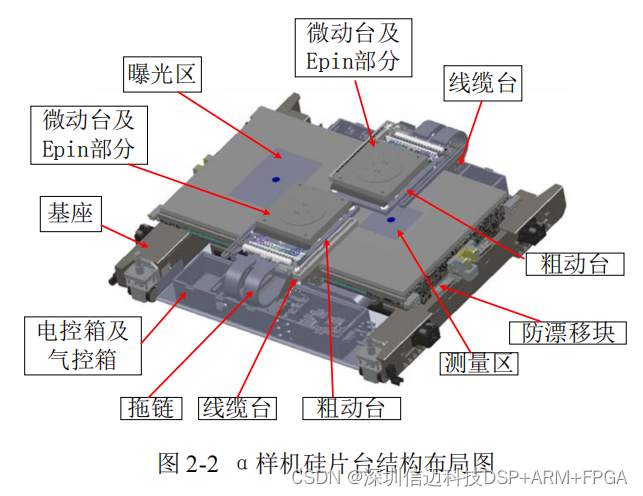

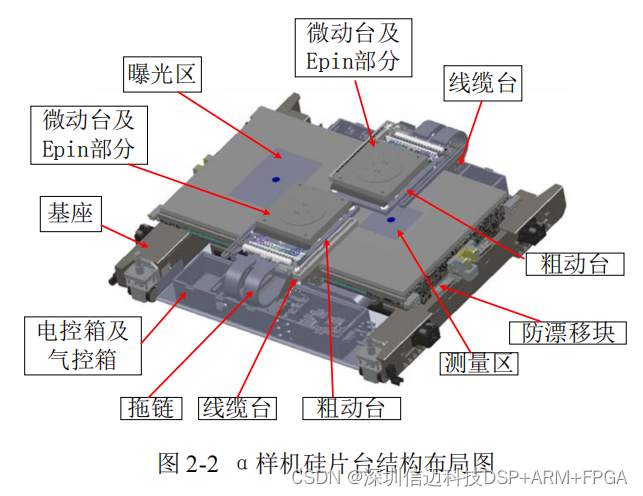

图 2-2

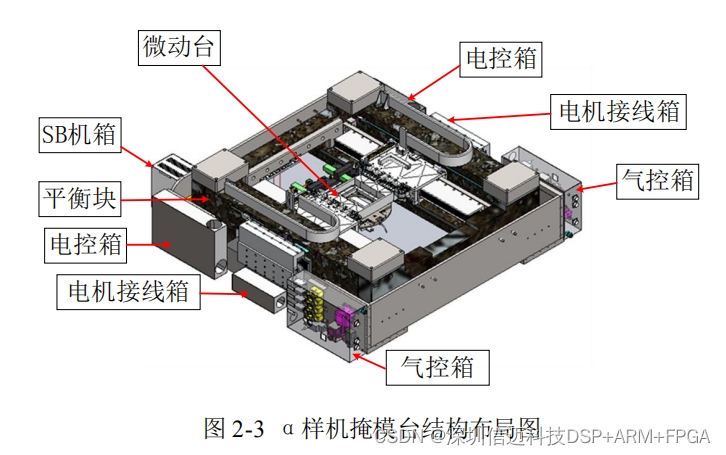

、图

2-3

分别为实验室α样机硅片台、掩模台的总体结构,均采用粗精叠层结构,由粗动台、微动台、线缆台以及平衡块组成。硅片台粗动台沿 X

、

Y 方向以及绕 Z 方向运动的驱动力由 4 个相同线圈阵列供给,每个线圈阵列均由三个线圈单元组成;微动台驱动系统包括 2 个 X 向的动铁式音圈电机、2 个 Y 向的动铁式音圈电机以及 4 个 Z 向的动铁式音圈电机;平衡块四角上均安装了防漂移电机,据统计,测量硅片台和曝光硅片台系统所需驱动轴数共达 32 个。

同样,掩模台系统中微动台也由

2

个

X

向音圈电机、

2

个

Y

向音圈电机和

4 个 Z

向音圈电机驱动;粗动台驱动系统包含

2

个

Y

向的直线电机;掩模台平衡块 有 2

个防漂移电机。因此,掩模台系统共需驱动的轴数为

12

个。经过最终统计, 工件台系统需驱动的轴数总共为 44

个,具体统计如表

2-1

、表

2-2

所示。

硅片台、掩模台的测量系统包括微动台绝对位置反馈测量、微动台与粗动台相对位置局部闭环测量、粗动台与线缆台相对位置测量、线缆台与平衡块相对位置测量、平衡块位置测量和相关的电气限位信号测量。在硅片台的测量系统中,微动台绝对位置反馈测量由 18 轴激光干涉仪实现;微动台与粗动台相对位置局部闭环测

量采用 3

个

PSD

传感器;粗动台与线缆台相对位置测量采用

2

个

PSD

传感器;线 缆台与平衡块相对位置测量由 2

个光栅编码器采集完成;平衡块相对地面位置信 息则由 4

个绝对光栅编码器采集;平衡块电气限位信号

8

个。

在掩模台的测量系统中,微动台绝对位置反馈测量由 9 轴激光干涉仪实现; 微动台与粗动台相对位置局部闭环测量由 8

个电涡流传感器完成;粗动台与平衡 块相对位置采用 2

个绝对编码器采集;平衡块相对地面位置通过

2

个绝对光栅编 码器采集;粗动台电气限位信号和平衡块电气限位信号共 8

个。系统所需采集的 信号数统计如表 2-3

、表

2-4

所示。

2.1.2

系统设计问题分析及需求提出

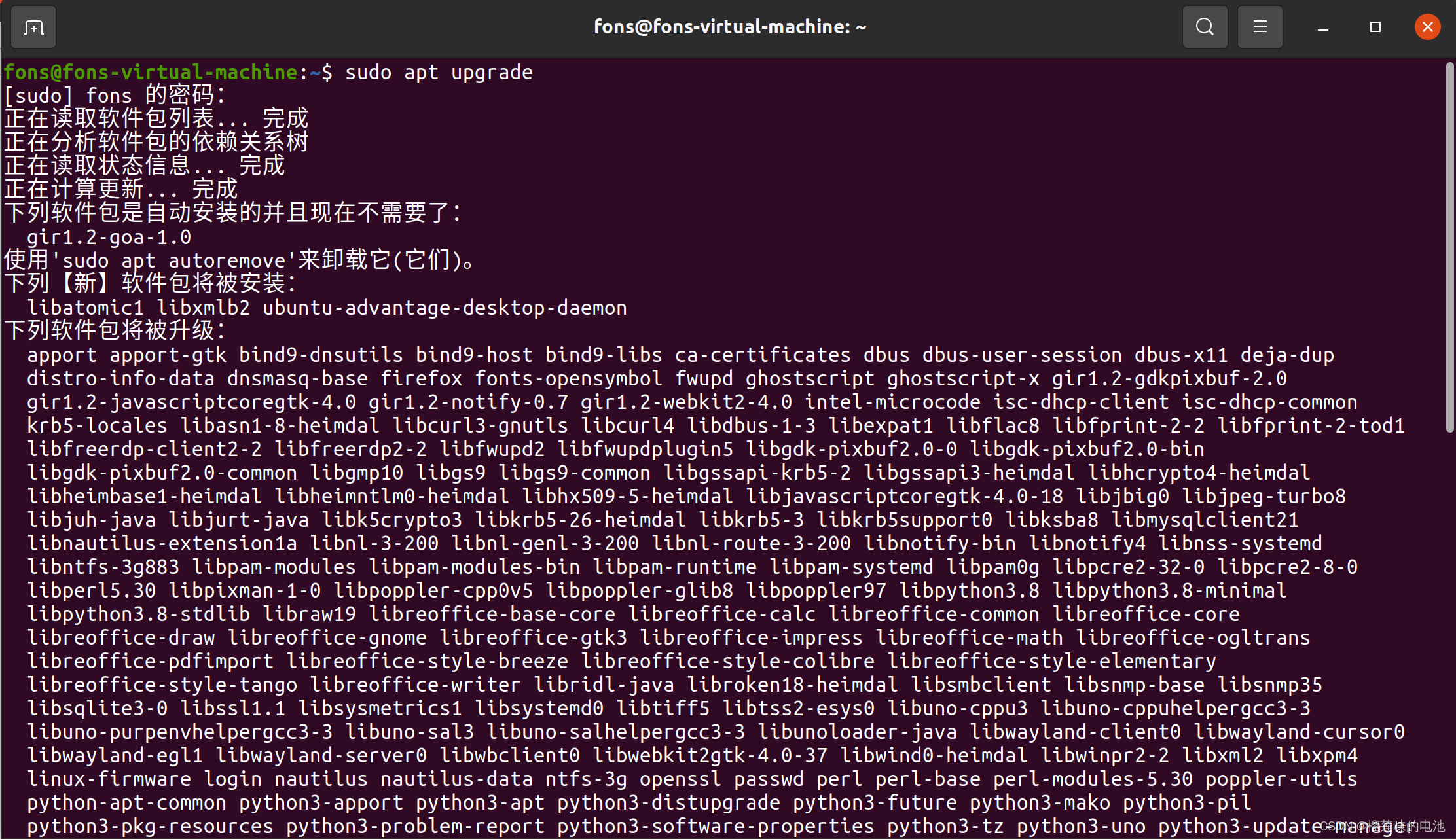

为保证工件台控制系统的实时性,系统中数百个传感器反馈数据须实时传输到运动控制器,而运动控制器必须要在规定的伺服周期内完成 44

轴的位置解算、 精密轨迹插补、位置-

加速度误差补偿、电机解耦等控制算法以及误差处理、控制 过程数据保存等任务,最后将伺服运算结果输送到各个电机的驱动器。 目前步进扫描光刻机工件台控制系统广泛采用 VME 总线构架,由于工件台控 制系统所需控制的电机数量大量增加,而且反馈信号也大量增加,如果只采用一台工控机来处理所有的信号,导致系统数据负载量大、结构复杂,一台机箱无法容纳众多的控制卡和信号处理卡。针对这种情况,控制系统被分为运动控制子系统和激光数据采集子系统,分别嵌入于运动控制侧与测量侧两个 VME 机箱中。运动控制子系统的 VME 机箱中插有多块运动控制卡(MC)、单板计算机卡和一块带有光纤 接口的主同步总线控制板(MBC)。MC 卡之间通过 VME 机箱的 P2 口自定义的非 复用同步位置数据总线(PDB)进行数据传输;MBC 接收来自激光数据采集子系 统发过来的硅片台微动台、掩模台微动台的位置数据;VME 总线作为单板计算机 与运动控制卡和 MBC 之间数据传输的通道,用MBC、MC 初始化,MC 固件下 载和命令传输等。针对以上 VME 控制系统,归纳以下几点在进行系统设计中存在 的问题及需求:

1

)多处理器之间数据传输实时性

VME

系统利用机箱背板的

P2

口自定义的非复用同步位置数据总线(

PDB

)作 为多块 MC

运动控制卡之间高速数据传输的通道,用以在每个中断伺服周期(

200us

) 内传输实时的伺服数据和状态信息。由于 PDB

总线的数据传输带宽理论带宽为 320Mbps,据统计,系统数据传输量在

800B-4KB

范围内,为了提高伺服系统采样 频率,增强系统实时性,总线带宽必须有所提高。

2

)处理器运算性能

VME

系统中

MC

卡集成单核

TMS320C6713b

处理器,其主频性能只有

300MHz

, 现在 DSP

处理性能已超过

1GHz

,因此提高处理器主频可使得控制算法计算时间 缩短,进而提升系统的实时性。

3

)光纤接口数量

在

VME

系统中,每个

MC

卡集成了相应的光纤接口,都能进行独立的数据采 集,由于一块 MC

卡上光纤口资源有限,导致出现以下复杂情况:

情况 i

:例如,微动台的伺服计算由一块

MC

完成,由于单块

MC

卡光纤口有 限,无法采集该微动台的所有传感器反馈信号,那么微动台某一个反馈信号则必须 由另一块 MC

卡采集完成后经

PDB

总线传输过来,增加了不必要的总线数据传 输环节;

情况

ii

:除了采集问题,一块

MC

卡在每个伺服周期内控制微动台的

8

个电 机,光纤口的不足致使此块 MC

卡须将相应的电机控制量通过

PDB

总线传输至另 一块 MC

卡,由另一块

MC

卡的光纤口将最终的电机控制量发送至驱动器。 虽然单 DSP

单光纤口具有模块化的功能,但所面临的系统环境复杂,无法更 优的应用于当前系统中,使得系统数据流不合理、凌乱。

4

)系统计算架构

VME

运动控制系统在数据计算方面采用多个单核

DSP 并行处理模式,面对众多控制对象和传感器信号,一台 VME 机箱无法容纳更的控制卡和信号处理卡。随着多核 DSP 技术的快速发展,多个多核 DSP 并行计算模式有待应用,不仅可以精简整个控制系统,而且提高编程效率。

因此,为了提高光刻机工件台的定位、跟踪精度以及生产效率,控制系统必须在更短的伺服周期内完成大量的位置数据采集、数据传输、控制计算和控制量输出 等任务。然而,基于 VME

总线的工件台运动控制系统瓶颈主要在于总线数据吞吐 速率、网络拓扑、数据处理能力以及接口局限等多方面原因。因此亟待构建一种基于 VPX

总线的多核处理器并行处理架构,并以此为基础开发工件台控制系统的硬件和软件,试图将伺服周期缩短至 100us

。

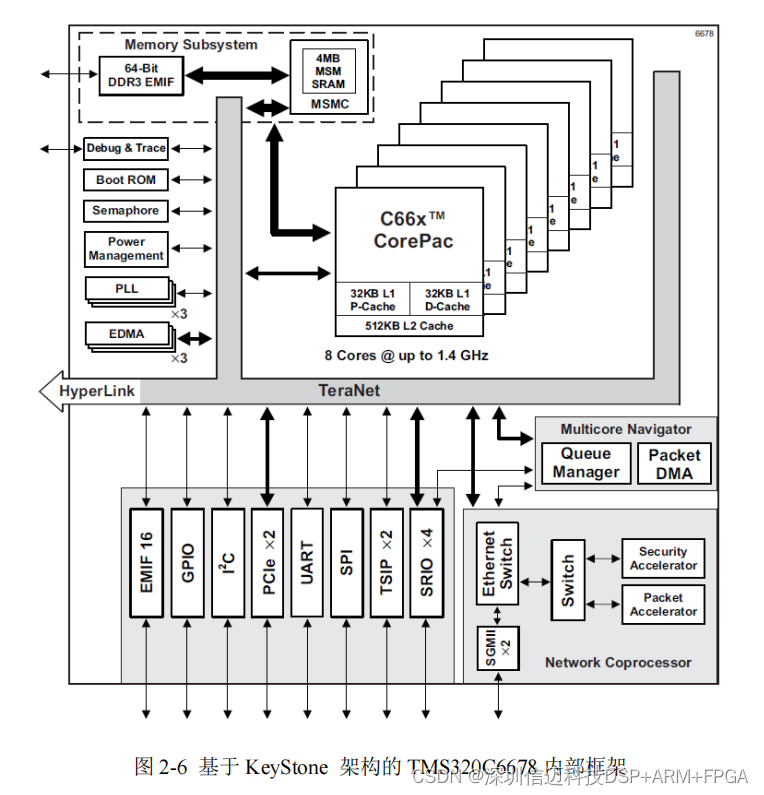

2.2.2

运动控制卡(

MC_4DSP_VPX

)

除了总线带宽之外,运动控制卡核心处理器的性能也对工件台控制系统伺服周期影响较大,目前在工业控制领域中,单片机、ARM

、

DSP

、

FPGA

和

PowerPC 等一些微处理器比较常用。相比较而言,单片机主要面向于低端市场;ARM

在任 务管理、软件系统支持等方面具有优势;FPGA

虽然在理论上可以达到更高频率和 信号处理速度,可是编译复杂,开发周期长,由于 FPGA

具有超强的逻辑编程柔性和并行处理资源,故只作为协处理器用在接收发送信号端;ASML

公司采用的单核

PowerPC

成本高且存在技术封锁问题,而且经过前期在

PowerPC

上的

RapidIO

带 宽测试,通信延迟较大,不符合系统设计要求;DSP

具有杰出的大数据处理能力, 而且随着处理数据量的增加,单核 DSP

芯片发展越来越不满足系统要求,传统嵌 入式系统是增加并行处理板上单核 DSP

芯片数量

[34]

或者增加单板数量,这样会导 致单板面积增大、I/O

不足或机箱内板卡数过多等问题,因此多核

DSP

在运算速 度、系统精简度和开发难度上有较好优势,并且依靠上一代单核 DSP

系统,具有 一定的可移植性。通过对系统需求以及处理芯片的性能和价格等方面的比较和分

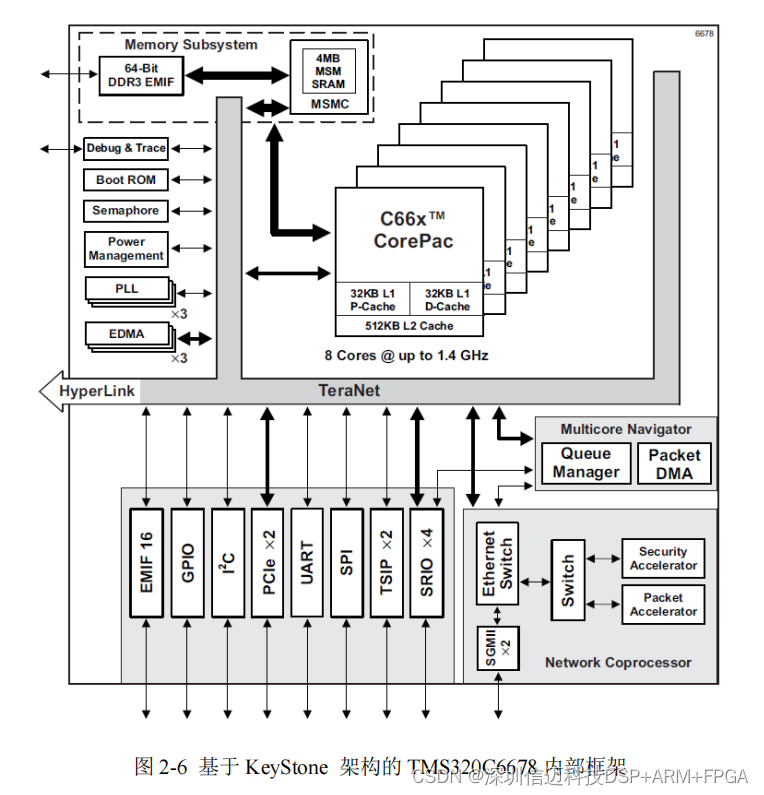

析,本文选取

TI

公司的

TMS320C6678

这一款多核

DSP

作为运动控制板卡的核心 处理器。

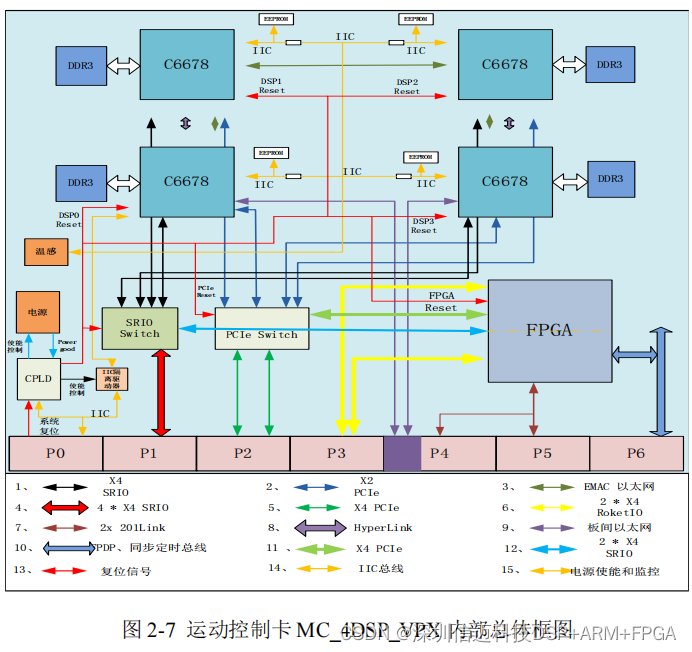

2

)运动控制卡(

MC_4DSP_VPX

)

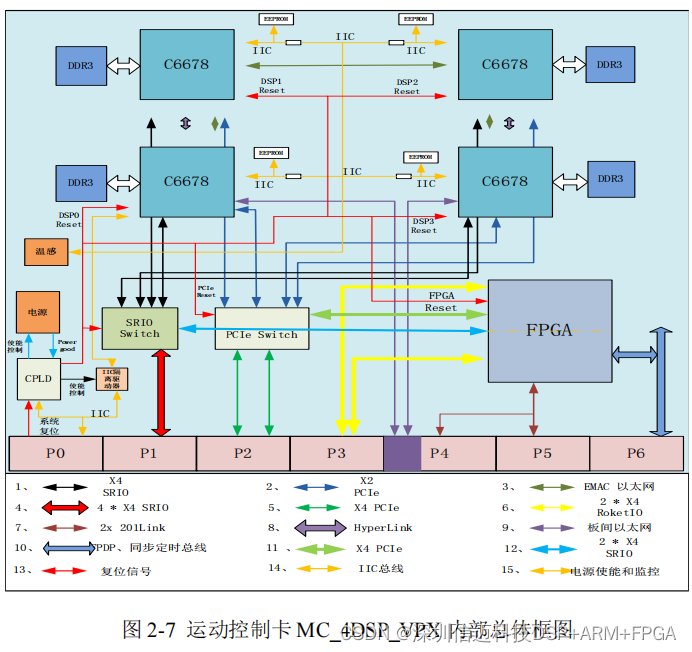

运动控制卡

MC_4DSP_VPX

是一块通用的

6U VPX

板卡。考虑到系统的扩展 性,例如后期需要融入对准系统,曝光系统等子系统,单板采用集成 4

片

C6678

和 1 片

K7 FPGA

的方案,增加系统处理器的冗余度。每片

C6678

芯片可外挂

4GB

的 DDR3,单板总存储容量可高达

16GB

,实现海量数据的存储,可使用于大规模实 时信号处理。单板内部总体框图及实物图如图 2-7

、图

2-8

所示。 运动控制卡 MC_4DSP_VPX

部分资源如下所述:

板载

4

片

C6678

处理芯片,工作频率最高为

1.25GHz

,一般保守设置为

1GHz

, 2 片

C6678

芯片作为

1

个处理节点,其间通过互连总线

Hyperlink

实现通信;

每片

C6678

和

FPGA

与

RapidIO Switch

的互连分别通过

1

路

X4 RapidIO

接口 和 2

路

X4 RapidIO

接口实现,

RapidIO Switch

提供

4

路

X4 RapidIO

接口,与VPX 背板的

P1

口相连,则多块板卡则通过背板的

RapidIO

总线和

P1

口实现数据传输。

2.2.3

光纤接口卡(

FC_FPGA_VPX

)

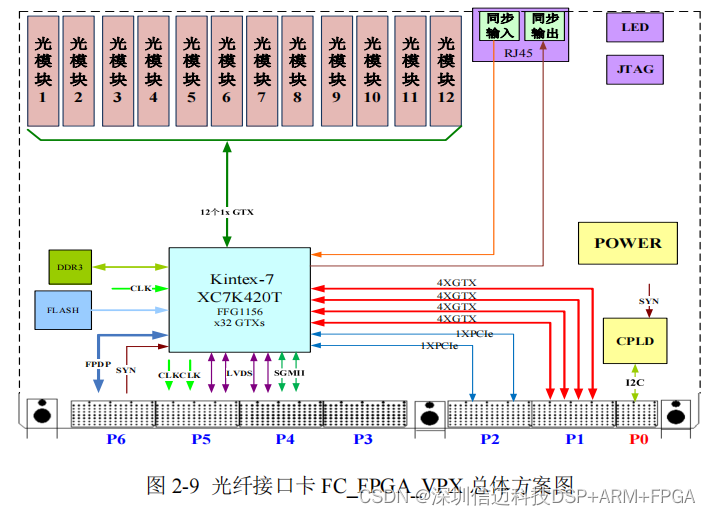

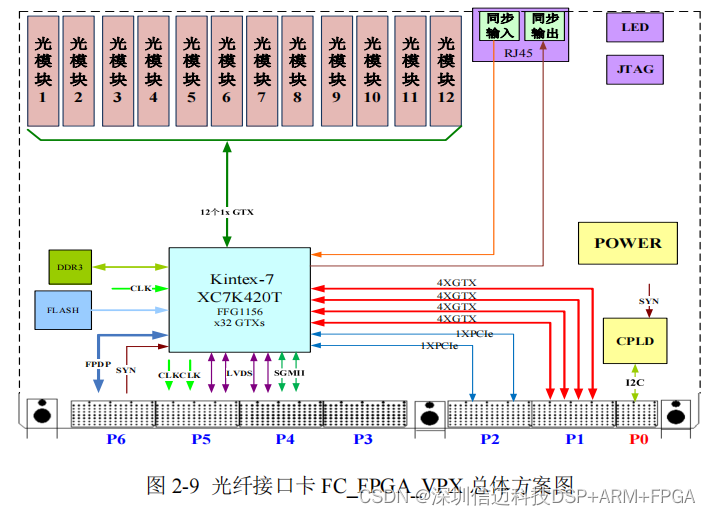

正如

2.1.2 节中提到的光纤接口数量受限问题,本文方案拟将光纤接口与运动控制处理 卡 分离, 所 有 的 光 纤 接 口 接 口 集 成 于 单 块 板 卡 。 光纤接口 卡(FC_FPGA_VPX)由硬件公司根据实验室需求完全定制设计,板上使用 1 片 K7FPGA 实现光纤接口的管理。常用接口包括:前面板 12 个协议可定义光口,同步信号输入输出接口、JTAG 接口等。参考方案框如图 2-9 所示:

光纤接口卡

FC_FPGA_VPX

部分资源如下所述:

P1

:

K7 FPGA

提供

4

个

x4 GTX

;

P2

:

K7_FPGA

提供

2

个

x1 PCIe

;

P4

:

K7 FPGA

提供多路

LVDS

差分对,

2

个

Ethernet

;

P5

:

K7 FPGA

提供多路

LVDS

差分对,并根据要求定义;;

P6

:

K7 FPGA

提供系统

SYN

信号及

32bit

自定义总线;

前面板提供

12

路光纤,采用

SFP

接口形式,提供

LED

指示通断;

前面板提供

1

路输出同步定时信号,

1

路输入同步定时信号,采用

RJ45

接口

形式;

2.2.4

主控卡(

HOST_CPU_VPX

)

主控卡

HOST_CPU_VPX

拟选用

PPC

(

TBD

)结构,根据项目要求所提的部

分资源需求描述如下:

主控单元

CPU

采用高性能

PowerPC

;

内存:

8 GB DDR3 (1600 MHz)

;

硬盘采用

256G

固态硬盘;

1

片

PCIE

转

RapidIO Switch

;

支持

VxWorks6.8

操作系统;

对外接口

前面板

3

个

USB2.0

接口;

前面板

2

个

RJ-45

输出千兆以太网;

前面板

1

个

VGA

视频输出接口;

背板

2

个

4XRapidIO

。

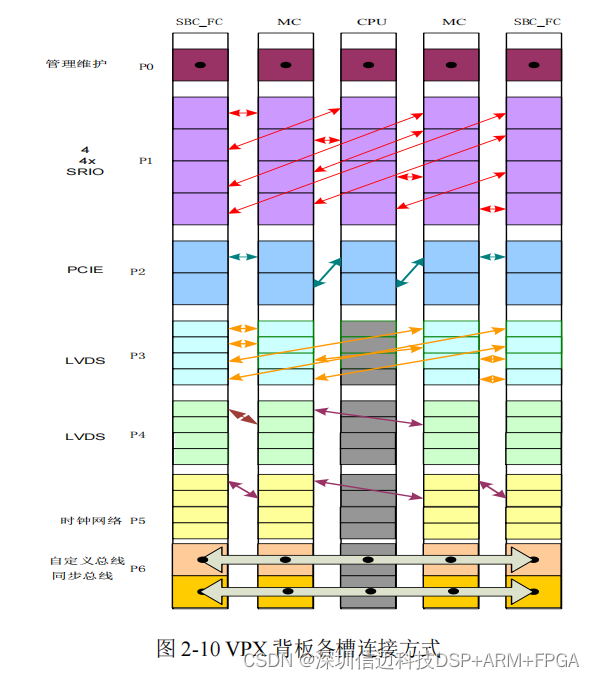

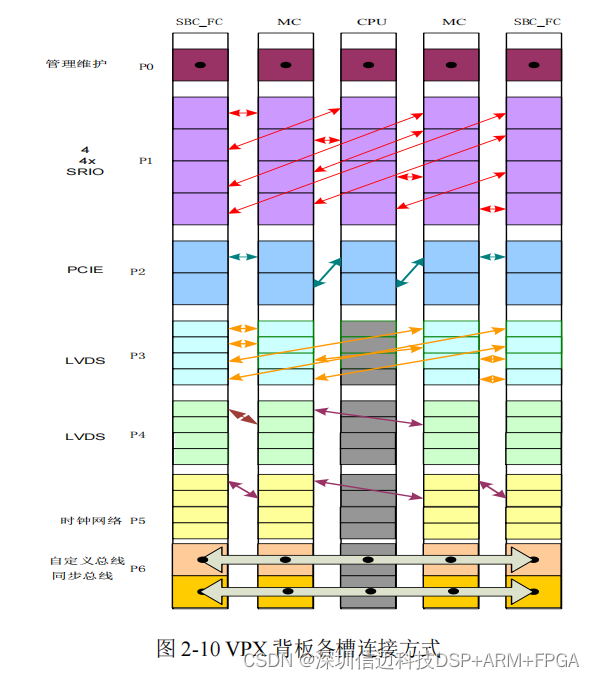

2.2.5 VPX

机箱背板

VPX

机箱背板是系统数据传输链路,是各功能模块之间的数据交互的基础,

承载着系统全部功能模块,除了给各个模块供电,还为各模块间的数据高速传输提

供通道,并为外接信号提供接口等。根据拓扑结构,

VPX

背板可以是星型、双星

型、菊花链型和孔网型等。

实验室所定制的

VPX

机箱采用

6U

加固式机箱,背板共有

6

个槽位,包括

1

个电源槽和

5

个处理模块槽,其中,

3

槽为主控槽,

1,2,4,5

槽为负载槽。背板各槽

的连接方式如图

2-10

所示。

VPX

机箱背板部分资源描述如下所述:

主控槽

P0

,

P1

,

P2

与其它板卡互连,

P3

,

P4

,

P5

,

P6

与其它板卡不互连,预

留为后插卡;

P0

:主电源采用

+12V

供电、

+5V

供电、系统管理和复位等;

P1

:

4

个

4X RapidIO

组成

FULLMESH

拓扑;

P4

上每个负载槽有

2

路千兆以太网;

P4

和

P5

:可作为

4

个

4XTS201LINK

接口使用,也可作为

32

对高速

LVDS

信

号使用;

P6

上定义了

32bit

自定义总线和

23bit

同步单端定时总线。

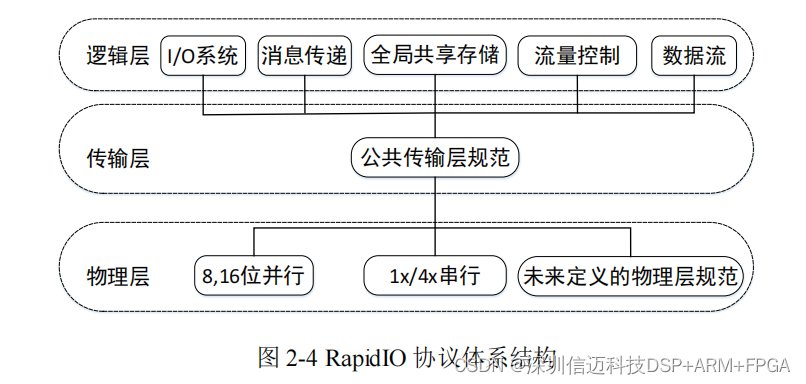

2.3

基于

RapidIO

总线的控制系统硬件体系结构设计

2.3.1

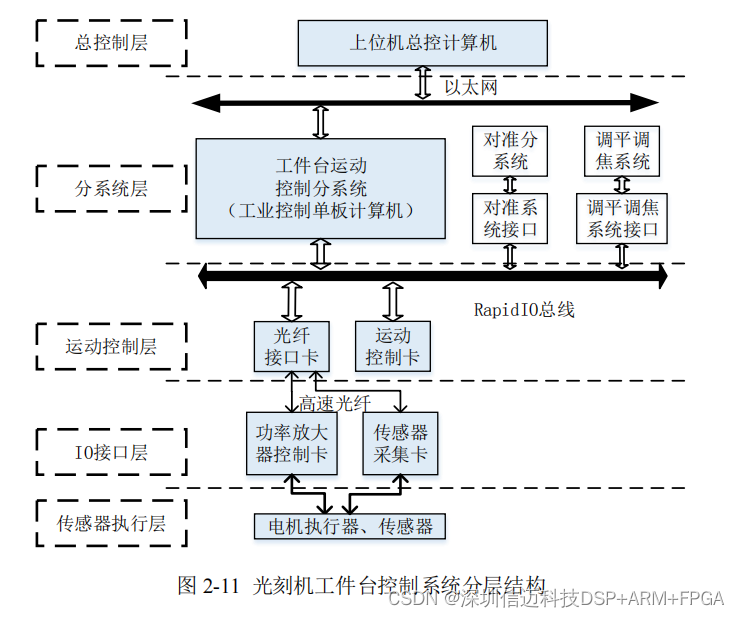

控制系统总体层次结构划分

由于工件台整机系统非常复杂,涉及的传感器和电机轴特别多,因此通过采用

主从结构,对系统进行分层设计,分析各部分的关联程度,将不同的部分合理部署

在相应的层次中。如图

2-11

所示,光刻机工件台整体运动控制系统共规划了五层,

从上之下依次是总控制层、分系统层、运动控制层、

IO

接口层和传感器执行器层,

各层控制结构的具体功能

[36]

如下:

1

)总控制层即上位机监视器,不仅提供人机交互界面,进行运行操作、测试

诊断、数据记录与存储、数据分析等工作,而且通过与分系统层进行数据交互,实

现对各个分系统的工作指令调度及协调管理,完成工件台的工作流程。

2

)分系统层主要包含工件台运动控制分系统、对准分系统等各个分系统的主

控制器,负责对各个分系统的软硬件管理及任务调度等。在工件台运动控制分系统,

主控卡为

Power PC

板卡,其工作在主模式,对工件台运动控制层的从设备进行管

理与调度。通过以太网(

Ethernet

)与上位机通信,实现命令接收、命令解析、任

务调度以及上传数据等任务。

3

)运动控制层包含有工作台运动控制卡、光纤接口卡和激光计数卡,相对于

主控卡

HOST_CPU_VPX

,工作在从模式,主要负责各控制台运动轴的闭环伺服控

制。其中,运动控制卡主要实现相关伺服运算以及与分系统层通讯完成命令解析与

功能执行;光纤接口卡作为数据交互中心,为各种数据提供的外围接口,负责位置

数据的接收,数据的传输,计算结果的输出;激光计数卡则同步采集激光数据。

4

)

IO

接口层由功率放大器控制卡(驱动器)和传感器卡组成。功率放大器控

制卡通过高速光纤接收运动控制层的控制指令,并转化成电流,实现对电机的驱动,

而传感器卡将采集的多种传感器信号通过光纤上传至运动控制层。

5

)传感器执行器层的设备主要是各种传感器和电机,负责实现物理信号(位

置、温度、力等)的采集以及电机的驱动。

2.3.2

基于

RapidIO

总线的控制系统架构

考虑到目前

DSP

性能的极大提高,特别是保持与前期工作的兼容性,充分利

用已有成果经验,避免较大幅度的方案变动,总控制层、

IO

接口层和传感器执行

器层基本沿用了

VME

系统的部分技术方案,依旧使用一台

VME

系统完成激光双

频干涉信号的处理,与运动控制侧之间采用高速光纤连接。

运动控制子系统则根据控制系统分层结构,并针对所提出的问题和需求,采用

如图

2-12

所示的结构方案。方案中运动控制侧机箱采用

VPX

系统,并结合

ASML

和华中科技大学等高校研制的基于

VME

总线的运动控制系统架构的优点,将

RapidIO

总线作为运动控制卡

MC_4DSP_VPX

和光纤接口卡

FC_FPGA_VPX

互连

通信网络,具体优点体现在一下几点:

1

)运动控制卡

MC

采用高性能的多核处理器

TMS320C6678

,一方面提高了主频,

另一方面多

DSP

多核大规模并行处理模式极大增强了系统的运算能力。

2

)运动控制卡

MC

采用

DSP

处理器与光纤接口模块分离式设计,独立的光纤接口

卡增加了光纤接口数量以及提高了连线灵活性,避免了系统数据流不合理现象。

3

)将

VME

总线和

PDB

总线替换成

RapidIO

总线和

UDB 总线,运动控制卡和光

纤接口卡之间采用

RapidIO

互连通信,由于总线带宽极大提升以及,无须担心总线

拥堵等问题,而且通过

UDB

总线自行构建合理的时钟网络。