目录

基础语法

VL1 四选一多路器

VL2 异步复位的串联T触发器

VL3 奇偶校验

VL4 移位运算与乘法

VL5 位拆分与运算

VL6 多功能数据处理器

VL7 求两个数的差值

VL8 使用generate…for语句简化代码

VL9 使用子模块实现三输入数的大小比较

VL10 使用函数实现数据大小端转换

组合逻辑

VL11 4位数值比较器电路

VL12 4bit超前进位加法器电路

时序逻辑

VL21 根据状态转移表实现时序电路

VL22 根据状态转移图实现时序电路

VL23 ROM的简单实现

VL24 边沿检测

基础语法

VL1 四选一多路器

思路1:case语句(4路以上用case更方便)

case(sel)

2'b00: mux_out = d3;

2'b01: mux_out = d2;

2'b10: mux_out = d1;

2'b11: mux_out = d0;

default:mux_out = 2'bxx;

endcase思路2:三目运算符

assign mux_out = (sel==2'd0)?d3:((sel==2'd1)?d2:((sel==2'd2)?d1:(d0)));VL2 异步复位的串联T触发器

T触发器功能:

当输入端T=0时,时钟脉冲到达触发器保持原态不变;

当输入端T=1时,每来一个时钟脉冲触发器的状态翻转一次。

信号示意图:

VL3 奇偶校验

奇偶校验概念:

奇校验:就是让原有数据序列中(包括你要加上的一位)1的个数为奇数

1000110(0)你必须添0这样原来有3个1已经是奇数了所以你添上0之后1的个数还是奇数个。

偶校验:就是让原有数据序列中(包括你要加上的一位)1的个数为偶数

1000110(1)你就必须加1了这样原来有3个1要想1的个数为偶数就只能添1了。

缺点:1位误码能检测出,2位及2位以上检测不出来,而且不能纠错。

思路:^a操作,可以检测a中的“1”是否为奇数;

若a=100,^a=1^0^0=1,则1的数量为奇数,

若a=1100,^a=1^1^0^0=0,则1的数量为偶数。

assign check_ji = ^bus; //每个位相异或,

assign check = (sel == 1) ? check_ji : ~check_ji;

VL4 移位运算与乘法

在硬件中进行乘除运算比较消耗资源,因此我们采用移位操作。

out <= d_reg + {d_reg ,1'b0}; //1+2=3

out <= d_reg + {d_reg,1'b0} + {d_reg,2'b0}; //1+2+4=7

out <= {d_reg,3'b0}; //8*d_reg

vivado仿真图:

VL5 位拆分与运算

注意:

wire变量只能用于组合逻辑中的assign语句(组合逻辑的always语句中不能用);

reg型变量用于时序逻辑中的always语句。

所以要注意看 该题设定好了输出变量类型,意味着要用下图设计方法。

VL6 多功能数据处理器

if else即可完成

VL7 求两个数的差值

if else即可完成,要注意if eles的赋值语句超过1个,就要加begin...end

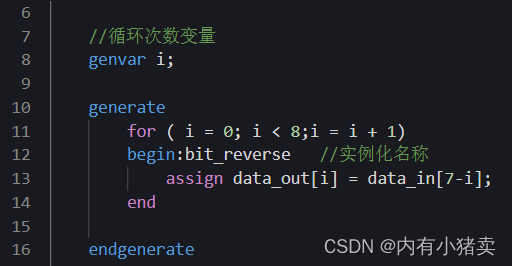

VL8 使用generate…for语句简化代码

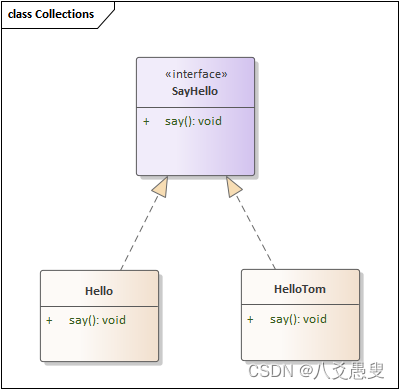

1、作用:generate…for是用于简化代码,

2、generate…for和for循环的区别:

generate-for只针对于module、regnet、assign、always、parameter、function.initial.task等语匀或煮模块,而g只针对打美例化的踊坎

3、使用方式:

4、举例模板:

5、本题实现代码