动态 RAM(DRAM)的刷新

-

刷新的过程实质上是先将原存信息读出,再由刷新放大器形成原信息并重新写入的再生过程

-

根据这个特点,可以估计刷新电路执行趟耗费的时间大致和访存时间相当

-

刷新放大器及读放大器均起此作用

-

由于存储单元被访问是随机的,有可能某些存储单元长期得不到访问,不进行存储器的读/写操作,其存储单元内的原信息将会慢慢消失。

-

为此,必须采用定时刷新的方法,它规定在一定的时间内,对动态 RAM 的全部基本单元电路必作一次刷新,一般取 2 ms,这个时间称为刷新周期,又称

再生周期。- 也就是说,每2ms( 2000 μ s 2000\mu{s} 2000μs)的时间间隔内,至少需要完成一次全单元刷新操作

-

刷新是

一行行进行的- 必须在

刷新周期内,由专用的刷新电路来完成对基本单元电路的逐行刷新,才能保证动态RAM内的信息不丢失。 - 同一行的所有单元同时执行刷新

- 不同行之间则是串行进行刷新

- 如果某个存储芯片有n行,刷新一行耗时和存取周期一致t=0.5us,那么刷新该芯片耗费时间nt

- 也就是,2ms=2000(us)的时间间隔内,有nt=0.5n(us)的时间用于刷新,还有(2000-0.5n)us的时间可以用于非刷新目的访存

- 在上述前提下,不同的访存时机分配方式对应不同的刷新方式

- 芯片的不同行不一定要连续刷新,只要在2ms内得到刷新即可

- 必须在

-

-

刷新操作不依赖于芯片最近是否被访问过(只要DRAM芯片上有数据,就要刷新维护,以便随时取用)

记号

-

为了便于描述:

- 将刷新操作记为REF操作(refresh,简称R操作)

- 将非刷新的操作(读/写/维护)记为M操作

- DRAM的读是破坏性的读,所以读完数据需要维护(再生)

- 这个操作必须紧跟在读操作之后,而不是等待统一刷新(来不及)

- 刷新只能够处理(只负责处理)电容自发掉电的问题

- 破坏性读出的维护是另外根据访存情况执行的(也认为要耗费一个存取周期.)

-

通常有三种方式刷新:集中刷新、分散刷新和异步刷新。

集中刷新

-

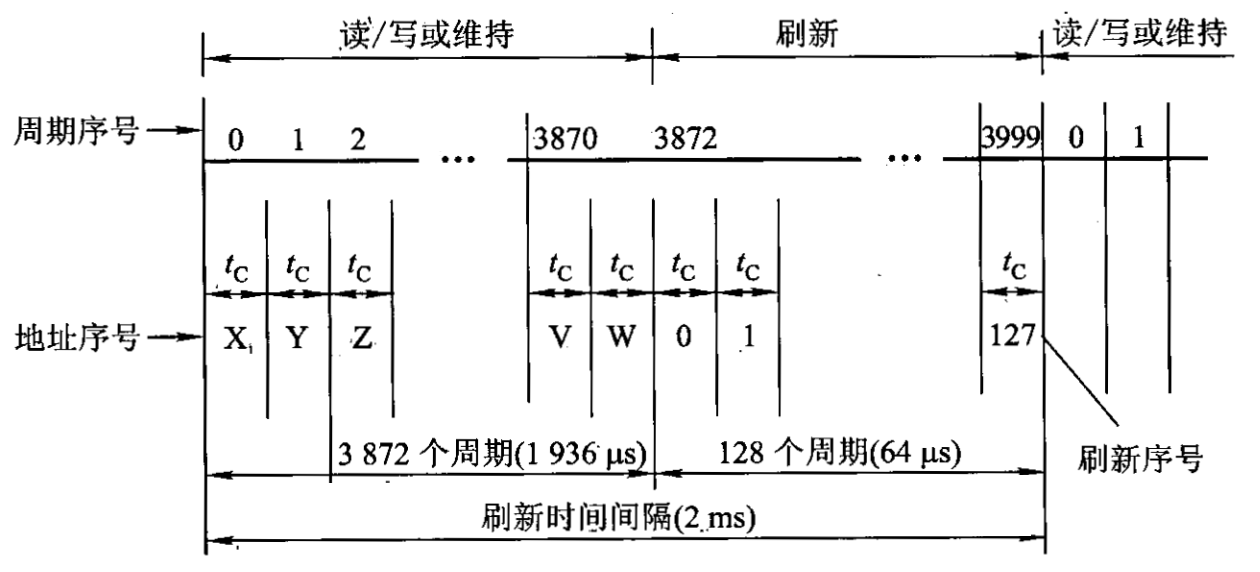

集中刷新是在规定的一个

刷新周期内,对全部存储单元集中一段时间逐行进行刷新,此刻必须停止读/写操作。-

例如,对 128× 128 矩阵的存储芯片A进行刷新时,

- 若存取周期为 0.5us,刷新周期为 2 ms(占 2 × 1 0 3 μ s 0.5 μ s \frac{2\times{10^3}\mu{s}}{0.5\mu{s}} 0.5μs2×103μs 4 000 个存取周期),

- 则对 n=128 行集中刷新共需nt=0.5*128= 64 us(占 128 个存取周期),

- 其余的 1936 us(相当于 3872 个存取周期)用来读/写或维持信息

-

由于在这 64 us 时间内不能进行读/′写操作,故称为“死时间”,又称访存“死区”,

- 所占比率为 128/4000 x 100%=3.2%,称为死时间率。

- t C t_C tC表示存取周期(cycle)

- 所占比率为 128/4000 x 100%=3.2%,称为死时间率。

-

分散刷新

-

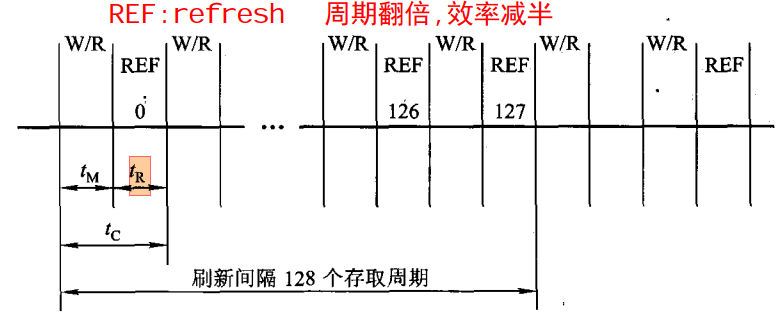

分散刷新:把对每行的刷新分散到各个工作周期中。

-

这样,一个存储器的系统工作周期(分为两部分:

- 前半部分用于正常读、写或保持(M操作);

- 后半部分用于刷新某一行(R操作)

- 更直白的说,每个时间间隔 t C t_C tC内的后半部分事件总是要执行刷新操作,无论前半部分做了什么

-

这种刷新方式增加了系统的

存取周期,如存储芯片的存取周期为 0.5us,则系统的存取周期为 1us。 -

分散刷新的优点是没有死区;

-

缺点是加长了

系统的存取周期,降低了整机的速度- 本例中,分散刷新每隔127us,就可以对所有存储单元完成一遍刷新

- 这个频率高于我们的最低要求2ms(2000us内可以被刷新了15次左右,而实际上我们只需要刷新一次即可)

- 多刷新的十几遍,造成了效率低下,为了解决这个问题,使用异步刷新来改善

-

-

t c = t M + t R t_{c}=t_{M}+t_{R} tc=tM+tR

-

t c 表 示 新 的 系 统 存 取 周 期 ; t M 表 示 读 写 或 维 护 操 作 时 间 ; t R 表 示 刷 新 操 作 时 间 t_{c}表示新的系统存取周期;t_{M}表示读写或维护操作时间;t_{R}表示刷新操作时间 tc表示新的系统存取周期;tM表示读写或维护操作时间;tR表示刷新操作时间

异步刷新

-

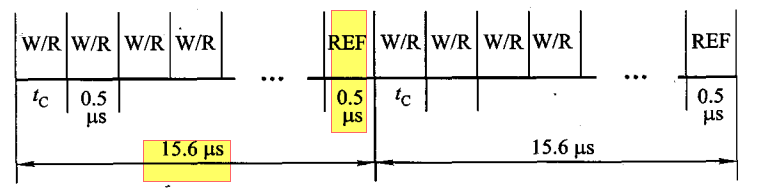

异步刷新是前两种方法的结合,它既可缩短“死时间”,又能充分利用最大刷新间隔为 2ms 的特点。

-

具体做法是将刷新周期2000us除以存储芯片A的行数n

- 得到的值就是两次刷新操作之间的时间间隔 t

- 利用逻辑电路每隔时间 t 产生一次刷新请求。

-

这样可以避免使 CPU 连续等待过长的时间,而且减少了刷新次数,从根本上提高了整机的工作效率。

-

异步刷新是前两种方式的结合,它既可缩短“死时间”,又充分利用最大刷新间隔为 2 ms 的特点

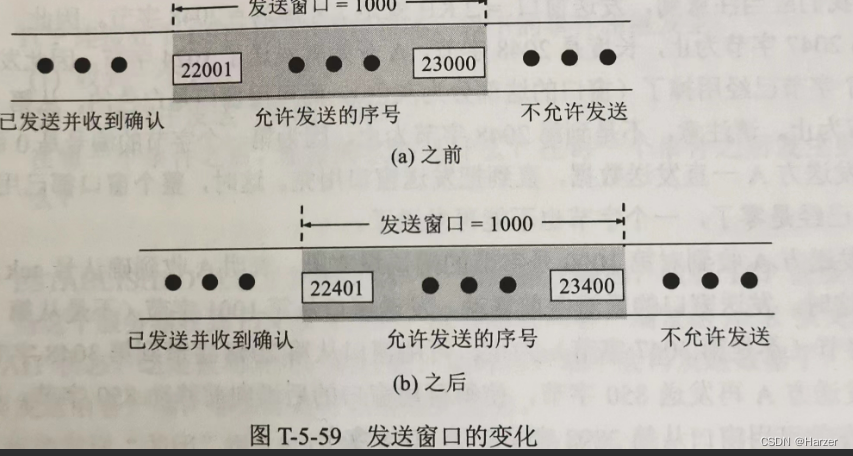

- 例如,对于存取周期为 0.5us,排列成 128×128 的存储芯片,采取在 2 ms 内对 128 行单元各刷新一遍(且仅一遍),即每隔 15.6 us(2 000 us / 128us=15.6 us)刷新一行,这样2000us后恰好能够对所有行完成一遍刷新

每行刷新的所需时间仍为 0.5 us- 我们也可以称, t L = t R t c t_L=\frac{t_R}{t_c} tL=tctR是行刷新周期(其中 t R t_R tR是芯片所有行完成刷新的时间)

-

这样,刷新一行只停止一个存取周期,但

对每行来说,刷新间隔时间仍 2ms.而死时间缩短为 0.5 us。 -

summary

DRAM 的刷新需注意以下问题:

-

刷新

对CPU是透明的,即刷新不依赖于外部的访问(刷新不占用 cpu 资源,但是会在 DRAM 刷新的时候阻碍 cpu 对存储的访问); -

动态 RAM 的刷新单位是行,因此刷新操作时仅需要行地址;

-

刷新操作类似于读操作,但又有所不同。

- 刷新操作仅给栅极电容补充电荷,不需要信息输出。

-

刷新时不需要选片,即整个存储器中的所有芯片同时被刷新。

DRAM的读写周期

相关缩写:(Principles of operation )

-

An asynchronous DRAM chip has power connections,

- some number of address inputs (typically 12),

- and a few (typically one or four) bidirectional data lines.

-

There are four active-low (有效低电平)control signals:

-

RAS, the Row Address Strobe.

- The address inputs are captured on the falling edge of RAS, and select a row to open.

- The row is held open as long as RAS is low.

-

CAS, the Column Address Strobe.

- The address inputs are captured on the falling edge of CAS,

- and select a column from the currently open row to read or write.

-

WE, Write Enable.

- This signal determines whether a given falling edge of CAS is a read (if high) or write (if low).

- If low, the data inputs are also captured on the falling edge of CAS.

-

OE, Output Enable.

- This is an additional signal that controls output to the data I/O pins.

- The data pins are driven by the DRAM chip if RAS and CAS are low, WE is high, and OE is low.

- In many applications, OE can be permanently connected low (output always enabled)

- but switching OE can be useful when connecting multiple memory chips in parallel.

-

-

This interface provides direct control of internal timing.

-

When RAS is driven low, a CAS cycle must not be attempted until the sense amplifiers have sensed the memory state, and RAS must not be returned high until the storage cells have been refreshed.

-

When RAS is driven high, it must be held high long enough for precharging to complete.

-

Although the DRAM is asynchronous, the signals are typically generated by a clocked memory controller, which limits their timing to multiples of the controller’s clock cycle.(限制为控制器时钟周期的倍数)

R A S ‾ \overline{RAS} RAS

- R A S ‾ \overline{RAS} RAS(行地址选通,低电平有效)

C A S ‾ \overline{CAS} CAS

- C A S ‾ \overline{CAS} CAS列地址选通,低电平有效

W E ‾ \overline{WE} WE

- W E ‾ \overline{WE} WE写允许信号

周期解释

- 在读周期中,为了使得DRAM芯片能够正确接收行地址和列地址

- 在 R A S ‾ \overline{RAS} RAS有效前,将行地址送到芯片的地址引脚

-

C

A

S

‾

\overline{CAS}

CAS滞后

R

A

S

‾

\overline{RAS}

RAS一段时间,类似的,

- 在 C A S ‾ \overline{CAS} CAS有效前,将列地址送到芯片的地址引脚

- R A S ‾ \overline{RAS} RAS和 C A S ‾ \overline{CAS} CAS至少保持 t R A S 和 t C A S t_{RAS}和t_{CAS} tRAS和tCAS的时间

- 在读周期中, W E ‾ \overline{WE} WE为高电平,并在 C A S ‾ \overline{CAS} CAS有效前建立

存储芯片的架构

存储芯片的内部结构

- 存储芯片有由一下几个部分组成

- 存储体(存储矩阵)

- 是存储单元的集合

- 有行选线X和列选线Y来选择所访问的单元

- 存储体相同行/列上的位被同时读出/写入

- 读写控制电路(I/O)

- 用以控制被选中的单元的读出/写入,具有放大信息的作用

- 地址译码器

- 将地址转换为译码输出线上的高电平,以便驱动相应的读写电路

- 控制电路

- 片选控制信号

- 由于单个存储芯片的容量往往不够

- 需要用一定数量的芯片进行存储器扩展

- 在访问某个字的时候,必须选该字所在存储芯片

- 同时,其他芯片不被选中

- 读/写控制信号

- 根据CPU给出的读命令/写命令(读写控制信号,通过控制线传递给读写控制电路),控制被片选中单元进行读/写

- 数据线的宽度和MDR相同

- 例如,64位的数据线,在按字节编址方式下,每次最多可以存取64bit(8个字节(8个存储单元))的内容

- 地址线的宽度和MAR相同

- 决定了主存地址空间的最大可寻址范围

- 例如,36位地址的最大可寻址地址范围为 0 ∼ 2 36 − 1 , 共 有 2 36 个 不 同 地 址 0\sim{2^{36}-1},共有2^{36}个不同地址 0∼236−1,共有236个不同地址

- 片选控制信号

- 存储体(存储矩阵)

地址引脚复用技术

- 为了减少芯片的地址引脚,采用地址引脚复用技术,行地址和列地址通过相同的引脚分先后两次输入

- 地址引脚数可以减少一般

存储体容量

- 数据线位数m和地址线位数n共同反映存储体容量大小

- 最大为 2 n ⋅ m 2^{n}\cdot{m} 2n⋅m

ROM

- ROM和RAM都是可以随机存取的存储器

- ROM结构简单,具有更高的位密度

- 具有非易失性,可靠性较高

ROM类型

- 掩模式只读存储器MROM

- 写入内容后无法改变

- 由半导体制造商更加客户要求写入

- 一次可编程只读存储器PROM

- 可以一次性编程

- 用写入设备写入一次后,内容无法改变

- 由用户用专门的设备写入

- 可擦除可编程只读存储器EPROM

- 这里的只读已经不是真的只读

- EPROM即可读又可写

- 但是写的次数和写入速度不如RAM

- Flash存储器

- 在EPROM和EEPROM( E 2 P R O M E^2PROM E2PROM)的基础上发展而来

- Flash价格便宜,集成度高,擦除重写速度快

- 固态硬盘SSD

- 固态电子存储芯片阵列制成的硬盘

- 由控制单元和存储单元(Flash芯片)组成

- 具有长期保存信息,快速擦除与重写的特性

- 速度快,功耗低

- 价格高

半导体存储芯片的基本结构

-

半导体存储芯片采用超大规模集成电路制造工艺,在一个芯片内集成具有记忆功能的存储矩阵、译码驱动电路和读/写电路等

-

译码驱动能把地址总线送来的地址信号翻译成对应存储单元的选择信号,该信号在读/写电路的配合下完成对被选中单元的读/写操作。 -

读/写电路包括读出放大器和写入电路,用来完成读/写操作。- 存储芯片通过

地址总线﹑数据总线和控制总线与外部连接。

- 存储芯片通过

-

数据线的位数与芯片容量

有关,地址线和数据线的位数共同反映存储芯片的容量。地址线是单向输入的,其位数与芯片容量有关。数据线是双向的(有的芯片可用成对出现的数据线分别作为输入或输出),- 其

位数与芯片可读出或写入的数据位数有关。 - 例如,地址线为 10 根,数据线为 4 根,则芯片容量为 2 10 × 4 2^{10}\times4 210×4 K 位;

- 如地址线为 14 根,数据线为 1 根,则其容量为 2 14 = 2 4 × 2 10 = 16 k 2^{14}=2^{4}\times2^{10}=16k 214=24×210=16k位。

-

控制线- 主要有

读/写控制线与片选线,两种。 - 读/写控制线决定芯片进行读/写操作,

片选线用来选择存储芯片。 - 不同存储芯片的读/写控制线和片选线可以不同。

- 有的芯片的

读/写控制线共用 1 根(如芯片2114) ,有的分用两根(如 6264) ; - 有的芯片的

片选线用1根(如芯片2114) ,有的用 2 根(如 6264)。

- 有的芯片的

- 由于半导体存储器是由许多芯片组成的,为此需用片选信号来确定哪个芯片被选中。

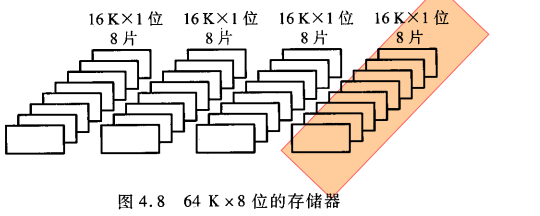

- 例如,一个 64K×8 位的存储器可由

32 片 16 Kx1 位的存储芯片组成 - 但每次读出一个存储字时,只需选中 8 片。

- 主要有

多模块存储器

- 多模块存储器是一种空间并行技术

- cpu的速度比存储器快,如果同时从存储器中读取n条指令,可以更充分利用cpu资源

- 利用多个结构完全相同的存储模块的并行工作来提高存储器的吞吐率

- 常用的方式有2种

- 将地址分为两部分低地址

- 高地址

- 低地址

单体多字存储器

- 一个存储体的每个存储单元包含m个字(总线宽度也为m字)

- 一次并行读出m个字

- 前提: 地址必须顺序排列并且处于同一个存储单元

- 在一个存取周期内,从同一地址取出m条指令,然后逐送至cpu

- 相当于, 1 m \frac{1}{m} m1个存取周期cpu就可以取得一条指令

多体并行存储器

-

此处将存储体芯片也称为模块

- 每个模块具有相同的容量和速度

- 假设存储器有m个模块,分别记为 M 0 ∼ M n − 1 M_0\sim{M_{n-1}} M0∼Mn−1

- 每个模块具有k个存储单元

-

高位交叉编址

- 这种方式依然是串行存取,不能提高存储器的吞吐率

-

低位交叉编址

- 高地址为存储体的体内地址

- 低地址为存储体的体号

- 每个模块按照

m

o

d

m

\mod{m}

modm交叉编址

-

模 块 号 i = 单 元 地 址 / m 模块号i=单元地址/m 模块号i=单元地址/m

- KaTeX parse error: Undefined control sequence: \set at position 5: i\in\̲s̲e̲t̲{0,1,\cdots{m-1…

-

地址为 0 , m , ⋯ ( k − 1 ) m 0,m,\cdots{(k-1)m} 0,m,⋯(k−1)m(等差数列)的存储单元位于同一个模块 M 0 M_0 M0

-

流水

-

cpu每次访问一个存储体(多模块中的一个)

-

从开始访问到结束对某个模块的访问需要的时间为存取周期 T c , 简 记 为 T T_c,简记为T Tc,简记为T

-

而将访问到的数据通过数据总线从存储器传输到cpu(MDR)中需要的时间,即传输周期为 T r , 简 称 为 r T_r,简称为r Tr,简称为r

-

假设

-

T=200ns;(每个存储体的存取周期)

-

r=50ns,(cpu经过时间r的延迟后,启动下个模块的访问)

-

从各个存储模块返回读取结果的角度看

-

它们间隔不能够比总线传输周期r小(总线的分时特性)

-

同时由于每个存储体的性能一样(存取周期一样)

- 所以对应于它们的启动时间,间隔也是至少为r

-

又考虑到cpu可能对同一个模块的多次访问,那么第二次访问到来之前必须保证前一次的访问任务结束

-

也就是说,第二次访问同一个模块 M i M_i Mi的时间距离第一次的时间间隔至少为存取周期 T c T_c Tc

-

-

模块字长等于数据总线的宽度

-

cpu对m=4体交叉存储器的访问可以是流水的

-

假设访问第一个存储体的时间点是0

-

cpu将它要读取的单元告诉给存储器后,有存储器的控制电路将数据传输给CPU

- 花费的主要时间在于存储器内部的工作电路上,这部分时间cpu无法为其加速

- 多体交叉存储器的每个芯片模块都具有独立的控制电路

-

时间过了200+50ns,cpu取得第一个数据(包括传输时间)

-

![[打卡笔记]-RK3399平台开发入门到精通系列视频-Linux 设备树](https://img-blog.csdnimg.cn/33e2b7858a1846b98d4e7be0dfe4fcb7.png)

![[附源码]java毕业设计医学季节性疾病筛查系统](https://img-blog.csdnimg.cn/2199f054587045c8929924cb012c784b.png)