别再乱用defparam了!Verilog参数传递的两种正确姿势(附避坑指南)

news2026/5/3 11:14:19

Verilog参数传递的工程实践从语法规范到项目级解决方案在数字电路设计领域参数化设计是提升代码复用性和可维护性的关键手段。当我们需要在多个场景下复用同一模块但需要调整其内部特性时参数传递机制就显得尤为重要。本文将深入探讨Verilog中两种主流参数传递方式的工程实践帮助开发者规避常见陷阱建立规范化的参数管理策略。1. 参数化设计的核心价值与应用场景参数化设计绝非仅仅是语法层面的技巧而是直接影响项目开发效率和代码质量的工程实践。想象一下当你需要设计一个可配置的FIFO模块其深度和宽度可能根据应用场景不同而变化。如果没有参数化机制我们可能需要为每个配置创建独立的模块文件——这显然会导致代码库膨胀和维护噩梦。参数传递在实际项目中的典型应用场景包括IP核配置在复用第三方IP时调整其内部参数仿真加速通过修改时序参数缩短验证周期工艺适配针对不同工艺节点调整电路特性模式切换同一模块在不同工作模式下的行为配置// 典型参数化模块声明示例 module configurable_fifo #( parameter DEPTH 1024, parameter WIDTH 32, parameter AFULL_THRESH 950 ) ( input wire clk, input wire rst_n, // ...其他端口声明 );提示良好的参数命名规范应该做到见名知义推荐使用全大写加下划线的命名方式如DATA_WIDTH而非简单的DW2. 例化时修改安全可靠的参数传递方式例化时修改参数是目前业界推荐的首选方式其核心优势在于作用域明确、可读性强且不易产生歧义。这种方式采用名称关联的语法在模块实例化的同时指定需要覆盖的参数值。2.1 标准语法与工程实践// 基础模块定义 module clock_divider #( parameter DIV_RATIO 4, parameter PHASE_SHIFT 0 ) ( input clk, input rst_n, output reg div_clk ); // 模块实例化时修改参数 clock_divider #( .DIV_RATIO(8), // 将分频比改为8 .PHASE_SHIFT(90) // 添加90度相移 ) u_pll_clock ( .clk(sys_clk), .rst_n(sys_rst_n), .div_clk(pll_clk) );在实际工程中我们建议遵循以下规范显式命名关联始终使用.PARAM_NAME(value)的形式避免依赖参数顺序参数分组将功能相关的参数组织在一起用注释说明其关系默认值设计为参数设置合理的默认值减少不必要的覆盖2.2 多层级参数传递策略在复杂系统中参数可能需要穿透多个层次进行传递。例化时修改的方式天然支持这种需求// 顶层模块 module soc_top #( parameter AXI_DATA_WIDTH 64, parameter DDR_CLK_FREQ 1600 ) ( // 端口声明 ); // 内存控制器实例化 memory_controller #( .BUS_WIDTH(AXI_DATA_WIDTH), .TARGET_FREQ(DDR_CLK_FREQ) ) u_mem_ctrl ( // 端口连接 ); endmodule这种方式确保了参数传递路径的透明性任何参数的来源都可以通过代码追溯极大降低了调试难度。3. defparam的潜在风险与限制场景虽然defparam语法提供了另一种修改参数的方式但其设计上的灵活性恰恰成为了项目维护的隐患。IEEE Verilog标准甚至将其标记为可能在未来版本中移除的特性这足以说明其问题所在。3.1 典型问题场景分析作用域污染是defparam最常见的问题。由于defparam可以在任何位置修改任何模块的参数这可能导致同一参数在多个文件被不同值覆盖参数修改点远离模块实例化位置难以追踪条件编译导致的参数值不确定性// 文件A.v defparam u_processor.CACHE_SIZE 1024; // 文件B.v可能在不同目录 defparam u_processor.CACHE_SIZE 2048; // 冲突覆盖层次化引用陷阱是另一个常见痛点。当使用defparam修改深层次模块参数时路径引用极易出错// 易错示例路径引用错误 defparam top.u_sub.u_ram.DEPTH 256; // 如果中间层次变更路径失效 // 正确但脆弱的写法 defparam top.u_sub[3].u_ram.DEPTH 256; // 依赖具体例化结构3.2 有限的安全使用场景在某些特殊情况下defparam仍可能被谨慎使用测试平台配置在仿真环境中集中配置DUT参数向后兼容维护遗留代码时的临时方案条件参数覆盖基于宏定义的灵活配置即使在这些场景下也应当建立严格的代码规范所有defparam语句集中放置在专门的文件中为每个defparam添加详细注释说明修改原因避免在RTL代码中使用defparam4. 工程级参数管理策略成熟的数字设计项目需要建立系统化的参数管理方法超越简单的语法选择。以下是经过验证的实践方案4.1 参数分类与标准化参数类型声明方式修改方式典型示例架构参数parameter例化时修改DATA_WIDTH,DEPTH工艺参数localparam不修改CLK_TO_Q仿真参数ifdef SIMULATION条件编译SIM_DELAY全局配置define配置文件GLOBAL_CLK_PERIOD4.2 基于Package的参数共享SystemVerilog引入的package特性为参数管理提供了更强大的工具// parameters_pkg.sv package bus_params_pkg; parameter AXI_DATA_W 64; parameter AXI_ADDR_W 32; parameter AXI_ID_W 4; endpackage // 使用端 module axi_master import bus_params_pkg::*; ( input logic [AXI_ID_W-1:0] id, // 其他端口 );这种方法特别适合大型SoC项目中跨模块共享的参数配置。4.3 参数验证与约束良好的工程实践应当包含参数值的有效性检查module fifo #( parameter DEPTH 1024, parameter WIDTH 32 ) ( // 端口 ); // 参数合法性检查 initial begin if (DEPTH 16) $error(FIFO深度不能小于16); if (WIDTH % 8 ! 0) $warning(数据宽度建议为8的倍数); end5. 调试技巧与常见问题排查即使遵循最佳实践参数相关的问题仍可能出现。以下是几个实用的调试技巧参数追踪使用$display在仿真开始时打印关键参数值initial $display(FIFO配置DEPTH%0d, WIDTH%0d, DEPTH, WIDTH);交叉探测在EDA工具中检查参数最终值Vivado: report_property -all [get_cells u_instance]Quartus: qreport -instance_parameters u_instance命名冲突排查当遇到意外的参数值时检查是否有多个defparam语句修改同一参数宏定义与参数名冲突不同文件中的同名参数版本控制策略对参数配置文件使用严格的版本管理为每次参数变更添加注释说明考虑使用配置管理系统跟踪参数变更历史在大型FPGA项目中我们曾遇到一个典型案例某关键时序参数在测试中表现正常但在实际部署时出现故障。最终发现是构建系统中一个条件编译标志错误地覆盖了参数值。这促使团队建立了强制性的参数审计流程——所有关键参数值必须在构建日志中明确记录并与设计文档进行交叉验证。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2578078.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

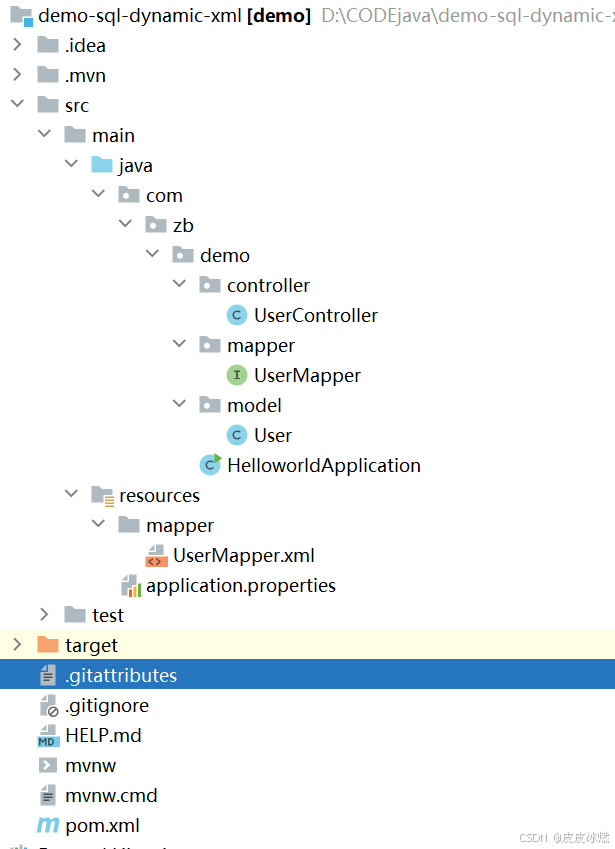

SpringBoot-17-MyBatis动态SQL标签之常用标签

文章目录 1 代码1.1 实体User.java1.2 接口UserMapper.java1.3 映射UserMapper.xml1.3.1 标签if1.3.2 标签if和where1.3.3 标签choose和when和otherwise1.4 UserController.java2 常用动态SQL标签2.1 标签set2.1.1 UserMapper.java2.1.2 UserMapper.xml2.1.3 UserController.ja…

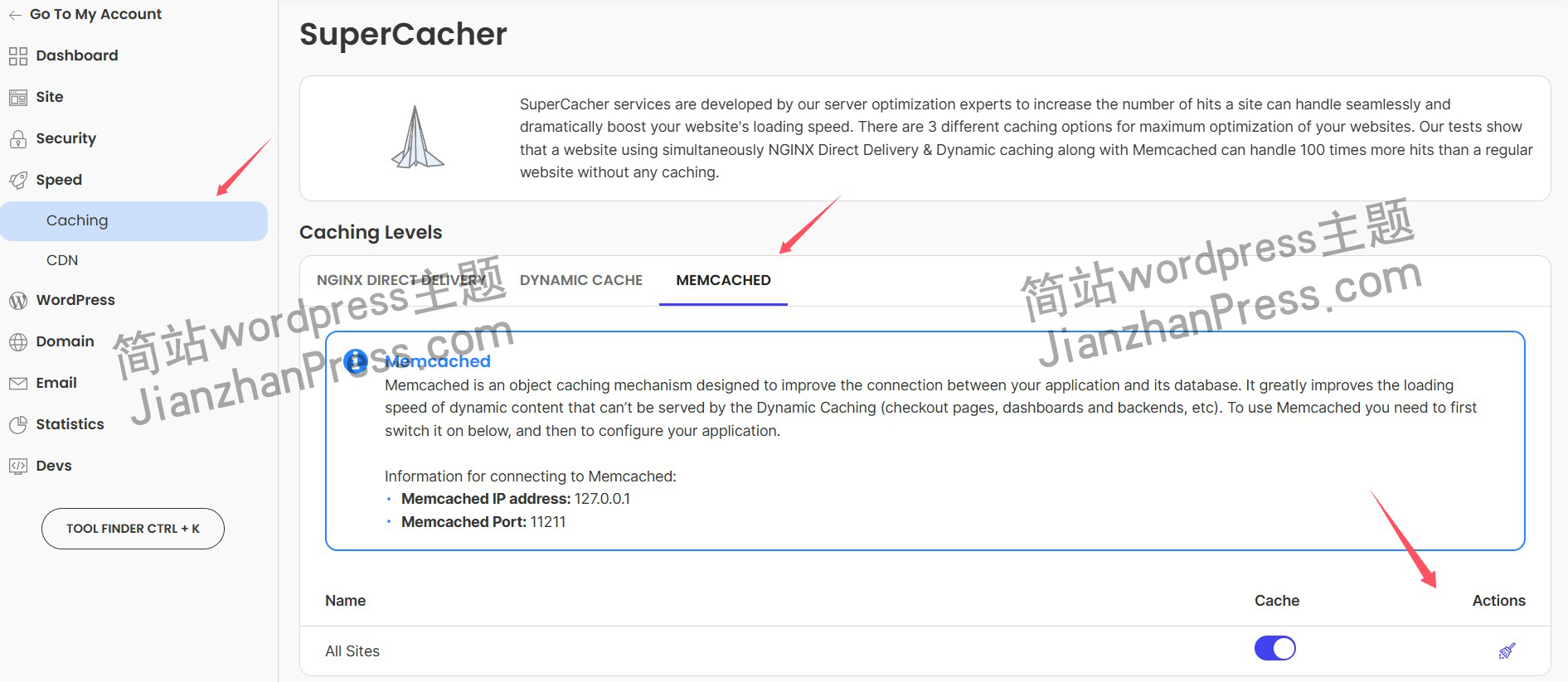

wordpress后台更新后 前端没变化的解决方法

使用siteground主机的wordpress网站,会出现更新了网站内容和修改了php模板文件、js文件、css文件、图片文件后,网站没有变化的情况。

不熟悉siteground主机的新手,遇到这个问题,就很抓狂,明明是哪都没操作错误&#x…

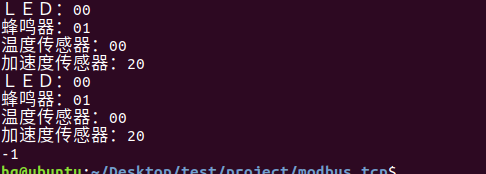

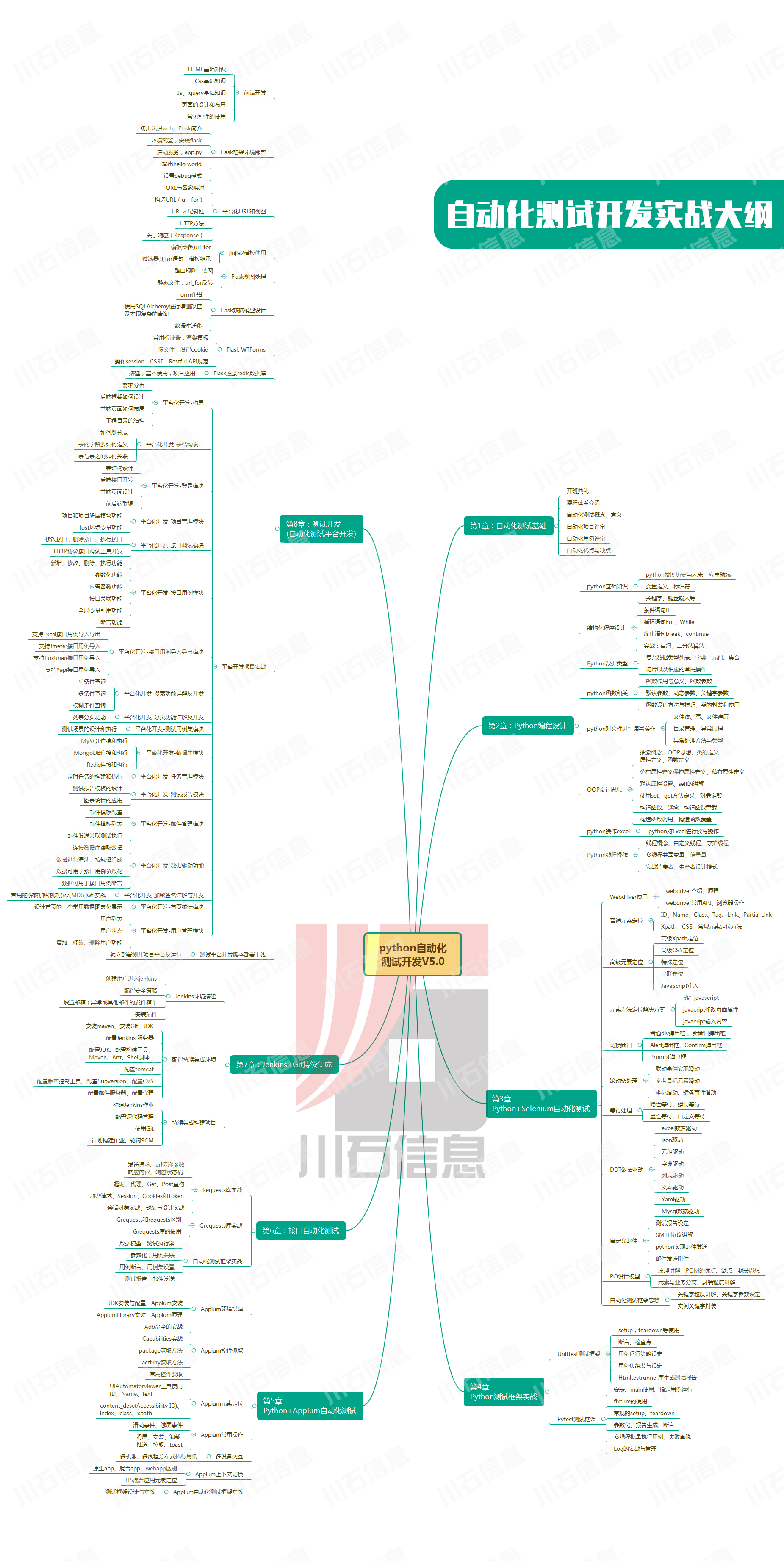

网络编程(Modbus进阶)

思维导图 Modbus RTU(先学一点理论)

概念 Modbus RTU 是工业自动化领域 最广泛应用的串行通信协议,由 Modicon 公司(现施耐德电气)于 1979 年推出。它以 高效率、强健性、易实现的特点成为工业控制系统的通信标准。 包…

UE5 学习系列(二)用户操作界面及介绍

这篇博客是 UE5 学习系列博客的第二篇,在第一篇的基础上展开这篇内容。博客参考的 B 站视频资料和第一篇的链接如下:

【Note】:如果你已经完成安装等操作,可以只执行第一篇博客中 2. 新建一个空白游戏项目 章节操作,重…

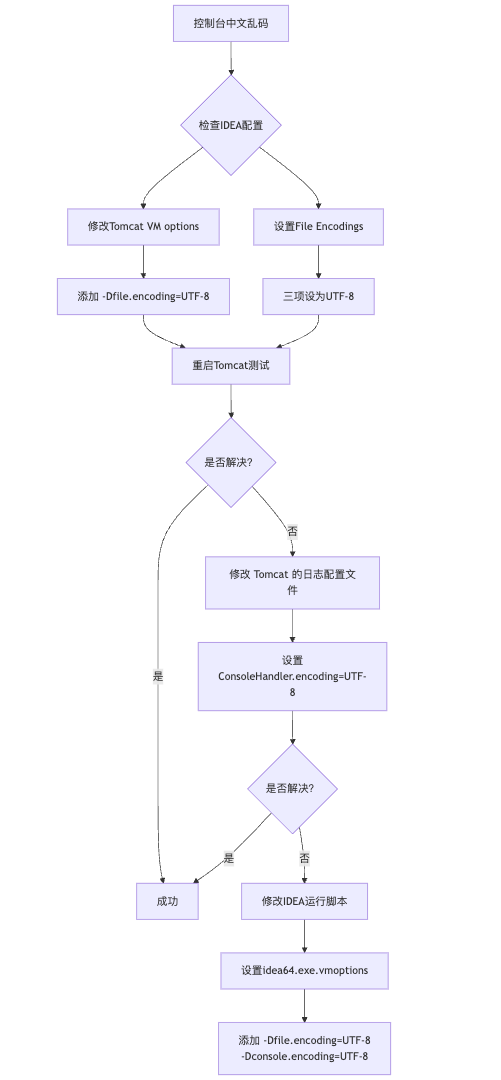

IDEA运行Tomcat出现乱码问题解决汇总

最近正值期末周,有很多同学在写期末Java web作业时,运行tomcat出现乱码问题,经过多次解决与研究,我做了如下整理:

原因:

IDEA本身编码与tomcat的编码与Windows编码不同导致,Windows 系统控制台…

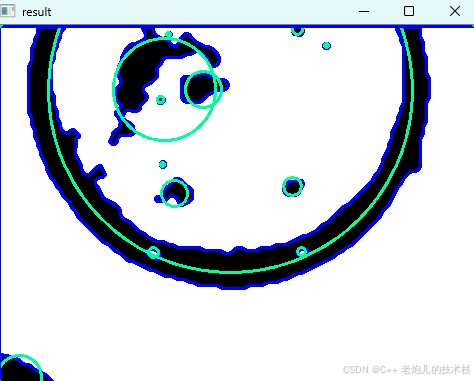

利用最小二乘法找圆心和半径

#include <iostream>

#include <vector>

#include <cmath>

#include <Eigen/Dense> // 需安装Eigen库用于矩阵运算 // 定义点结构

struct Point { double x, y; Point(double x_, double y_) : x(x_), y(y_) {}

}; // 最小二乘法求圆心和半径 …

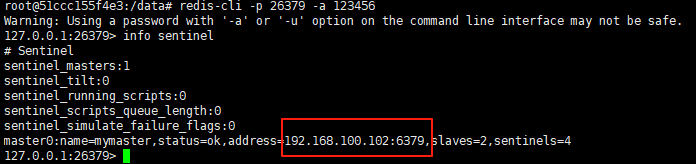

使用docker在3台服务器上搭建基于redis 6.x的一主两从三台均是哨兵模式

一、环境及版本说明

如果服务器已经安装了docker,则忽略此步骤,如果没有安装,则可以按照一下方式安装: 1. 在线安装(有互联网环境): 请看我这篇文章 传送阵>> 点我查看 2. 离线安装(内网环境):请看我这篇文章 传送阵>> 点我查看

说明:假设每台服务器已…

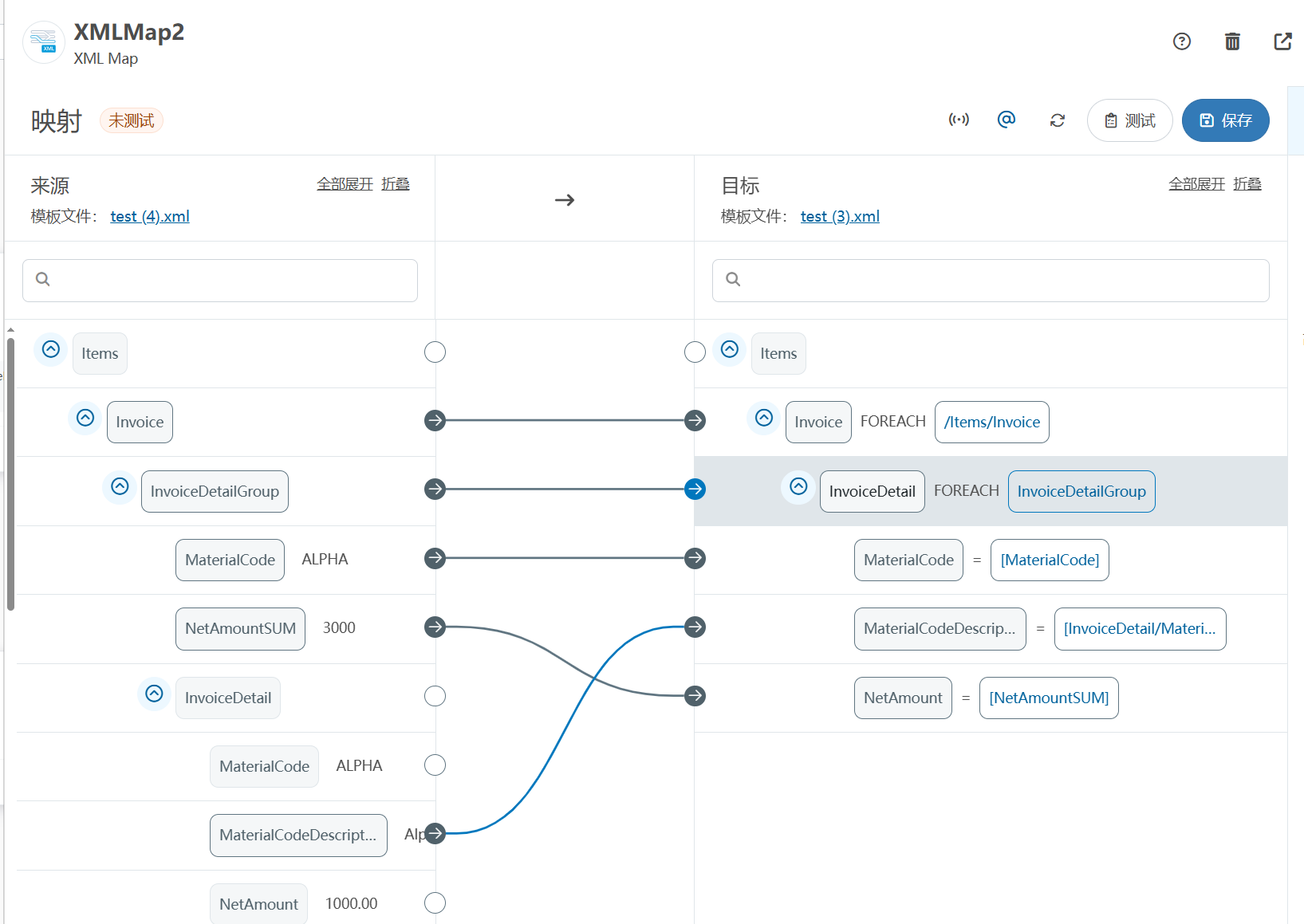

XML Group端口详解

在XML数据映射过程中,经常需要对数据进行分组聚合操作。例如,当处理包含多个物料明细的XML文件时,可能需要将相同物料号的明细归为一组,或对相同物料号的数量进行求和计算。传统实现方式通常需要编写脚本代码,增加了开…

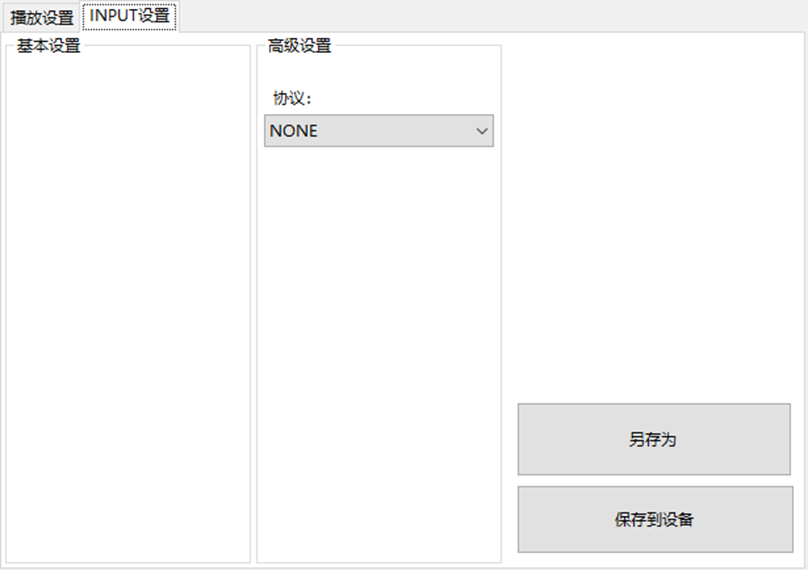

LBE-LEX系列工业语音播放器|预警播报器|喇叭蜂鸣器的上位机配置操作说明

LBE-LEX系列工业语音播放器|预警播报器|喇叭蜂鸣器专为工业环境精心打造,完美适配AGV和无人叉车。同时,集成以太网与语音合成技术,为各类高级系统(如MES、调度系统、库位管理、立库等)提供高效便捷的语音交互体验。

L…

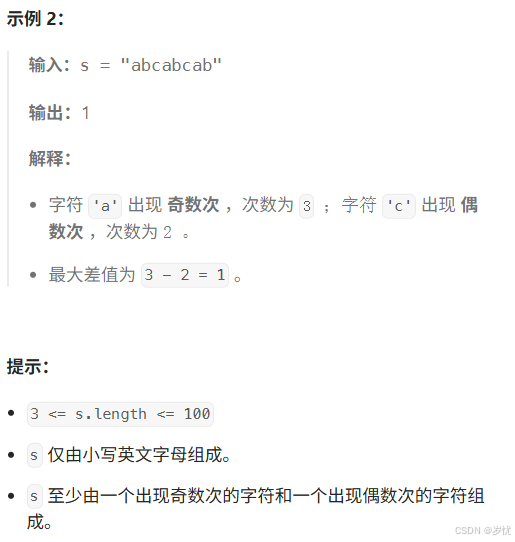

(LeetCode 每日一题) 3442. 奇偶频次间的最大差值 I (哈希、字符串)

题目:3442. 奇偶频次间的最大差值 I 思路 :哈希,时间复杂度0(n)。 用哈希表来记录每个字符串中字符的分布情况,哈希表这里用数组即可实现。

C版本:

class Solution {

public:int maxDifference(string s) {int a[26]…

【大模型RAG】拍照搜题技术架构速览:三层管道、两级检索、兜底大模型

摘要

拍照搜题系统采用“三层管道(多模态 OCR → 语义检索 → 答案渲染)、两级检索(倒排 BM25 向量 HNSW)并以大语言模型兜底”的整体框架: 多模态 OCR 层 将题目图片经过超分、去噪、倾斜校正后,分别用…

【Axure高保真原型】引导弹窗

今天和大家中分享引导弹窗的原型模板,载入页面后,会显示引导弹窗,适用于引导用户使用页面,点击完成后,会显示下一个引导弹窗,直至最后一个引导弹窗完成后进入首页。具体效果可以点击下方视频观看或打开下方…

接口测试中缓存处理策略

在接口测试中,缓存处理策略是一个关键环节,直接影响测试结果的准确性和可靠性。合理的缓存处理策略能够确保测试环境的一致性,避免因缓存数据导致的测试偏差。以下是接口测试中常见的缓存处理策略及其详细说明:

一、缓存处理的核…

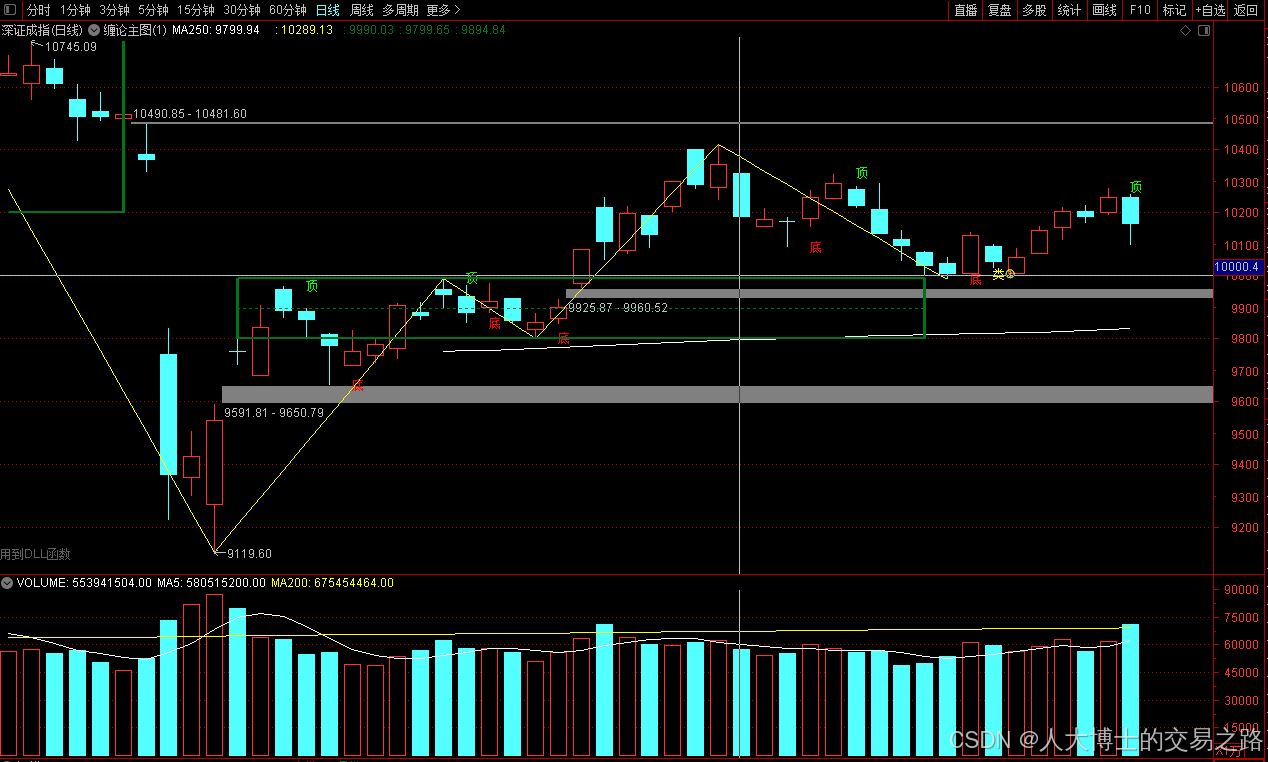

龙虎榜——20250610

上证指数放量收阴线,个股多数下跌,盘中受消息影响大幅波动。 深证指数放量收阴线形成顶分型,指数短线有调整的需求,大概需要一两天。 2025年6月10日龙虎榜行业方向分析 1. 金融科技

代表标的:御银股份、雄帝科技

驱动…

观成科技:隐蔽隧道工具Ligolo-ng加密流量分析

1.工具介绍

Ligolo-ng是一款由go编写的高效隧道工具,该工具基于TUN接口实现其功能,利用反向TCP/TLS连接建立一条隐蔽的通信信道,支持使用Let’s Encrypt自动生成证书。Ligolo-ng的通信隐蔽性体现在其支持多种连接方式,适应复杂网…

铭豹扩展坞 USB转网口 突然无法识别解决方法

当 USB 转网口扩展坞在一台笔记本上无法识别,但在其他电脑上正常工作时,问题通常出在笔记本自身或其与扩展坞的兼容性上。以下是系统化的定位思路和排查步骤,帮助你快速找到故障原因:

背景:

一个M-pard(铭豹)扩展坞的网卡突然无法识别了,扩展出来的三个USB接口正常。…

未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?

编辑:陈萍萍的公主一点人工一点智能 未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?RWM通过双自回归机制有效解决了复合误差、部分可观测性和随机动力学等关键挑战,在不依赖领域特定归纳偏见的条件下实现了卓越的预测准…

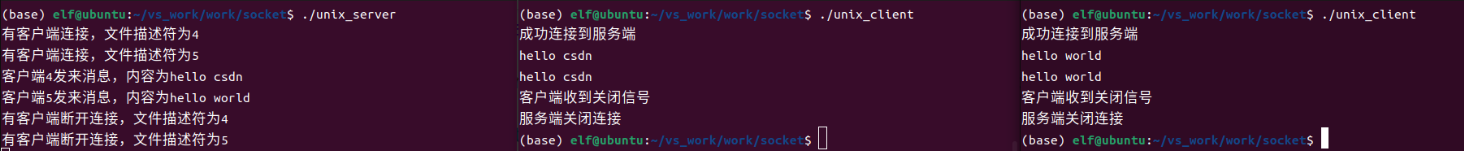

Linux应用开发之网络套接字编程(实例篇)

服务端与客户端单连接

服务端代码

#include <sys/socket.h>

#include <sys/types.h>

#include <netinet/in.h>

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <arpa/inet.h>

#include <pthread.h>

…

华为云AI开发平台ModelArts

华为云ModelArts:重塑AI开发流程的“智能引擎”与“创新加速器”!

在人工智能浪潮席卷全球的2025年,企业拥抱AI的意愿空前高涨,但技术门槛高、流程复杂、资源投入巨大的现实,却让许多创新构想止步于实验室。数据科学家…

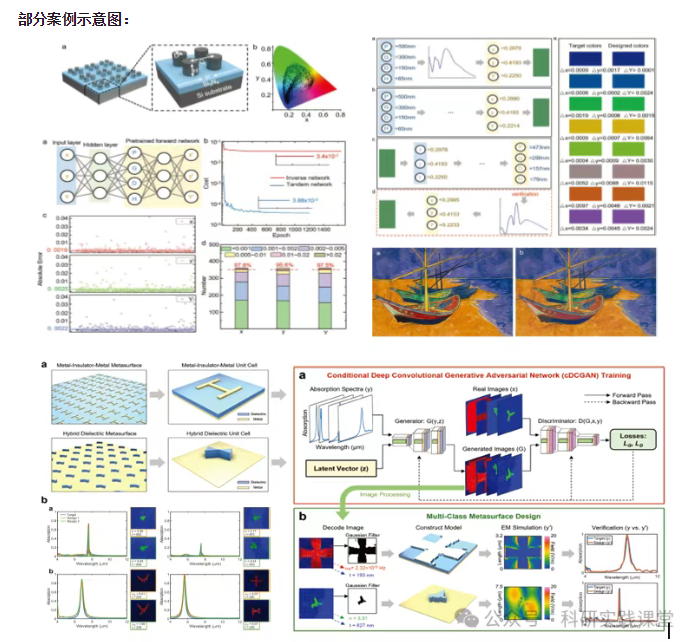

深度学习在微纳光子学中的应用

深度学习在微纳光子学中的主要应用方向

深度学习与微纳光子学的结合主要集中在以下几个方向:

逆向设计 通过神经网络快速预测微纳结构的光学响应,替代传统耗时的数值模拟方法。例如设计超表面、光子晶体等结构。

特征提取与优化 从复杂的光学数据中自…