SPI通信原理、四种工作模式与多从机工程实践

news2026/3/25 9:04:22

1. SPI通信原理与工程实践深度解析SPISerial Peripheral Interface串行外设接口是嵌入式系统中应用最广泛、性能最可靠的同步串行通信协议之一。自Motorola于20世纪80年代提出以来其简洁的硬件结构、确定性的时序特性以及高达数十MHz的通信速率使其成为连接微控制器与各类高速外设——包括ADC/DAC、Flash存储器、传感器阵列、显示驱动芯片、数字电位器及精密模拟开关——的首选接口。与I²C相比SPI不依赖开漏总线和上拉电阻无地址仲裁机制无固有速率限制与UART相比其同步特性消除了波特率容差问题全双工能力显著提升数据吞吐效率。本文将从物理层信号定义、时序模型、模式配置、多设备拓扑到典型工程问题系统性地展开SPI通信的底层原理与实践要点。1.1 四线制SPI物理接口与信号职责标准四线SPI接口由四个单向或双向信号线构成其命名与方向严格遵循主从架构视角信号名方向主机视角功能说明电气特性SCLKSerial Clock输出主机生成的同步时钟信号驱动所有数据采样与移位操作通常为方波占空比接近50%频率由主机软件或硬件分频器设定CSChip Select输出低电平有效片选信号用于使能/禁用特定从机多数器件要求CS在SCLK空闲期间稳定建立部分高速器件需满足tCSHCS高电平保持时间MOSIMaster Out, Slave In输出主机向从机发送数据的单向数据线数据在SCLK指定边沿由CPHA决定被从机采样MISOMaster In, Slave Out输入从机向主机发送数据的单向数据线数据在SCLK另一指定边沿由CPHA决定被主机采样该接口本质为主从式、全双工、同步移位寄存器链路。主机通过SCLK提供时序基准通过CS选择目标从机MOSI与MISO在每个时钟周期内各自完成一位数据的并行-串行转换。值得注意的是SPI协议本身不定义数据帧格式、起始/停止位、校验机制或应答信号这些均由具体外设的数据手册规定工程师必须严格遵循。1.2 时钟极性CPOL与时钟相位CPHA四种工作模式的本质SPI的灵活性核心在于其时钟配置参数——CPOLClock Polarity与CPHAClock Phase。二者组合形成四种标准工作模式Mode 0–3决定了SCLK空闲状态电平及数据采样/移位的时钟边沿。理解其物理意义是避免通信失败的关键。CPOL时钟极性定义SCLK在无通信活动CS为高时的静态电平。CPOL 0SCLK空闲时为低电平CPOL 1SCLK空闲时为高电平。CPHA时钟相位定义数据采样读取与数据移位写入相对于SCLK边沿的时序关系。CPHA 0数据在第一个时钟边沿采样在第二个时钟边沿移位CPHA 1数据在第一个时钟边沿移位在第二个时钟边沿采样。下表归纳了四种模式的时序特征与典型应用场景SPI ModeCPOLCPHASCLK空闲电平数据采样边沿数据移位边沿典型外设示例Mode 000低上升沿下降沿SD卡默认、多数Flash、STM32内部SPI外设默认Mode 101低下降沿上升沿MCP3008 ADC、部分EEPROMMode 210高下降沿上升沿AD779x系列ADC、部分DACMode 311高上升沿下降沿NXP LPC系列MCU常用、部分高速传感器关键工程实践要点模式选择必须与从机数据手册严格匹配。常见错误是仅关注CPOL而忽略CPHA导致数据错位一位。在CS有效拉低后SCLK的第一个有效边沿即启动数据传输。因此CS建立时间tCSH与SCLK首个边沿之间需满足从机最小建立时间要求。某些MCU如STM32的SPI硬件支持自动模式切换但多数裸机驱动需在初始化时固化配置使用RTOS或HAL库时务必确认其SPI驱动是否正确映射了目标外设所需的CPOL/CPHA。1.3 多从机系统设计常规模式与菊花链模式的权衡单一SPI主机连接多个从机是常见需求但不同拓扑对硬件资源与软件复杂度影响迥异。1.3.1 常规独立片选模式Standard Mode此模式下主机为每个从机分配独立的CS信号线MOSI、MISO、SCLK三线共用。其优势在于时序简单确定各从机通信完全隔离无数据竞争协议兼容性广适用于所有SPI从机调试直观可单独使能某从机进行通信验证。然而其核心缺陷是GPIO资源消耗呈线性增长。例如控制4个ADG1412四通道SPST开关需16个GPIO4×4远超多数MCU通用IO能力。解决方案包括GPIO复用将非关键功能引脚如未用的ADC输入、比较器输出配置为普通IO译码器扩展使用3-8线译码器如74HC138以3个GPIO控制8个CS信号专用SPI扩展芯片如MAX31855热电偶放大器内置SPI接口但需额外成本。1.3.2 菊花链模式Daisy-Chain Mode菊花链将多个从机的MISO与MOSI级联所有从机共享同一组SCLK与CS信号。数据流路径为主机MOSI → 从机1 IN → 从机1 OUT → 从机2 IN → ... → 从机N OUT → 主机MISO。其优势在于GPIO极致节省无论从机数量多少仅需4根线SCLK、CS、MOSI、MISO布线简洁减少PCB走线密度与信号完整性挑战。但其代价是通信效率与协议约束时钟周期倍增传输N位数据至第K个从机需K×N个SCLK周期。例如向链中第3个8位器件写入数据需24个时钟脉冲而非标准模式的8个器件兼容性限制并非所有SPI器件支持菊花链需明确查阅数据手册中“Daisy-Chain”或“Cascade”特性数据回读复杂化主机读取第K个从机数据时需发送K×N位填充数据以“泵出”目标数据软件需精确管理移位寄存器长度。工程决策树若从机数量≤3且GPIO充足 → 优先选用常规模式若从机数量大≥4、速率要求不高如开关控制、慢速ADC、且器件明确支持菊花链 → 采用菊花链若器件不支持菊花链但GPIO严重不足 → 评估SPI转并行桥接芯片如74HC595的BOM与PCB面积成本。1.4 SPI通信的完整时序流程与关键时序参数一次成功的SPI事务Transaction包含严格的时序阶段任何环节不满足都将导致通信失败。以Mode 0CPOL0, CPHA0为例典型流程如下CS建立期CS Setup主机将CS拉低。此时SCLK必须处于空闲态低电平且CS需在SCLK首个上升沿前稳定至少tCSH典型值10–100ns。数据传输期Data TransferSCLK第一个上升沿从机采样MOSI上的第一位数据MSB或LSB由器件定义SCLK第一个下降沿从机将第一位数据置于MISO线上后续每个SCLK周期重复采样/移位操作直至全部N位传输完毕。CS保持期CS Hold传输结束后CS需在SCLK最后一个下降沿后保持低电平至少tCSL典型值10–50ns确保从机完成内部操作。CS释放期CS ReleaseCS拉高SCLK恢复空闲态低电平。工程师必须核查的关键时序参数以ADG1412为例tCSHCS High TimeCS高电平最小持续时间确保从机退出SPI模式tCSLCS Low TimeCS低电平最小持续时间确保从机完成当前指令tSUData Setup TimeMOSI数据在SCLK采样边沿前的建立时间tHData Hold TimeMOSI数据在SCLK采样边沿后的保持时间tDISMISO Output Disable TimeCS拉高后MISO进入高阻态的最大延迟。这些参数直接决定MCU SPI外设的最高安全工作频率。例如若tSU tH 20ns则SCLK周期需 40ns对应最大频率25MHz。实践中建议初始速率设为数据手册标称最大值的50%再逐步提升并用逻辑分析仪验证眼图质量。1.5 嵌入式系统中的SPI驱动实现要点在裸机或RTOS环境下SPI驱动需兼顾效率、可移植性与健壮性。以下为关键实现策略1.5.1 硬件外设 vs 软件模拟Bit-Banging硬件SPI外设绝大多数现代MCUSTM32、ESP32、nRF52等集成专用SPI控制器支持DMA、中断、多种模式及自动CS管理。强烈推荐优先使用可释放CPU资源并保证时序精度。软件模拟当硬件SPI资源耗尽或需特殊时序如非标准CPHA时通过GPIO翻转模拟SCLK/MOSI并在精确延时后读取MISO。其缺点是CPU占用率高难以处理实时任务速率受限于MCU主频与指令周期通常≤1MHz易受中断干扰导致时序偏差。1.5.2 驱动API设计范式一个工业级SPI驱动应提供分层接口// 1. 初始化配置时钟、模式、波特率、CS引脚 spi_init(SPI_INSTANCE_1, SPI_MODE_0, 10000000); // 10MHz // 2. 事务封装自动处理CS使能/禁用保证原子性 spi_transaction_t tx { .tx_buf cmd_buffer, .rx_buf data_buffer, .len 4, .cs_pin GPIO_PIN_5 }; spi_transfer(tx); // 3. 批量传输利用DMA提升大数据量效率 spi_dma_transfer(SPI_INSTANCE_1, tx_buf, rx_buf, len);1.5.3 常见故障诊断方法故障现象可能原因诊断手段读取数据全0xFF或0x00CS未正确拉低MISO悬空或短路从机未供电用万用表测CS电平检查MISO上拉/下拉测量VCC/GND数据位移一位CPHA配置错误Mode 0/1或2/3混淆用逻辑分析仪捕获SCLK/MOSI/MISO对照模式时序图通信随机失败SCLK边沿过缓PCB走线长、容性负载大电源噪声干扰示波器观察SCLK上升/下降时间应10ns检查电源纹波多从机间数据串扰CS信号未完全隔离MISO未加缓冲器逐个断开从机定位干扰源在MISO线上加74LVC1G125缓冲器1.6 SPI在高可靠性系统中的工程考量在工业控制、医疗设备等场景SPI通信的鲁棒性至关重要信号完整性SCLK、MOSI、MISO为高速边沿信号PCB布线需遵循长度匹配Skew 1/4 SCLK周期远离高频噪声源如DC-DC开关节点使用22Ω串联端接电阻抑制振铃。ESD防护SPI接口常暴露于外部连接器应在CS、MOSI、MISO线上添加TVS二极管如SMF5.0A。看门狗协同对关键SPI外设如Flash、RTC在驱动中嵌入超时检测。若spi_transfer()在预设毫秒内未返回触发软复位或上报错误。固件升级安全通过SPI Flash存储固件时采用双Bank机制确保升级失败后仍可回滚至旧版本。2. SPI接口演进与前沿应用案例随着系统复杂度提升传统SPI正衍生出更高效的变体同时其基础原理在新型应用中持续焕发活力。2.1 高速SPI变体QSPI与XIPQuad-SPIQSPI将数据线从1位MOSI/MISO扩展至4位IO0-IO3在相同SCLK频率下实现4倍带宽。其核心创新在于双线/四线模式支持单线SDO/SDI、双线DQ0/DQ1、四线DQ0-DQ3数据传输XIPeXecute-In-PlaceMCU可直接从QSPI Flash执行代码无需加载至RAM大幅降低启动时间与内存占用。STM32H7、i.MX RT系列已将其作为标配。2.2 SPI与模拟开关的协同设计ADGS1412案例ADI的ADGS1412是一款SPI接口四通道SPST开关其设计完美体现了SPI在系统级优化中的价值。对比传统GPIO控制方案方案GPIO占用PCB面积BOM成本配置灵活性GPIO直连16个4×4大长走线低仅开关低固定逻辑SPI菊花链4个小短链路中含SPI开关高寄存器可编程ADGS1412内部集成8位配置寄存器通过SPI写入可独立控制各通道通断、设置故障保护阈值。工程师仅需一条4线SPI总线即可动态重构整个信号路由网络这在ATE自动测试设备与模块化仪器中已成为标准设计范式。3. 结语回归本质的工程实践SPI协议的简洁性恰是其强大生命力的源泉。它不试图解决所有问题而是将时序控制权交予硬件将协议解释权交予外设将系统集成的智慧交予工程师。在调试一块SPI OLED屏幕时与其纠结于“为什么Mode 3不工作”不如拿起逻辑分析仪逐帧比对SCLK边沿与MOSI数据的对应关系在规划一个16通道数据采集系统时与其盲目堆砌GPIO不如审视AD7606等SPI接口ADC如何通过菊花链将布线复杂度降至最低。真正的嵌入式功力永远沉淀在对每一个时钟沿、每一位数据、每一处时序裕量的敬畏与掌控之中。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2439069.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

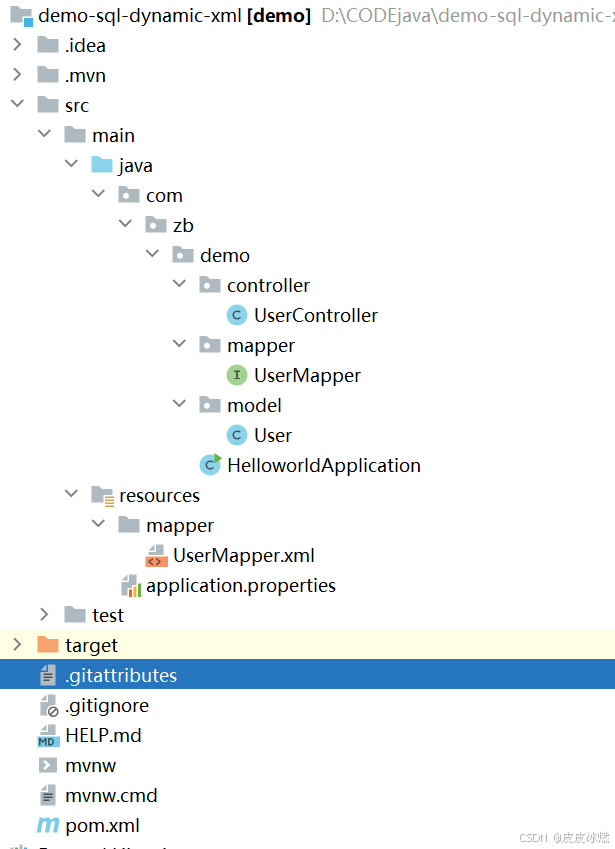

SpringBoot-17-MyBatis动态SQL标签之常用标签

文章目录 1 代码1.1 实体User.java1.2 接口UserMapper.java1.3 映射UserMapper.xml1.3.1 标签if1.3.2 标签if和where1.3.3 标签choose和when和otherwise1.4 UserController.java2 常用动态SQL标签2.1 标签set2.1.1 UserMapper.java2.1.2 UserMapper.xml2.1.3 UserController.ja…

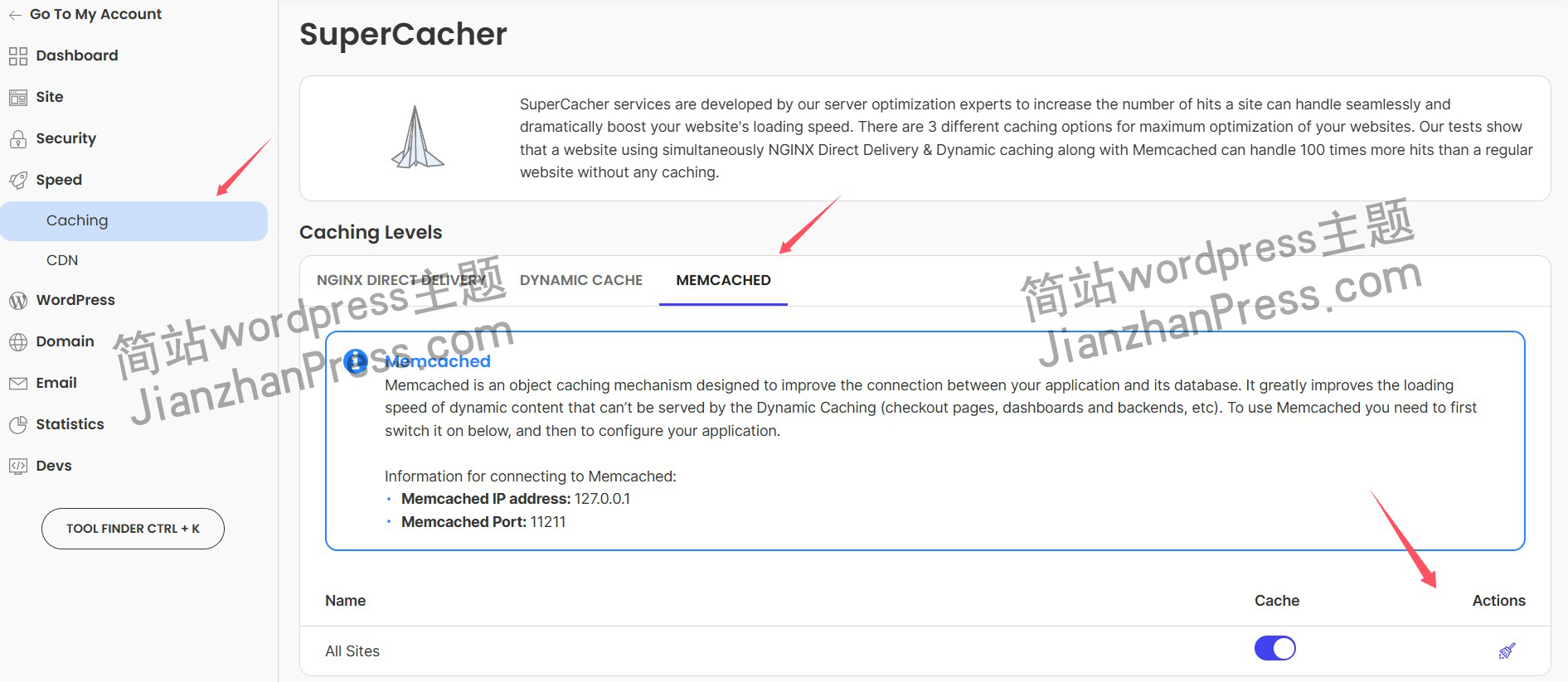

wordpress后台更新后 前端没变化的解决方法

使用siteground主机的wordpress网站,会出现更新了网站内容和修改了php模板文件、js文件、css文件、图片文件后,网站没有变化的情况。

不熟悉siteground主机的新手,遇到这个问题,就很抓狂,明明是哪都没操作错误&#x…

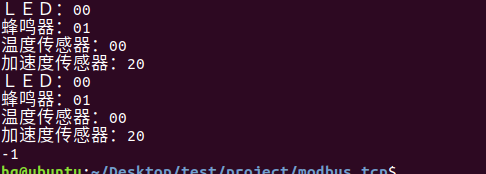

网络编程(Modbus进阶)

思维导图 Modbus RTU(先学一点理论)

概念 Modbus RTU 是工业自动化领域 最广泛应用的串行通信协议,由 Modicon 公司(现施耐德电气)于 1979 年推出。它以 高效率、强健性、易实现的特点成为工业控制系统的通信标准。 包…

UE5 学习系列(二)用户操作界面及介绍

这篇博客是 UE5 学习系列博客的第二篇,在第一篇的基础上展开这篇内容。博客参考的 B 站视频资料和第一篇的链接如下:

【Note】:如果你已经完成安装等操作,可以只执行第一篇博客中 2. 新建一个空白游戏项目 章节操作,重…

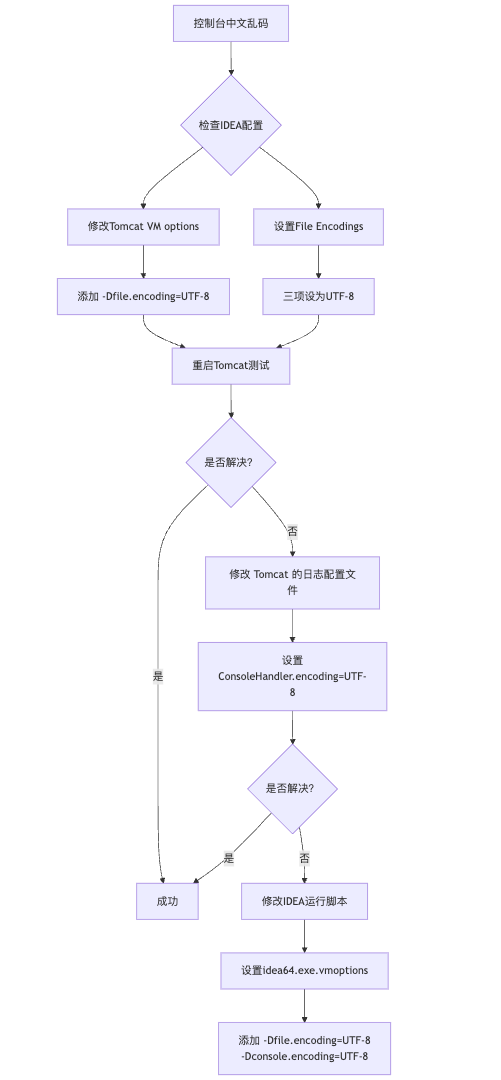

IDEA运行Tomcat出现乱码问题解决汇总

最近正值期末周,有很多同学在写期末Java web作业时,运行tomcat出现乱码问题,经过多次解决与研究,我做了如下整理:

原因:

IDEA本身编码与tomcat的编码与Windows编码不同导致,Windows 系统控制台…

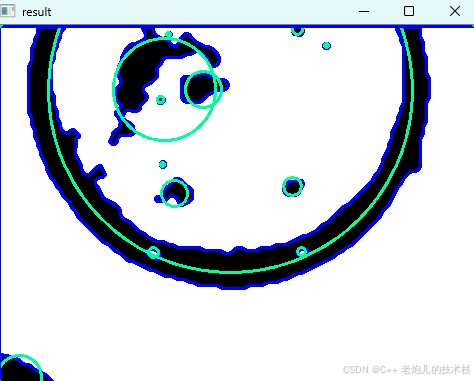

利用最小二乘法找圆心和半径

#include <iostream>

#include <vector>

#include <cmath>

#include <Eigen/Dense> // 需安装Eigen库用于矩阵运算 // 定义点结构

struct Point { double x, y; Point(double x_, double y_) : x(x_), y(y_) {}

}; // 最小二乘法求圆心和半径 …

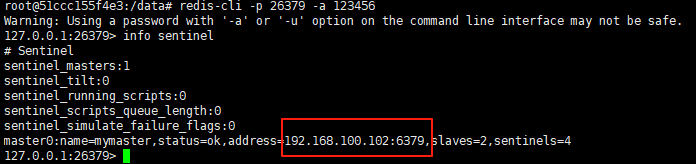

使用docker在3台服务器上搭建基于redis 6.x的一主两从三台均是哨兵模式

一、环境及版本说明

如果服务器已经安装了docker,则忽略此步骤,如果没有安装,则可以按照一下方式安装: 1. 在线安装(有互联网环境): 请看我这篇文章 传送阵>> 点我查看 2. 离线安装(内网环境):请看我这篇文章 传送阵>> 点我查看

说明:假设每台服务器已…

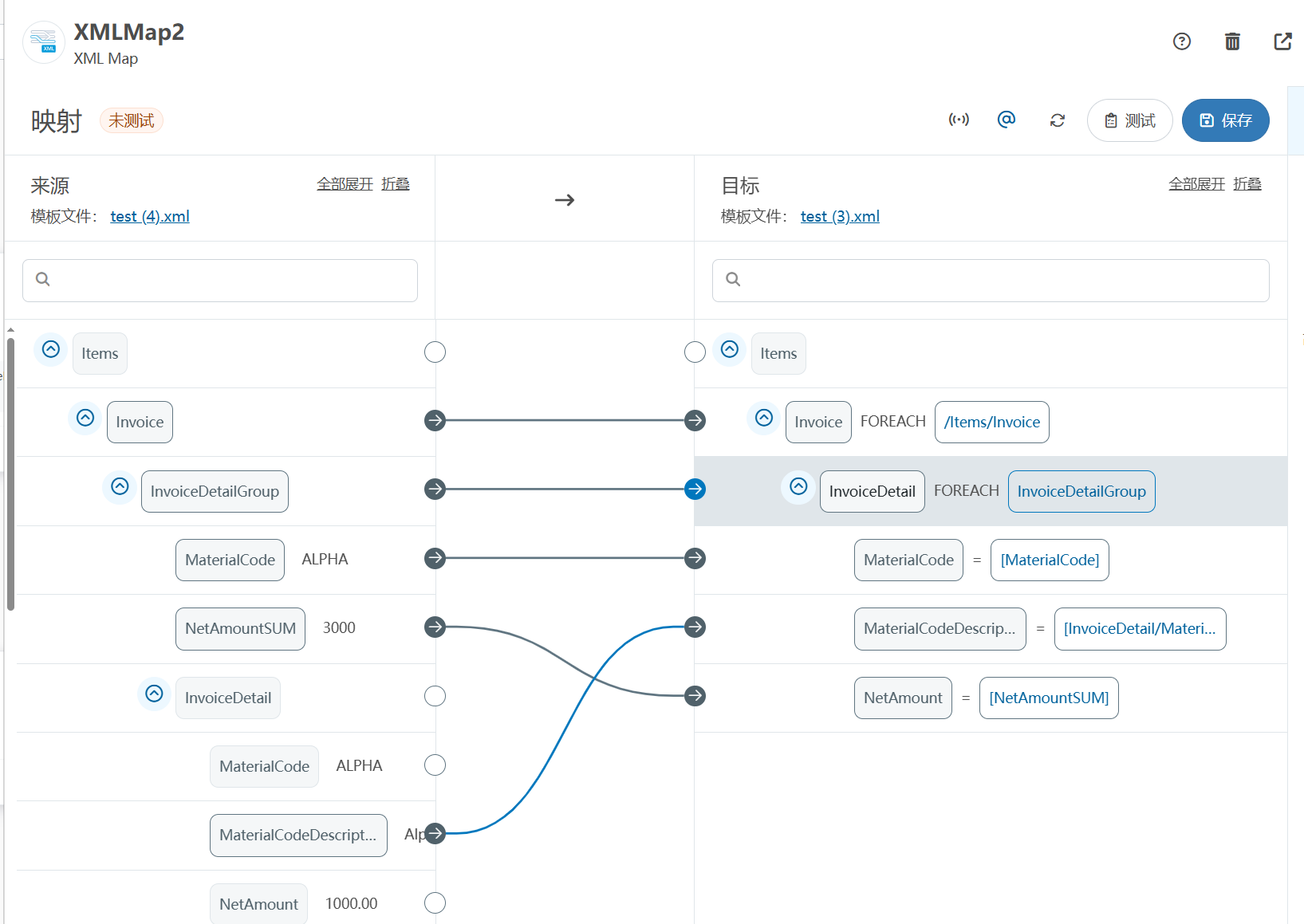

XML Group端口详解

在XML数据映射过程中,经常需要对数据进行分组聚合操作。例如,当处理包含多个物料明细的XML文件时,可能需要将相同物料号的明细归为一组,或对相同物料号的数量进行求和计算。传统实现方式通常需要编写脚本代码,增加了开…

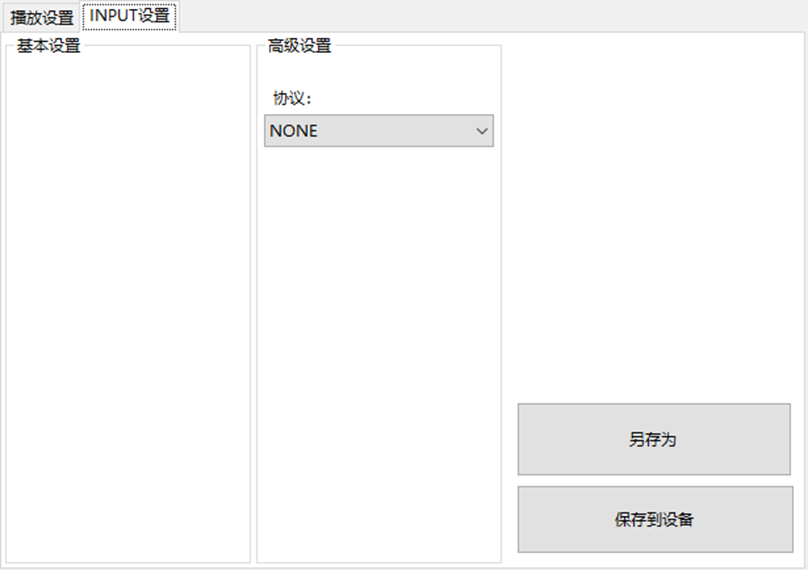

LBE-LEX系列工业语音播放器|预警播报器|喇叭蜂鸣器的上位机配置操作说明

LBE-LEX系列工业语音播放器|预警播报器|喇叭蜂鸣器专为工业环境精心打造,完美适配AGV和无人叉车。同时,集成以太网与语音合成技术,为各类高级系统(如MES、调度系统、库位管理、立库等)提供高效便捷的语音交互体验。

L…

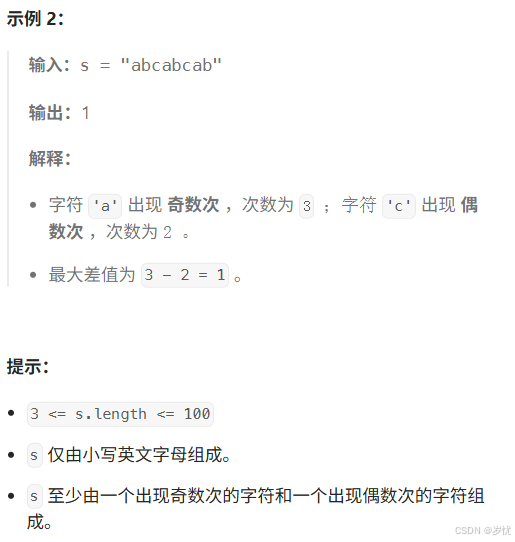

(LeetCode 每日一题) 3442. 奇偶频次间的最大差值 I (哈希、字符串)

题目:3442. 奇偶频次间的最大差值 I 思路 :哈希,时间复杂度0(n)。 用哈希表来记录每个字符串中字符的分布情况,哈希表这里用数组即可实现。

C版本:

class Solution {

public:int maxDifference(string s) {int a[26]…

【大模型RAG】拍照搜题技术架构速览:三层管道、两级检索、兜底大模型

摘要

拍照搜题系统采用“三层管道(多模态 OCR → 语义检索 → 答案渲染)、两级检索(倒排 BM25 向量 HNSW)并以大语言模型兜底”的整体框架: 多模态 OCR 层 将题目图片经过超分、去噪、倾斜校正后,分别用…

【Axure高保真原型】引导弹窗

今天和大家中分享引导弹窗的原型模板,载入页面后,会显示引导弹窗,适用于引导用户使用页面,点击完成后,会显示下一个引导弹窗,直至最后一个引导弹窗完成后进入首页。具体效果可以点击下方视频观看或打开下方…

接口测试中缓存处理策略

在接口测试中,缓存处理策略是一个关键环节,直接影响测试结果的准确性和可靠性。合理的缓存处理策略能够确保测试环境的一致性,避免因缓存数据导致的测试偏差。以下是接口测试中常见的缓存处理策略及其详细说明:

一、缓存处理的核…

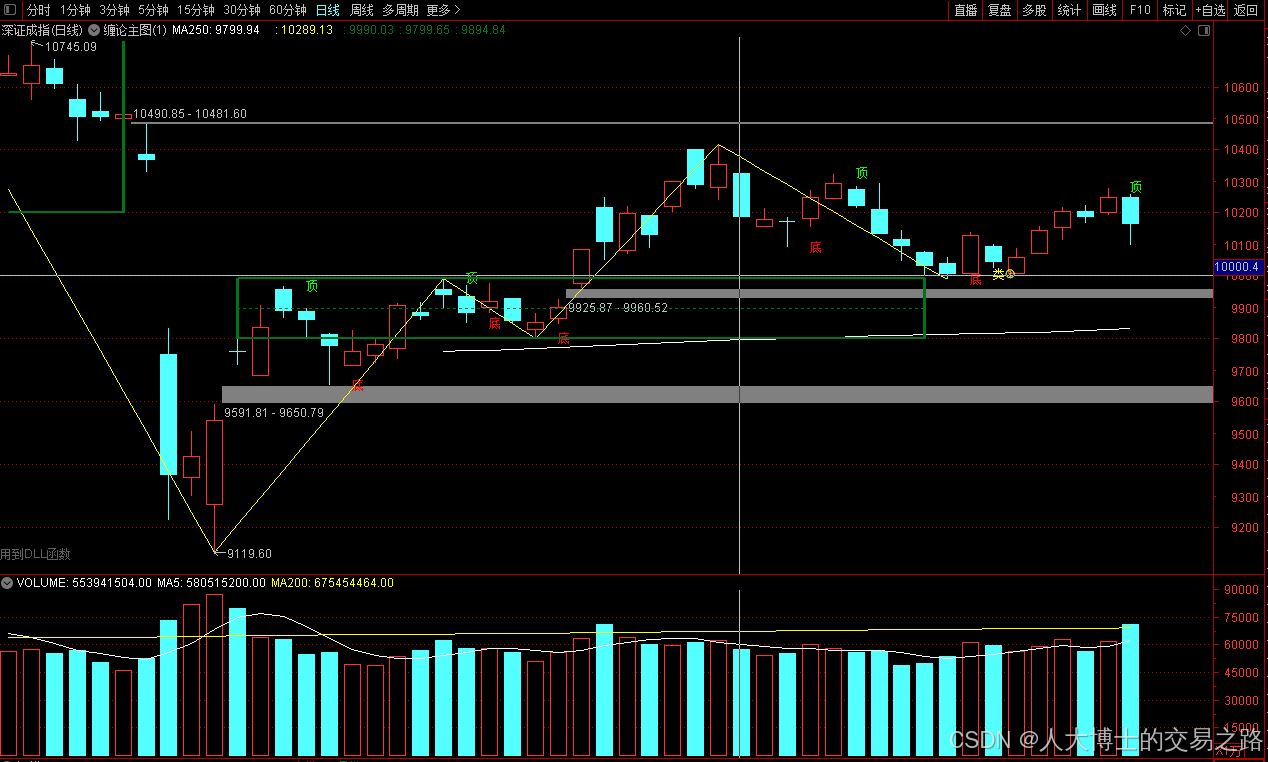

龙虎榜——20250610

上证指数放量收阴线,个股多数下跌,盘中受消息影响大幅波动。 深证指数放量收阴线形成顶分型,指数短线有调整的需求,大概需要一两天。 2025年6月10日龙虎榜行业方向分析 1. 金融科技

代表标的:御银股份、雄帝科技

驱动…

观成科技:隐蔽隧道工具Ligolo-ng加密流量分析

1.工具介绍

Ligolo-ng是一款由go编写的高效隧道工具,该工具基于TUN接口实现其功能,利用反向TCP/TLS连接建立一条隐蔽的通信信道,支持使用Let’s Encrypt自动生成证书。Ligolo-ng的通信隐蔽性体现在其支持多种连接方式,适应复杂网…

铭豹扩展坞 USB转网口 突然无法识别解决方法

当 USB 转网口扩展坞在一台笔记本上无法识别,但在其他电脑上正常工作时,问题通常出在笔记本自身或其与扩展坞的兼容性上。以下是系统化的定位思路和排查步骤,帮助你快速找到故障原因:

背景:

一个M-pard(铭豹)扩展坞的网卡突然无法识别了,扩展出来的三个USB接口正常。…

未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?

编辑:陈萍萍的公主一点人工一点智能 未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?RWM通过双自回归机制有效解决了复合误差、部分可观测性和随机动力学等关键挑战,在不依赖领域特定归纳偏见的条件下实现了卓越的预测准…

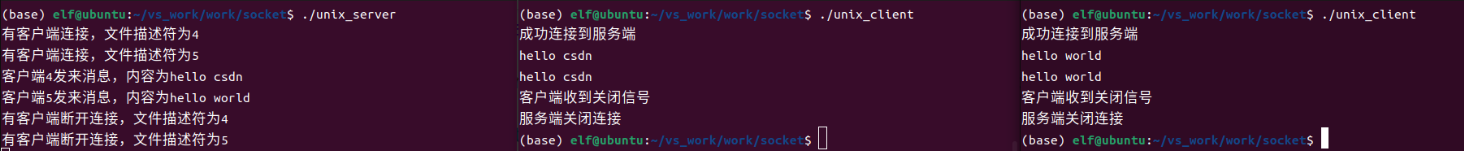

Linux应用开发之网络套接字编程(实例篇)

服务端与客户端单连接

服务端代码

#include <sys/socket.h>

#include <sys/types.h>

#include <netinet/in.h>

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <arpa/inet.h>

#include <pthread.h>

…

华为云AI开发平台ModelArts

华为云ModelArts:重塑AI开发流程的“智能引擎”与“创新加速器”!

在人工智能浪潮席卷全球的2025年,企业拥抱AI的意愿空前高涨,但技术门槛高、流程复杂、资源投入巨大的现实,却让许多创新构想止步于实验室。数据科学家…

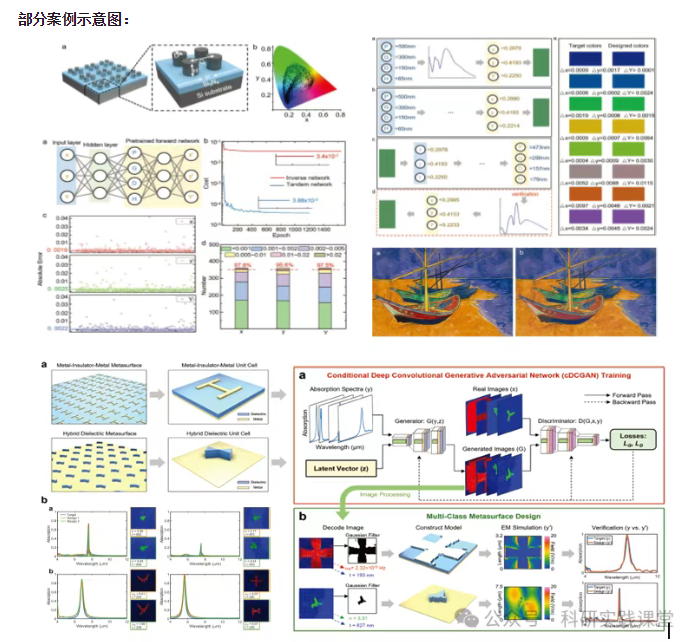

深度学习在微纳光子学中的应用

深度学习在微纳光子学中的主要应用方向

深度学习与微纳光子学的结合主要集中在以下几个方向:

逆向设计 通过神经网络快速预测微纳结构的光学响应,替代传统耗时的数值模拟方法。例如设计超表面、光子晶体等结构。

特征提取与优化 从复杂的光学数据中自…