课程体系以硬件嵌入式开发与AI芯片技术融合为核心,构建模块化知识框架。从硬件设计规范切入,系统讲解PCB Layout设计中的信号完整性控制、电磁兼容性(EMC)优化等关键要素,延伸至高速电路设计中阻抗匹配与电源完整性(PI)的工程化解决方案。嵌入式开发模块深度解析C/C++内存管理机制与Rust语言在实时系统中的安全特性,建立从裸机编程到RTOS任务调度的完整知识图谱。针对AI芯片领域,重点剖析NPU计算单元流水线、GPU并行架构及FPGA可重构逻辑资源,结合TensorRT、OpenCL等工具链实现算法硬件加速。通过工业级项目案例贯穿理论实践,覆盖自动驾驶感知系统开发、边缘计算节点部署等场景,形成从电路仿真到智能芯片落地的全流程能力矩阵。

硬件设计规范深度解析

在硬件设计领域,遵循行业规范是确保系统稳定性和可靠性的核心前提。PCB Layout设计需严格把控信号完整性约束,包括走线间距、阻抗匹配及电磁兼容(EMC)设计准则,例如高频信号路径的等长处理与电源平面分割策略。对于高速数字电路而言,时序分析需结合器件延迟参数与传输线效应,通过仿真工具验证关键信号的建立/保持时间余量。工业级设计还需关注散热布局优化,通过热阻计算确定散热片尺寸与风道规划,避免局部温升引发性能降级。此外,设计规范中明确要求遵循IPC-2221B等国际标准,从焊盘尺寸、过孔设计到器件布局均需满足可制造性(DFM)要求,确保硬件方案从原型到量产的平滑过渡。

嵌入式开发语言实战技巧

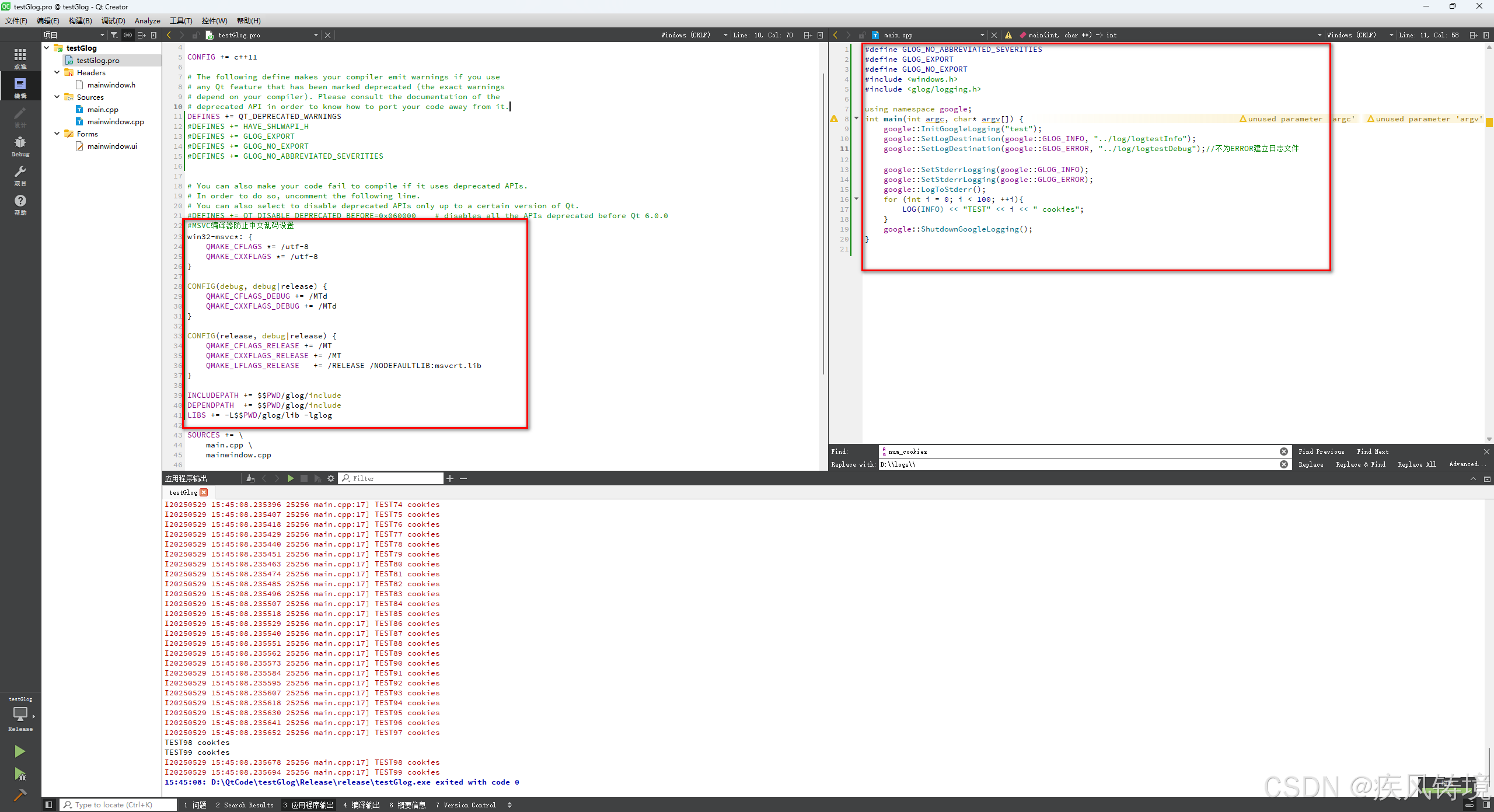

在资源受限的嵌入式系统中,C语言凭借其高效的底层控制能力与轻量级特性,仍是实时操作系统(RTOS)与硬件驱动开发的核心工具。通过指针操作和寄存器级编程,开发者能够精准优化内存占用与执行效率,例如在STM32系列MCU中实现中断向量表配置与外设寄存器映射。与此同时,C++通过面向对象特性简化复杂设备的状态管理,其模板元编程技术可显著提升代码复用率,适用于物联网网关等多协议通信场景。

随着Rust语言在嵌入式领域的崛起,其所有权模型与生命周期检查机制有效解决了内存泄漏与数据竞争问题。在ESP32-C3等RISC-V架构芯片中,Rust可通过no_std模式绕过标准库依赖,结合embedded-hal抽象层实现跨平台外设驱动开发,尤其适合对安全性要求苛刻的工业控制系统。开发者需根据项目实时性要求、硬件资源限制及团队技术栈,灵活选择语言组合方案。

AI芯片架构特性与应用

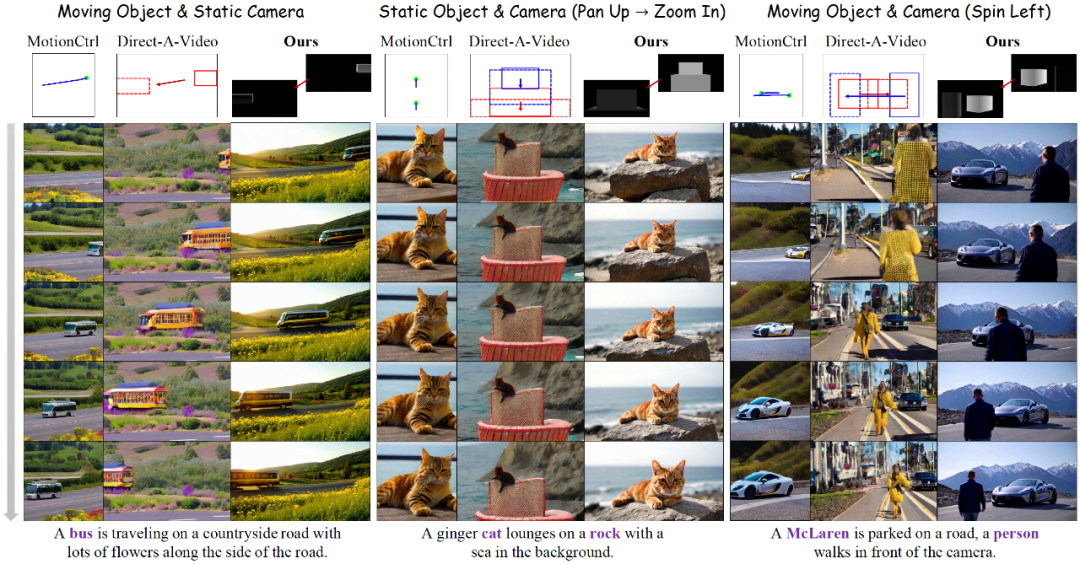

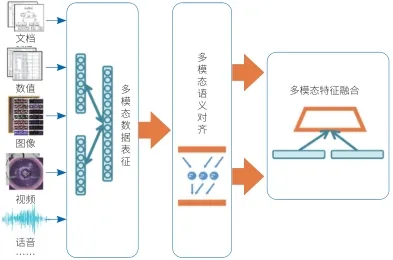

随着人工智能算法复杂度持续攀升,专用计算架构已成为突破性能瓶颈的关键路径。NPU(神经网络处理器)通过定制化张量计算单元实现百倍于传统CPU的能效比,其脉动阵列结构可高效处理卷积、矩阵运算等典型AI负载;GPU凭借大规模并行流处理器集群,在训练场景中展现出色吞吐能力,而Turing架构引入的Tensor Core更强化了混合精度计算优势;FPGA则依托可编程逻辑单元的动态重构特性,在算法快速迭代的推理场景中提供灵活部署方案。

建议开发者在架构选型时,需同步考量算法特性、功耗预算与部署周期——图像识别类任务优先选用NPU+ISP的异构方案,自动驾驶多传感器融合场景适合GPU+FPGA的混合架构,而边缘计算节点可基于FPGA实现算法动态加载。

在工业级应用层面,特斯拉FSD芯片采用双NPU设计实现毫秒级图像处理,英伟达Orin平台通过GPU集群支撑L4级决策模型,Xilinx Versal系列FPGA则在5G基站中完成AI赋能的信号优化。这些实践案例揭示出,掌握不同芯片的存储器层次结构、数据流优化机制及异构调度策略,是实现算法硬件加速的核心竞争力。

高速电路优化核心技术

在复杂电子系统中,高速电路设计直接影响信号完整性与系统稳定性。优化过程需从信号传输路径入手,采用阻抗匹配技术降低反射损耗,通过差分走线布局抑制共模噪声。针对GHz级高频信号,需运用电磁场仿真工具(如HyperLynx或ANSYS HFSS)对传输线特性阻抗进行精确建模,同时结合叠层规划优化电源地平面分布,减少串扰与电磁干扰。对于时序敏感型电路,需通过等长布线与时钟树综合技术确保同步精度,并采用端接电阻网络消除信号振铃现象。实际工程中还需考虑热效应与机械应力对高速信号的影响,通过热仿真与材料选型实现多物理场协同优化,为自动驾驶控制器、边缘计算节点等场景提供可靠硬件基础。

C与Rust系统开发实践

在嵌入式系统开发领域,C语言凭借其接近硬件的特性与高效的执行效率,长期占据核心地位。开发人员通过指针操作、内存直接管理等方式,能够精准控制传感器驱动、外设接口等底层功能模块。然而,随着物联网设备复杂度提升,C语言在内存安全性与并发处理方面的局限性逐渐显现。Rust语言通过所有权机制和编译期检查,有效解决了空指针异常、数据竞争等典型问题,其零成本抽象特性更使系统在保证安全性的同时维持高性能表现。在实际工程中,C与Rust的混合编程模式正成为趋势——使用C构建经过验证的稳定驱动层,而采用Rust编写高可靠性的业务逻辑层,两者通过FFI(外部函数接口)实现无缝交互。例如在自动驾驶域控制器开发中,Rust可用于构建传感器数据融合的安全中间件,而C语言则处理实时性要求更高的CAN总线通信协议栈,这种分层架构显著提升了系统的健壮性与可维护性。

NPU/GPU算法加速方案

在AI芯片开发领域,NPU(神经网络处理器)与GPU(图形处理器)凭借其并行计算架构成为算法加速的核心载体。NPU通过专用指令集和硬件级张量计算单元,可显著提升卷积神经网络(CNN)和Transformer模型的推理效率,其能效比可达通用处理器的10倍以上。而GPU则凭借CUDA核心集群与高内存带宽优势,在训练阶段的大规模矩阵运算中展现出色性能。开发者需结合FPGA的动态重构特性,针对目标场景进行算子定制化优化,例如通过Winograd算法减少卷积计算量,或利用混合精度量化降低内存占用。当前主流框架如TensorRT、OpenVINO已提供针对NPU/GPU的自动化部署工具链,但在工业级应用中仍需关注散热设计、内存对齐等硬件协同优化点,以确保算法在自动驾驶感知模块或边缘计算设备中的实时性与稳定性。

工业级项目案例全解析

课程通过复现自动驾驶域控制器开发、工业物联网边缘节点部署、智能安防视觉处理系统三大典型场景,构建完整的工程实践框架。在自动驾驶场景中,学员将完成12层HDI板卡的PCB叠层设计,实现多传感器信号完整性仿真,并基于Rust语言开发实时数据融合中间件,最终在FPGA异构计算平台上完成目标检测算法的硬件加速验证。工业物联网案例侧重低功耗电路设计与嵌入式系统能效优化,涵盖从电源管理模块的纹波抑制到C++线程池的资源调度策略,结合NPU芯片实现设备预测性维护模型的端侧部署。项目开发过程中同步植入代码审查、EMC测试、热仿真验证等企业级流程,使学员在解决信号串扰、内存泄漏、算子兼容性等实际问题的过程中,形成符合工业标准的工程思维。

自动驾驶领域岗位对接

随着L3级以上自动驾驶技术的商业化落地加速,行业对复合型硬件嵌入式开发人才的需求呈现指数级增长。掌握PCB Layout设计能力的技术人员可胜任车载多传感器融合系统的电路板开发,而精通C/Rust语言的开发者则能高效完成ADAS控制单元的固件编写与实时性优化。在AI芯片应用层面,熟悉NPU/GPU异构计算架构的工程师可针对目标检测、路径规划等算法设计专用加速单元,通过量化编译与硬件调度技术将算法延迟降低30%-60%。当前头部车企与Tier1供应商普遍要求开发者具备车规级硬件开发经验,同时能够完成AUTOSAR架构下的软件模块集成,这正是职坐标课程体系中工业级仿真平台训练的价值体现。从岗位分布来看,自动驾驶域控制器开发、激光雷达信号处理系统构建以及边缘计算节点部署等领域,已成为嵌入式与AI芯片技术人才的主要就业方向。

边缘计算技术部署实战

在边缘计算场景中,硬件与软件的协同优化是技术落地的核心挑战。通过低功耗PCB Layout设计与高速信号完整性分析,系统可满足工业物联网设备对紧凑布局与抗干扰能力的要求。开发层面需结合C/C++实现嵌入式实时任务调度,同时利用Rust语言的内存安全特性增强边缘节点在复杂网络环境下的稳定性。针对AI芯片的部署,课程通过NPU的并行计算单元优化图像识别模型推理效率,借助FPGA动态重构能力实现算法灵活适配。例如,在智能安防场景中,通过边缘端GPU加速的视频流分析方案,可将数据传输延迟降低60%,同时减少云端计算资源消耗。此类实战案例为学员提供了从芯片选型到分布式节点部署的全链路设计经验。

在硬件与智能芯片技术深度融合的产业背景下,系统化的知识体系与工程实践能力已成为职业竞争的关键要素。通过对PCB Layout设计规范、嵌入式多语言开发范式以及AI芯片硬件加速方案的系统性学习,开发者不仅能掌握从电路仿真到算法部署的完整技术链路,更能在自动驾驶、工业物联网等场景中实现技术方案的精准落地。课程中贯穿的工业级项目案例,既强化了高速信号完整性优化、Rust内存安全模型等核心技能的应用深度,也为应对边缘计算设备低功耗部署、NPU并行计算资源调度等复杂问题提供了可复用的工程经验。这种技术能力与产业需求的深度对齐,为从业者构建了从理论到实战的可持续发展路径。