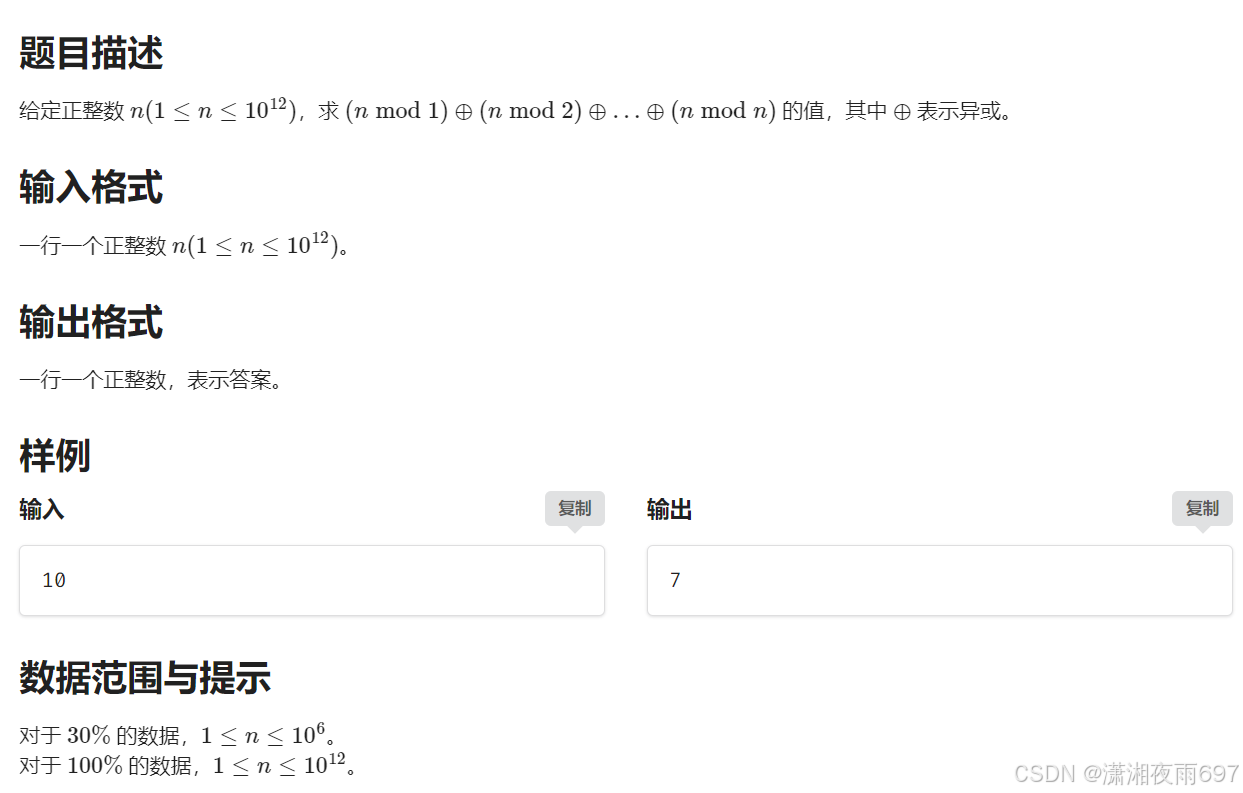

目录

参考资料

1.程序状态 - PSTATE

2.用户模式的 PSTATE 信息

2.1.状态标志

2.2.溢出/饱和标志

2.3.大于等于标志

2.4.指令集状态

2.5.IT 块状态

2.6.端序控制

2.7.指令执行时间控制

3.用户模式访问 PSTATE - APSR 寄存器

4.系统模式的 PSTATE 信息

4.1.状态标志

4.2.溢出/饱和标志

4.3.大于等于标志

4.4.PE 状态控制

4.5.异步异常(中断)标志

4.6.PE 模式

4.7.权限控制(ARMv8.1 可用)

4.8.指令执行时间控制

4.9.Speculation 控制

5.系统模式访问 PSTATE - CPSR 寄存器

参考资料

// ARMv9 架构手册:ARM Architecture Reference Manual for A-profile Architecture

// https://www.cnblogs.com/frankfankk/p/15738453.html1.程序状态 - PSTATE

ARM AArch32 架构中的程序状态 Process State(PSTATE),用于指示当前指令执行的状态

指令执行时会产生进位、溢出、运算结果为负数(对于二进制编码,使用最高位指示正负)等情况,例如,系统架构为 32-bit,即该架构中的地址寄存器、数据寄存器等为 32-bit 长度,如果两个数据寄存器进行加法运算,但计算结果大于 32-bit,则此时会产生溢出,CPU 无法直接通过这两个数据寄存器中的值得知是否产生溢出,因此,CPU 会设置程序状态 PSTATE 的溢出标志位 V(Overflow Condition flag),以表明刚才执行的指令产生了溢出情况,需要进行处理

2.用户模式的 PSTATE 信息

// 手册位置

// 手册:ARM Architecture Reference Manual for A-profile Architecture

// 章节:E1 The AArch32 Application Level Programmers’ ModelARM 在用户模式下(异常等级 EL0),提供的 PSTATE 信息如下:

2.1.状态标志

-

N:Negative Condition flag,负数标志,如果需要将指令计算结果视为二进制有符号整数,则该位为:

-

1:表示结果为负数;

-

0:表示结果为正数或者 0;

-

注意:当计算结果需要用更高的位来保存时就会产生进位,例如,计算 8 + 9 = 17,二进制表示为 1 0 0 0 + 1 0 0 1 = 1 0 0 0 1,这便是进位的一种情况;

-

-

Z:Zero Condition flag,计算结果为 0,常用于表示比较的结果为相等:

-

1:表示结果为 0;

-

0:其他;

-

-

C:Carry Condition flag,进位标志:

-

1:指令计算产生了进位,例如,无符号整数加法运算溢出也是一种进位;

-

-

V:Overflow Condition flag,溢出标志:

-

1:指令计算产生溢出,例如,有符号整数的加法运算导致溢出;

-

0:其他;

-

条件指令基于这些状态标志,结合指令中的信息确定是否执行下一条指令,或者执行哪一条指令,即基于上一条指令的执行结果,确定下一条需要执行的指令

2.2.溢出/饱和标志

-

Q:Overflow or Saturation flag,溢出/饱和标志,某些指令(通常为 DSP 相关的指令)会设置该位:

-

1:表示指令执行的结果产生溢出或饱和;

-

0:其他情况下不会发生改变;

-

2.3.大于等于标志

-

GE[3:0]:Greater than or equal flags,大于等于标志,并行加法/减法指令会使用该标志位,用于指示单字节或半字节运算的结果;

2.4.指令集状态

-

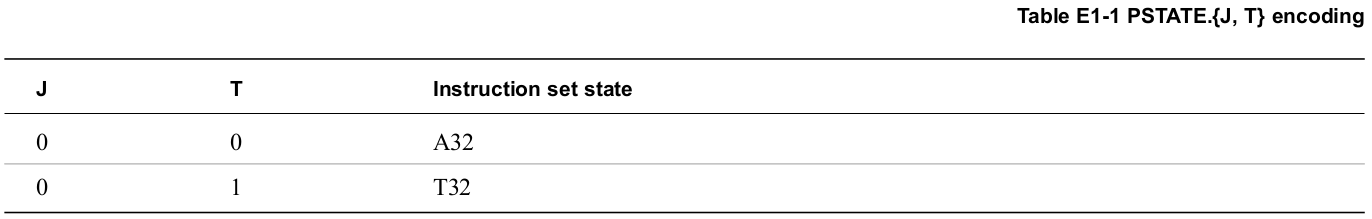

J、T:Instruction set state,指令集状态(正在执行哪个指令集),其中:

-

J 在 ARMv8 之前的架构中用于指示 CPU 是否为 Jazelle 状态(正在执行的指令集为 Jazelle,Jazelle 技术使 CPU 可以直接运行 Java 字节码);

-

T 用于指示 CPU 当前使用的是 Thumb 指令集还是 ARM 指令集;

-

J、T 两位组合使用,指示当前 CPU 所使用的指令集;

-

注意:在 ARMv8 之前的架构中,{J,Z} = {1,0} 表示指令集为 Jazelle,{J,Z} = {1,1} 表示指令集为 T32EE,从 ARMv8 架构开始,不再支持这两个指令集(指令集未实现),AArch32 中仍然需要 Trivial Jazelle 指令集扩展

2.5.IT 块状态

-

IT[7:0]:IT block state,T32 指令集中的 IT 指令使用该字段(If-Then Control,控制 IT 指令块);

2.6.端序控制

-

E:Endianness mapping,端序选择:

-

0:小端序(Little-endian);

-

1:大端序(Big-endian);

-

指令集只会使用小端序,并且忽略 PSTATE.E;

-

2.7.指令执行时间控制

-

DIT:Data Independent Timing,控制指令执行的时间,例如,计算 1 + 1 和计算 12345789 + 123456789 所耗费的时间是不一样的,但是启用该功能后,所有指令执行所花费的时间均相同(为了安全);

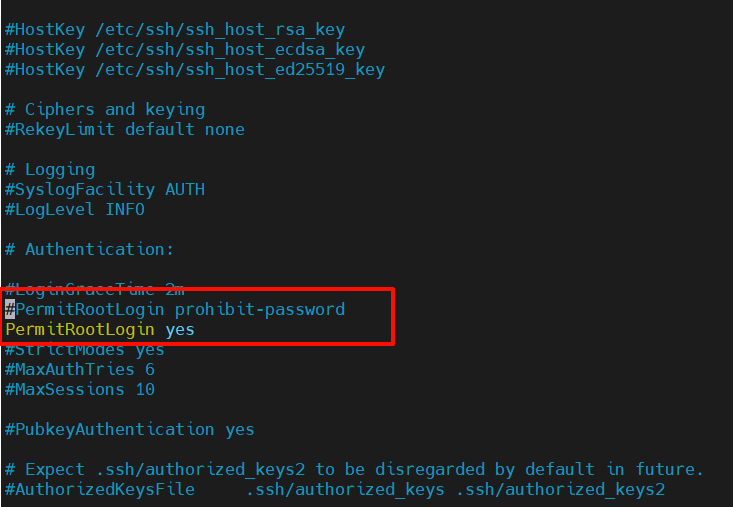

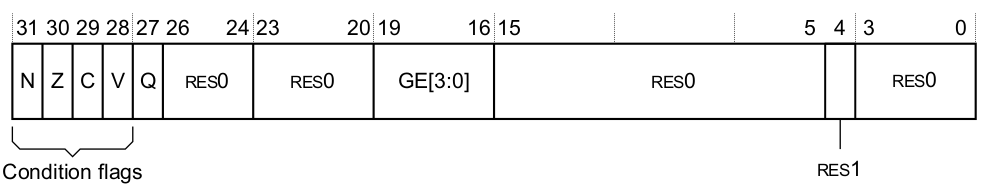

3.用户模式访问 PSTATE - APSR 寄存器

在用户模式中(EL0 权限),可以通过 APSR 寄存器(Application Program Status Register)访问 PSTATE

在 EL0 权限下,只可以访问部分 PSTATE 字段,通过 MRS 指令进行读取,通过 MSR 指令进行写入

APSR 寄存器的描述如下(可访问的 PSTATE 字段):

APSR 寄存器只提供了对 N、Z、C、V、Q、GE[3:0] 字段的访问,用户模式下,对剩余保留位执行的写入操作会被忽略,保留位虽然可以进行读取,但是读取出来的值是未知的

在更高的权限等级中(大于等于 EL1),可通过 CPSR 寄存器(Current Program Status Register)访问 PSTATE,CPSR 寄存器会提供更多的信息

4.系统模式的 PSTATE 信息

// 手册位置

// 手册:ARM Architecture Reference Manual for A-profile Architecture

// 章节:G The AArch32 System Level Programmers’ ModelAArch32 架构中,系统模式下的 PSTATE 信息如下所示:

4.1.状态标志

-

N:Negative Condition flag,负数标志;

-

Z:Zero Condition flag,计算结果为 0;

-

C:Carry Condition flag,进位标志;

-

V:Overflow Condition flag,溢出标志;

状态标志的含义和用户模式中的一致

4.2.溢出/饱和标志

-

Q:Overflow or Saturation flag,溢出/饱和标志;

该标志的含义和用户模式中的一致

4.3.大于等于标志

-

GE[3:0]:Greater than or equal flags,大于等于标志;

该标志的含义和用户模式中的一致

4.4.PE 状态控制

-

J、T:Instruction set state,指令集状态,该标志位的含义和用户模式中的一致:

-

AArch32 架构 PL1 权限下,处理异常时,通过系统控制寄存器(System Control Register,SCTLR)的 TE(T32 Exception Enable)位设置 T 标志位,表示当前执行的指令集为 T32({J、T} = {0,1});

-

AArch32 架构 PL2 权限下,通过 Hypervisor 系统控制寄存器(Hyp System Control Register,HCTLR)的 TE (T32 Exception Enable)位设置 T 标志位,表示当前执行的指令集为 T32({J、T} = {0,1});

-

-

IT[7:0]:IT block state,IT 块的状态,该标志位的含义和用户模式中的一致;

-

E:Endianness of data accesses,端序控制,该标志位的含义和用户模式中的一致,如果平台同时支持大端序和小端序,则:

-

AArch32 架构下执行 Warm Reset 时,该位的值依赖具体的平台实现:

-

如果平台异常权限的最高等级不为 EL2,则将该位设置为 SCTLR.EE 中的值;

-

如果平台异常权限的最高等级为 EL2,则将该位设置为 HSCTLR.EE 中的值;

-

-

处理异常时:

-

AArch32 架构 PL1 权限下,将该位设置为 SCTLR.EE 中的值;

-

AArch32 架构 PL2 权限下,将该位设置为 HSCTLR.EE 中的值;

-

-

-

IL:Illegal Execution state,非法执行状态;

4.5.异步异常(中断)标志

-

A:SError interrupt mask bit,SError 中断标记;

-

1:产生了该类型的异常;

-

0:未产生该类型的异常;

-

-

I:IRQ interrupt mask bit,IRQ 中断标记;

-

1:产生了该类型的异常;

-

0:未产生该类型的异常;

-

-

F:FIQ interrupt mask bit,FIQ 中断标记;

-

1:产生了该类型的异常;

-

0:未产生该类型的异常;

-

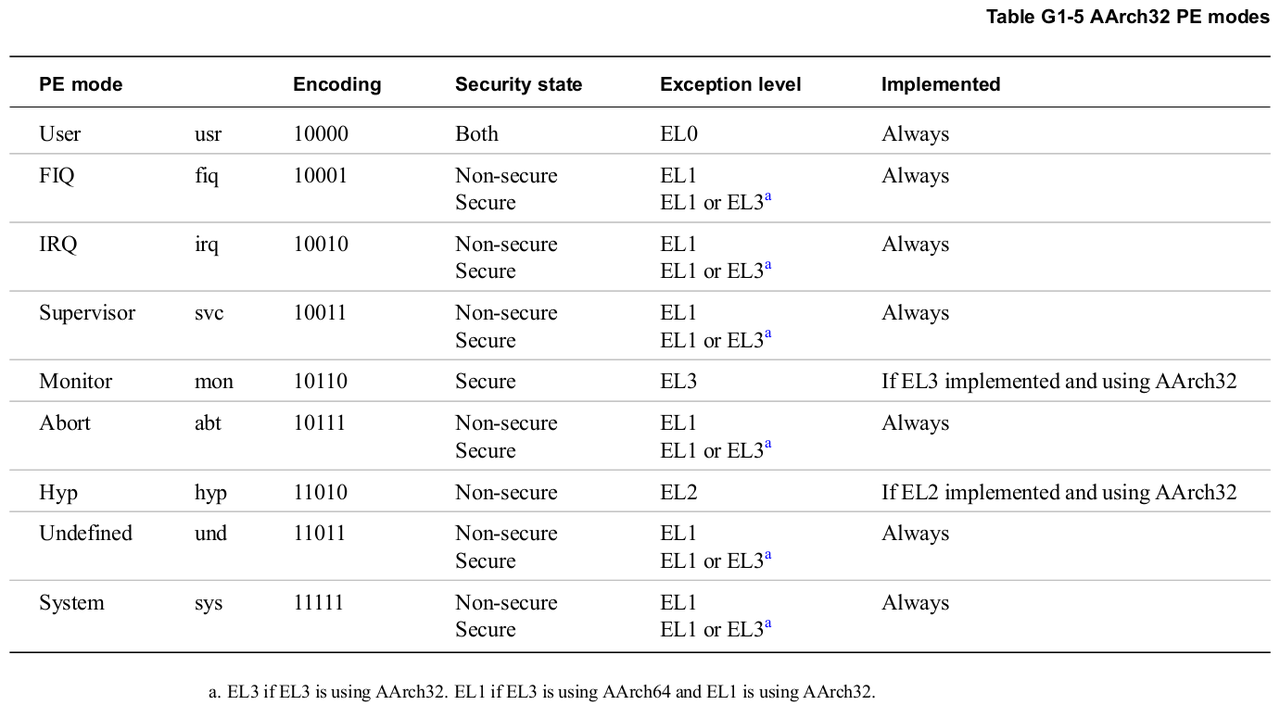

4.6.PE 模式

-

M[4:0]:Current mode of PE,当前 PE 的模式(User、IRQ、Hyp 等),支持的模式如下:

其中的编码 Encoding 即为 M[4:0] 字段的可能值

其中 M[4] 用于指示当前处理器的状态:

-

M[4] 为 0:处理器为 AArch64 状态;

-

M[4] 为 1:处理器为 AArch32 状态;

AArch32 架构中执行 Warm Reset 时,M[4:0] 的值设置如下:

-

如果系统最高权限等级不为 EL2,则该字段设置为 0b10011,表示 Supervisor 模式;

-

如果系统最高权限等级为 EL2,则该字段设置为 0b11010,表示 Hypervisor 模式;

AArch32 架构中处理异常时,M[4:0] 会设置为异常类型所对应的模式

4.7.权限控制(ARMv8.1 可用)

-

PAN:Privileged Access Never (PAN) state,ARMv8.1 架构中,当 PAN 位置 1 时,将受 PL1 或 EL2 权限保护的数据,拷贝至仅受 EL0 权限保护的虚拟内存中时,会产生权限受限错误,该位置 0 时,系统行为和 ARMv8.0 保持一致;

4.8.指令执行时间控制

-

DIT:Data Independent Timing (DIT) bit,该标志位的含义和用户模式中的一致,仅当架构实现了 FEAT_DIT 相关指令时,该位有效;

4.9.Speculation 控制

-

SSBS:Speculative Store Bypass Safe (SSBS) bit,用于防止 Speculative Store Bypass 漏洞,仅当架构实现了 FEAT_SSBS 相关指令时,该位有效;

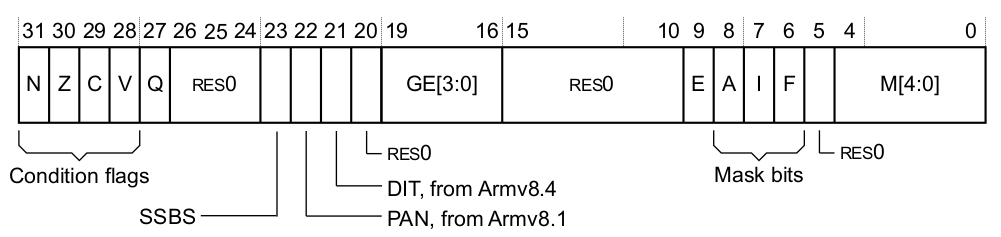

5.系统模式访问 PSTATE - CPSR 寄存器

用户模式下(EL0)仅能通过 APSR 寄存器访问一小部分 PSTATE 字段,在其他模式中(如中断 IRQ 模式)可以通过 CPSR 寄存器(Current Program Status Register)访问大部分 PSTATE 字段,同样的,通过 MRS 指令进行读取,通过 MSR 指令进行写入

CPSR 寄存器的描述如下(可访问的 PSTATE 字段):

CPSR 可以访问除 IL、IT[7:0]、J、E、T 字段的其余字段,这些字段可以通过 SPSR 寄存器(Saved Program Status Register)访问(仅在处理异常时可以访问),读写这些位需要使用对应的指令,例如,使用 SETEND BE 指令将 PSTATE.E 置 1,使用 SETEND LE 将 PSTATE.E 置 0 等等