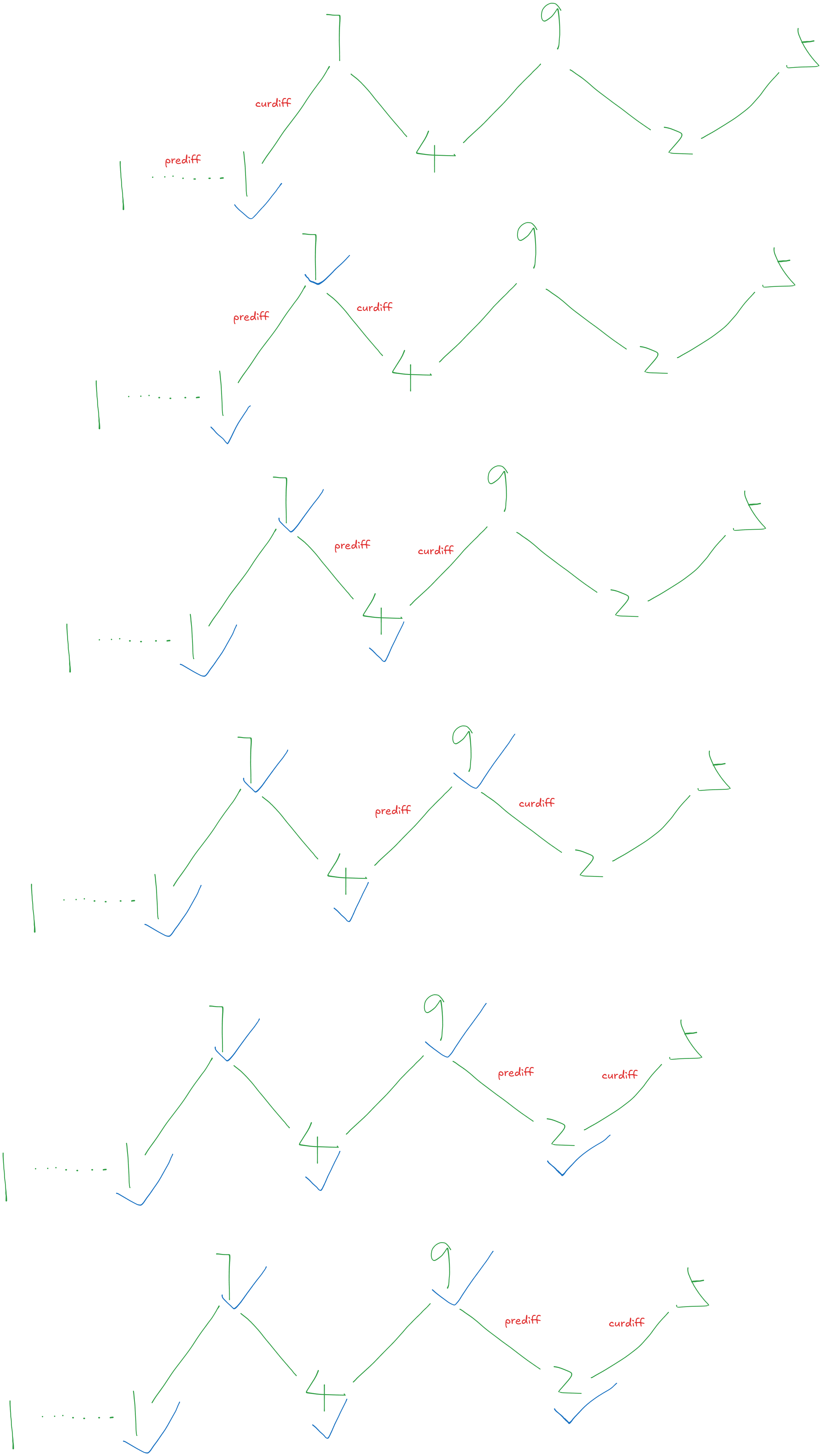

为了充分利用 GIP(通用图像处理单元)的并行处理能力,像素组的规模保持较小。每组像素数量的最小化可最大化可并行实现的独立内核数量。理想情况下,若处理单元可获取给定邻域的每个像素值,则内核可完全通用(即每个像素可赋予其独立系数)。但在此架构中,若不使用大量像素电流副本,这一设想无法实现。由于大量电流布线会导致像素尺寸和间距过大,完全通用的实现方案并不实际。因此,在设计 GIP 时必须权衡通用性与像素尺寸。因此,我们的设计允许基于 3×3 标准模型计算可变尺寸的内核,其中八个唯一系数可应用于九个像素。这些系数的分配取决于用于选择和路由的开关(或寄存器)配置。

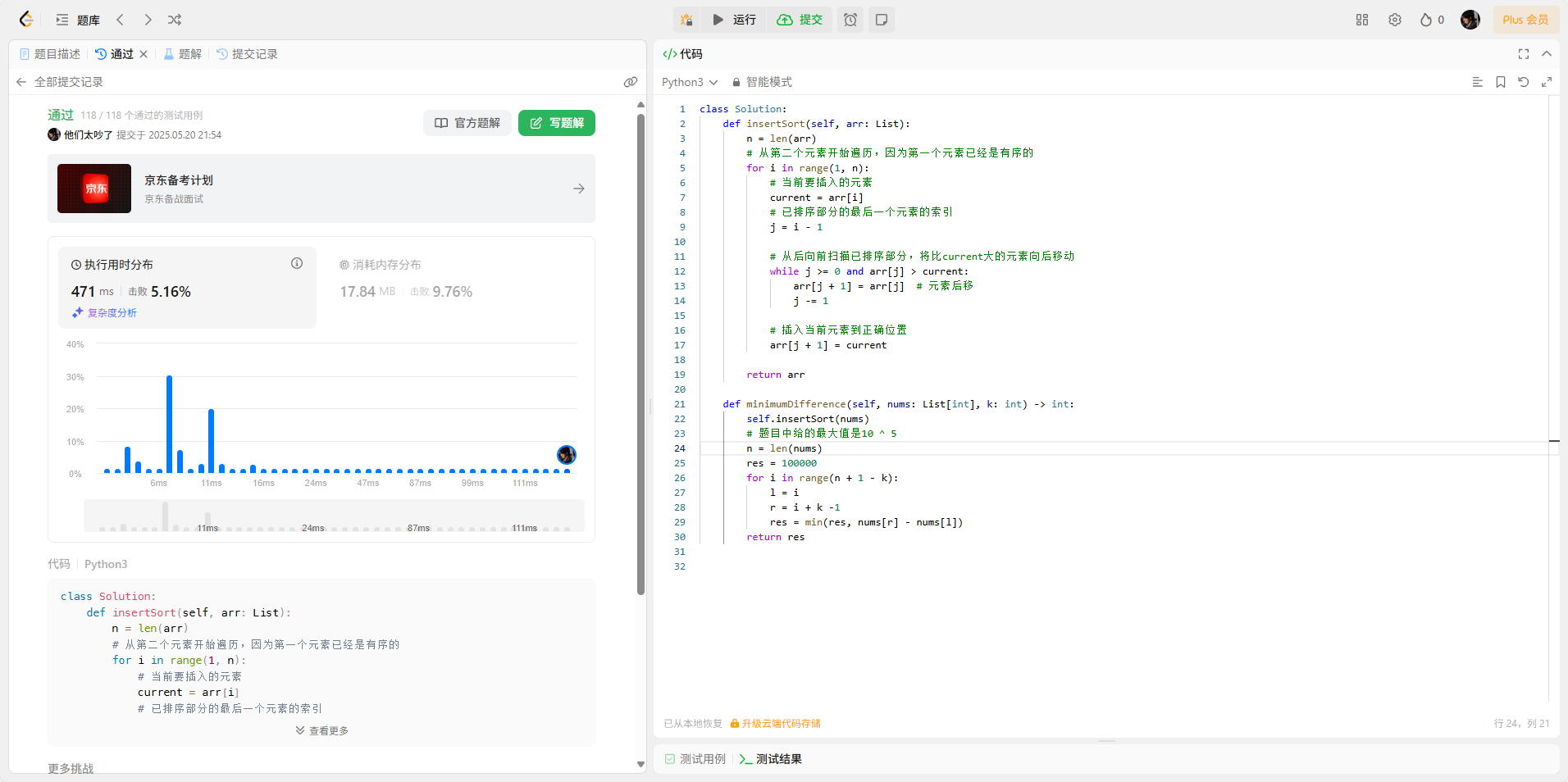

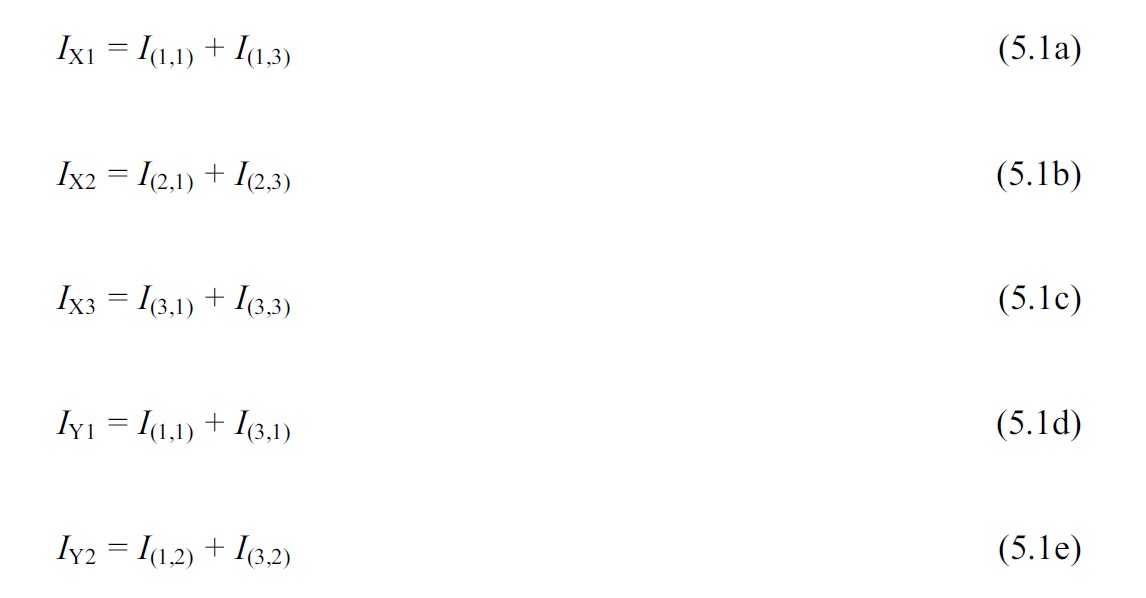

为说明这一点,可考虑一个 3×3 块,其中扫描寄存器加载了图 5-1 所示的位模式。完成此操作后,全局电流总线将传输由公式(5.1a)至(5.1h)描述的像素电流组:

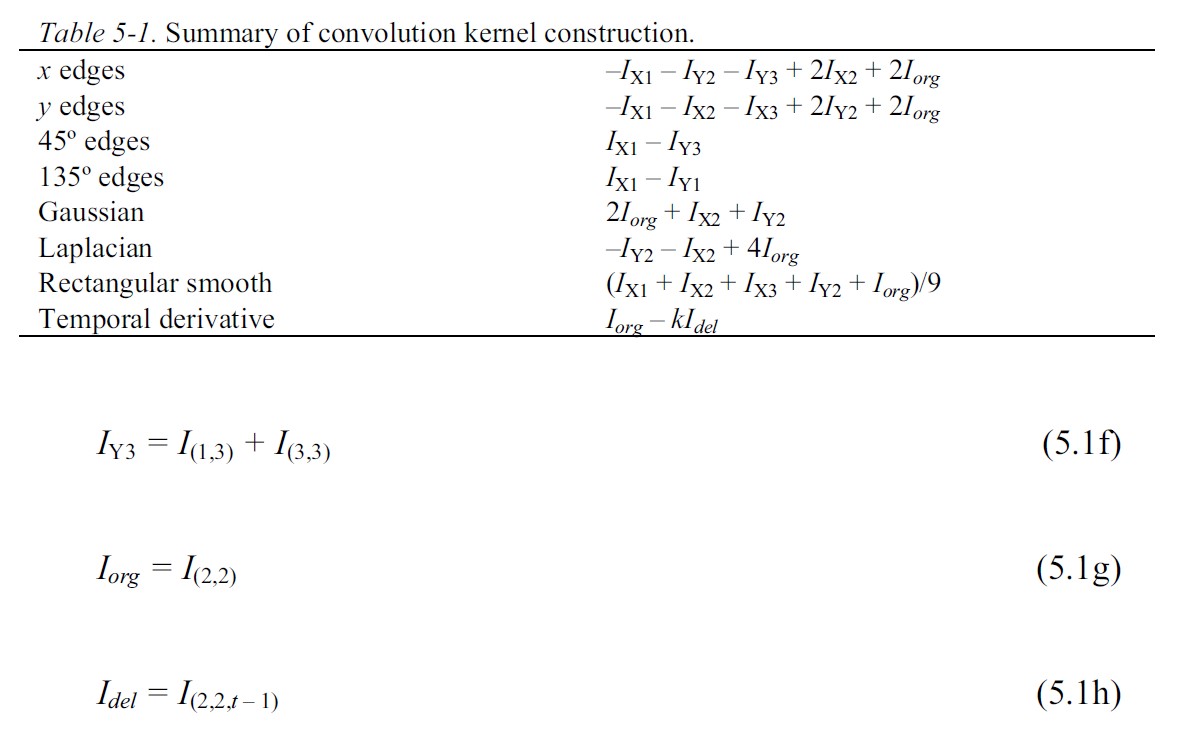

其他组合也是可能的,但所提出的分组方式将产生可并行处理的最大数量的独立内核。对于大型内核,电流 I (i,j) 可以是多个独立像素电流的总和,例如 3×3 子区域的像素电流。以这些电流为基础,可以构建各种内核。表 5-1 给出了利用公式 (5.1) 中提出的像素分组实现的卷积内核的一些示例。

具有 M×N 内核的一般卷积由公式 (5.2) 给出。四个这样的卷积(具有不同的系数)可以并行执行。

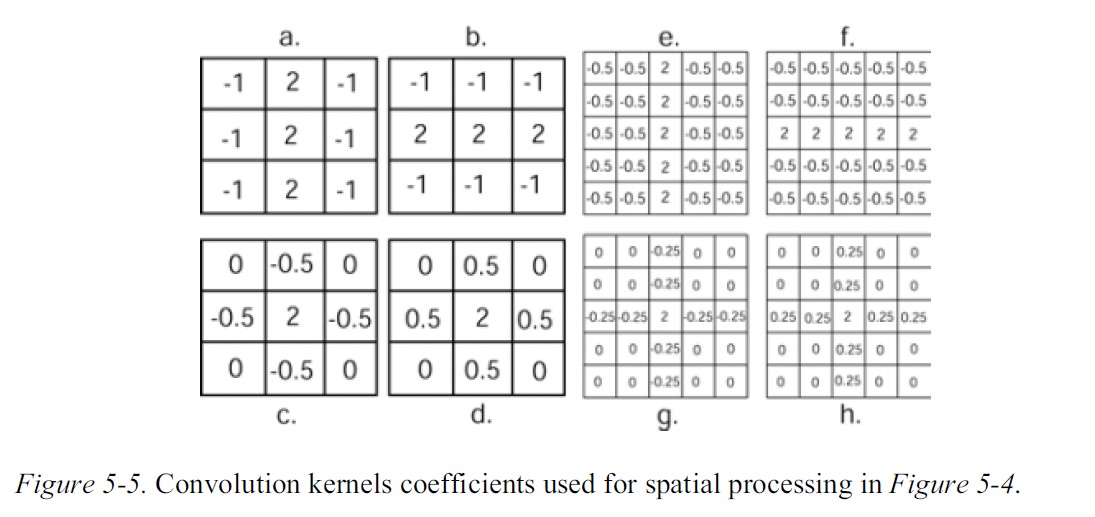

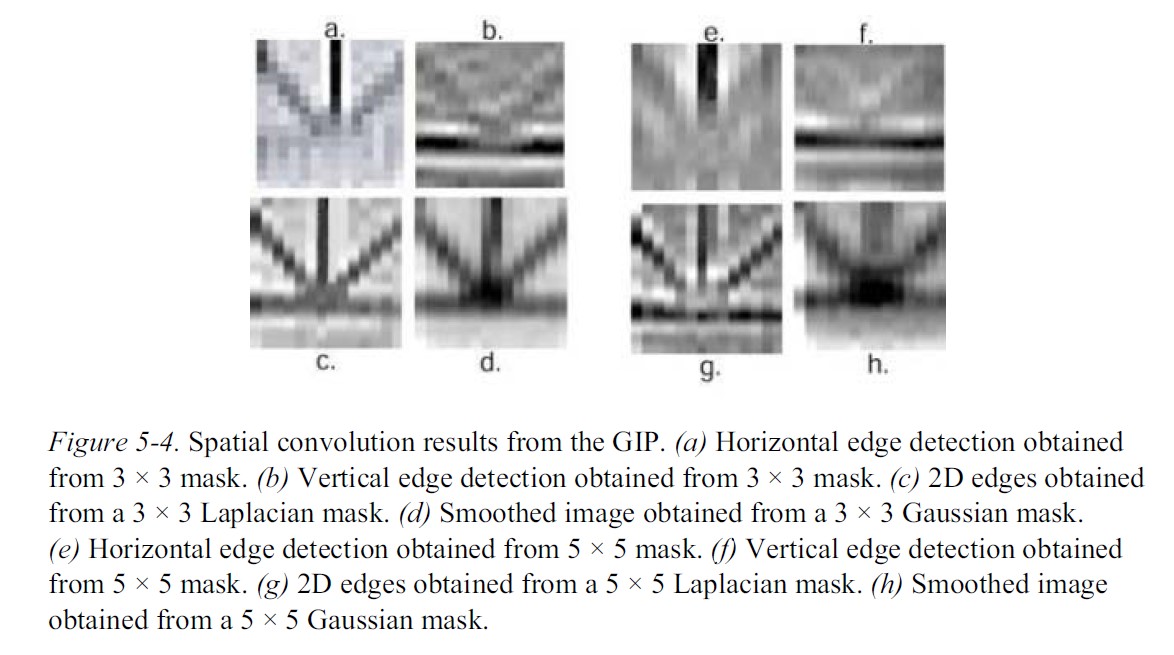

GIP 使用本章后文将讨论的编程位模式进行了测试。图 5-4 展示了入射图像与图 5-5 中的卷积核进行卷积时,芯片的输出示例。图像(a)至(d)使用 3×3 卷积核计算,而图像(e)至(h)使用 5×5 卷积核计算。5×5 核与 3×3 核结构相同,区别在于用 2×2 子区域替换了核中心轴以外的像素(见图 5-5)。构建更大尺寸的核时采用了类似技术。

图 5-4 的第一行图像分别展示了两种核尺寸计算得到的垂直和水平边缘检测结果,第二行图像则分别展示了拉普拉斯和高斯处理后的图像。正如预期,图像(a)和(f)中的垂直黑线在水平边缘检测图像(b)和(g)中不可见。拉普拉斯图像中同时显示了水平和垂直边缘,而高斯图像则提供了平滑后的图像版本。

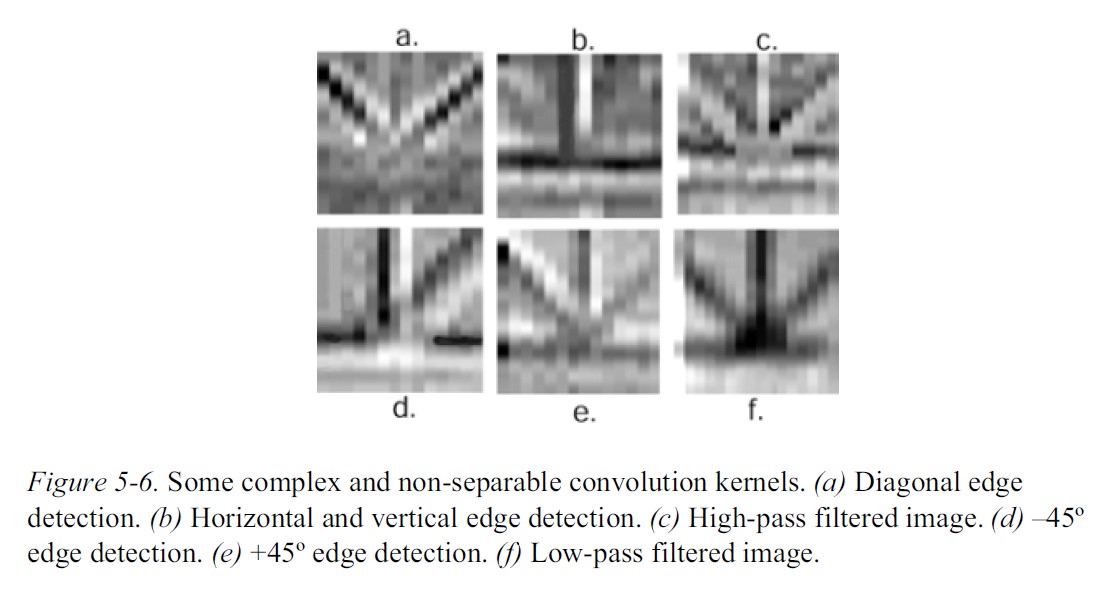

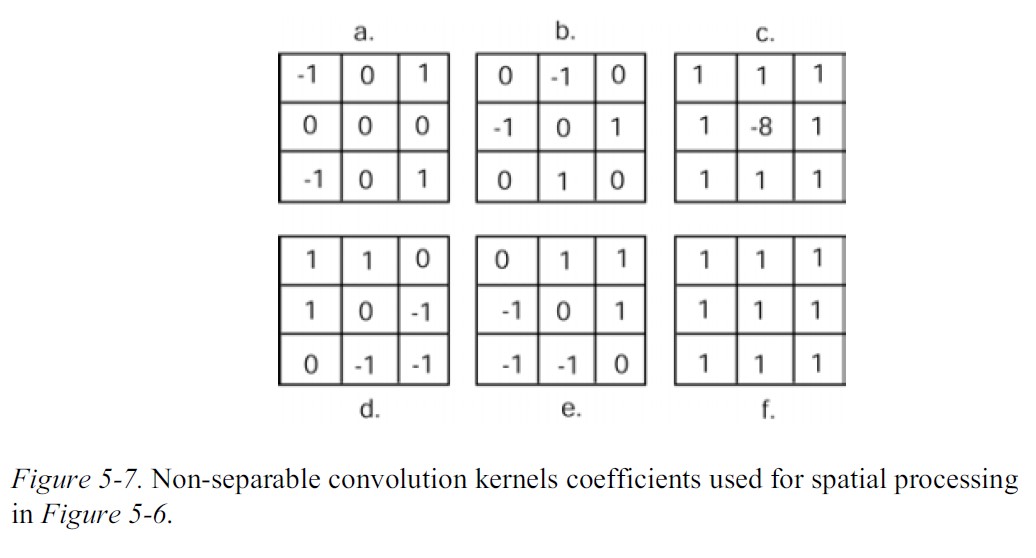

图 5-6 展示了通过各种复杂、非可分离或旋转滤波器滤波后的更多图像示例,对应的滤波器核如图 5-7 所示。图像(a)是与仅计算图像对角线边缘的空间掩码卷积的结果,而图像(b)的核在突出水平和垂直边缘组合的同时抑制了对角线边缘。图像(d)和(e)分别展示了 - 45° 和 + 45° 边缘检测结果,图像(f)为图像的低通滤波版本。此外,图像(a)和(c)的核计算强度的二阶导数(定向拉普拉斯算子),而图像(b)、(d)和(e)为一阶导数(定向梯度算子)。因此,强度梯度斜率的符号在后者图像中可见,而前者不可见。这些图中清晰显示了二维边缘检测器的方向选择性。GIP 还可实现其他复杂且非可分离的滤波器。