一、数据的表示和运算

1、进制转换

1. 常见进制类型

-

二进制(B):基数为2(0,1),计算机底层使用。

-

八进制(O):基数为8(0-7),3位二进制对应1位八进制。

-

十进制(D):基数为10(0-9),人类常用。

-

十六进制(H):基数为16(0-9, A-F),4位二进制对应1位十六进制。

2. 进制转换方法

-

二进制 ↔ 八进制/十六进制:

-

八进制:每3位二进制分一组,转换为1位八进制。

例:二进制 101 110 011 → 八进制 5 6 3 → 563O

-

十六进制:每4位二进制分一组,转换为1位十六进制。

例:二进制 1010 1111 → 十六进制 A F → AFH

-

-

十进制 ↔ 其他进制:

-

除基取余法(整数部分):如十进制转二进制,反复除以2取余数,倒序排列。

-

乘基取整法(小数部分):如十进制小数转二进制,反复乘2取整数部分,正序排列。

-

示例:

十进制 25.625 → 二进制 整数部分:25 ÷ 2 → 余数1 → 11001B 小数部分:0.625 × 2 = 1.25 → 取1,剩余0.25 0.25 × 2 = 0.5 → 取0,剩余0.5 0.5 × 2 = 1.0 → 取1 结果:11001.101B

-

2、机器数表示(原码、反码、补码、移码)

1. 原码(Sign-Magnitude)

-

定义:最高位为符号位(0正1负),其余位表示数值绝对值。

-

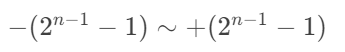

范围:nn位原码范围:

-

示例:8位原码中,+5 →

00000101,-5 →10000101。

2. 反码(Ones' Complement)

-

定义:正数与原码相同;负数符号位不变,数值位取反。

-

范围:同原码。

-

示例:-5的反码 →

11111010。

3. 补码(Two's Complement) ⭐️

-

定义:正数与原码相同;负数符号位不变,数值位取反后+1。

-

范围:nn位补码范围:

-

优势:加减法统一为加法运算,无+0和-0歧义。

-

示例:-5的补码 →

11111011。

4. 移码(Offset Binary)

-

定义:补码符号位取反,常用于浮点数阶码表示。

-

特点:方便比较大小(移码大的数实际值更大)。

-

示例:补码

11111011(-5)的移码 →01111011。

5. 转换关系表(以8位、数值-5为例)

| 表示法 | 二进制形式 | 解释 |

|---|---|---|

| 原码 | 10000101 | 符号位1,数值部分0000101 |

| 反码 | 11111010 | 原码数值位取反 |

| 补码 | 11111011 | 反码+1 |

| 移码 | 01111011 | 补码符号位取反 |

3、浮点数表示与规格化

1. 浮点数格式(IEEE 754标准) ⭐️

-

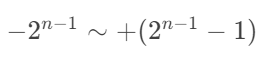

组成:

-

符号位(S):1位,0正1负。

-

阶码(E):移码表示,决定数值范围。

-

尾数(M):隐含最高位1(规格化数),表示精度。

-

-

单精度(32位):S(1) + E(8) + M(23)

-

双精度(64位):S(1) + E(11) + M(52)

2. 规格化浮点数

-

目的:通过调整阶码使尾数最高位为1(隐含存储,节省1位)。

-

步骤:

-

将数值转换为二进制科学计数法形式:

(B为偏移量,单精度127)。

(B为偏移量,单精度127)。 -

调整阶码,使尾数首位为1(隐含不存储)。

-

-

示例:

十进制数 10.25 → 二进制 1010.01 → 规格化:1.01001 × 2^3 符号位 S=0 阶码 E = 3 + 127 = 130 → 移码表示 10000010 尾数 M = 01001(隐含最高位1,实际存储后23位) 最终32位表示:0 10000010 01001000000000000000000

3. 特殊值处理

-

非规格化数:阶码全0,尾数不隐含1(用于表示接近0的数)。

-

无穷大:阶码全1,尾数全0。

-

NaN(非数):阶码全1,尾数非0。

4. 浮点数运算步骤

-

对阶(小阶向大阶对齐)。

-

尾数加减。

-

规格化处理。

-

舍入处理(可能引入精度误差)。

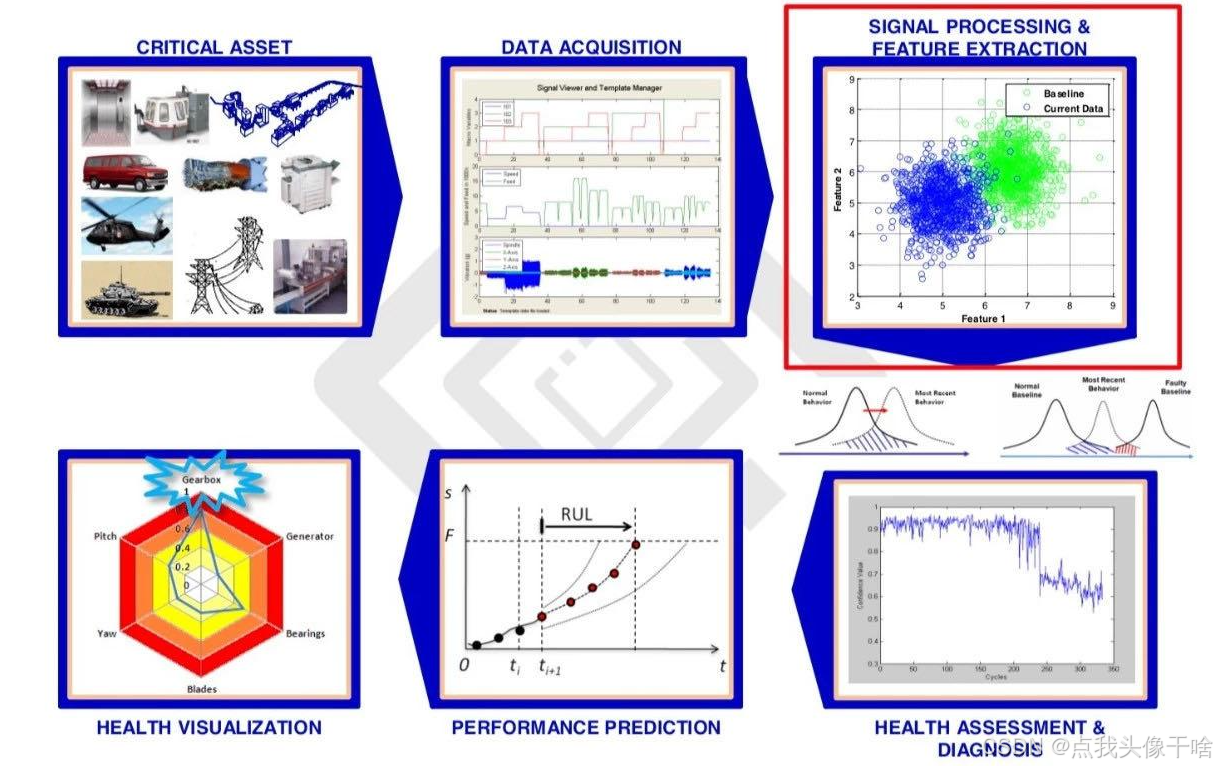

二、计算机组成与体系结构

1. 计算机体系结构分类

-

Flynn分类法(必考⭐️)

-

SISD:单指令单数据流(传统单核CPU)。

-

SIMD:单指令多数据流(GPU、向量处理器)。

-

MISD:多指令单数据流(理论模型,无实际应用)。

-

MIMD:多指令多数据流(多核CPU、分布式系统)。

-

-

真题示例:

(2022年) 多核处理器属于哪种体系结构?答案:MIMD。

2. 指令系统

1、常见寻址方式及分类

1. 立即寻址(Immediate Addressing)

-

定义:操作数直接包含在指令中(即立即数)。

-

特点:

-

速度快:无需访问内存或寄存器。

-

灵活性低:操作数为固定值,无法修改。

-

-

指令格式:

操作码 + 立即数 -

示例:

MOV AX, 1234H ; 将立即数1234H送入AX寄存器

-

应用场景:初始化寄存器或常量赋值。

2. 直接寻址(Direct Addressing)

-

定义:指令中直接给出操作数的内存地址。

-

特点:

-

需访存:需根据地址访问内存。

-

地址固定:代码重定位困难(地址硬编码)。

-

-

指令格式:

操作码 + 内存地址 -

示例:

MOV AX, [2000H] ; 将地址2000H处的数据送入AX

-

应用场景:访问全局变量或固定地址的硬件端口。

3. 间接寻址(Indirect Addressing)

-

定义:指令中给出的地址是操作数地址的地址(需两次访存)。

-

分类:

-

寄存器间接寻址:地址存储在寄存器中。

MOV AX, [BX] ; BX中存储的是操作数的地址

-

内存间接寻址:地址存储在内存中。

-

-

特点:

-

灵活:通过修改寄存器或内存中的地址,动态定位数据。

-

速度慢:需多次访存。

-

-

应用场景:指针操作、动态数据结构(如链表)。

4. 寄存器寻址(Register Addressing)

-

定义:操作数直接存储在寄存器中。

-

特点:

-

速度最快:无需访存。

-

资源有限:依赖寄存器数量。

-

-

示例:

ADD AX, BX ; AX = AX + BX(操作数均在寄存器中)

-

应用场景:高频运算操作。

5. 寄存器间接寻址(Register Indirect Addressing)

-

定义:操作数的地址存储在寄存器中。

-

特点:

-

灵活性高:通过修改寄存器内容动态寻址。

-

需一次访存:比寄存器寻址慢,但比内存间接寻址快。

-

-

示例:

MOV AX, [DI] ; DI中存储操作数的地址

-

应用场景:数组遍历、函数参数传递。

6. 相对寻址(Relative Addressing)

-

定义:操作数地址 = 当前程序计数器(PC)值 + 偏移量。

-

特点:

-

支持地址重定位:代码可动态加载到内存任意位置。

-

常用于跳转指令(如循环、条件分支)。

-

-

示例:

JMP +0AH ; 跳转到PC当前值 + 0AH的地址

-

应用场景:程序跳转、循环控制。

7. 基址寻址(Base Addressing)

-

定义:操作数地址 = 基址寄存器内容 + 偏移量。

-

特点:

-

支持动态重定位:通过修改基址寄存器,程序可加载到不同内存区域。

-

操作系统常用:管理进程地址空间。

-

-

示例:

MOV AX, [BP+10H] ; BP为基址寄存器,偏移量10H

-

应用场景:栈帧访问、内存分段管理。

8. 变址寻址(Indexed Addressing)

-

定义:操作数地址 = 变址寄存器内容 + 基址。

-

特点:

-

适合数组访问:通过变址寄存器遍历数组元素。

-

-

示例:

MOV AX, ARRAY[SI] ; SI为变址寄存器,ARRAY为基址

-

应用场景:数组、字符串处理。

9. 堆栈寻址(Stack Addressing)

-

定义:操作数通过堆栈指针(SP)隐式寻址。

-

特点:

-

后进先出(LIFO):通过PUSH/POP指令操作栈顶。

-

-

示例:

PUSH AX ; 将AX压入栈顶 POP BX ; 将栈顶数据弹出到BX

-

应用场景:函数调用、中断处理。

| 寻址方式 | 操作数来源 | 访存次数 | 典型应用 |

|---|---|---|---|

| 立即寻址 | 指令中的立即数 | 0 | 常量赋值 |

| 直接寻址 | 指令中的内存地址 | 1 | 全局变量访问 |

| 寄存器寻址 | 寄存器 | 0 | 高速运算 |

| 寄存器间接寻址 | 寄存器中存储的地址 | 1 | 指针操作 |

| 相对寻址 | PC值 + 偏移量 | 1 | 条件跳转 |

| 基址寻址 | 基址寄存器 + 偏移量 | 1 | 内存分段管理 |

| 变址寻址 | 基址 + 变址寄存器 | 1 | 数组遍历 |

3.CISC vs RISC(对比表格必背⭐️)

| 特性 | CISC | RISC |

|---|---|---|

| 指令数量 | 多(200+) | 少(约100) |

| 指令复杂度 | 复杂(硬件实现) | 简单(软件优化) |

| 寄存器使用 | 较少 | 较多 |

| 典型代表 | x86架构(Intel/AMD) | ARM架构、MIPS |

-

指令执行过程:取指 → 译码 → 执行 → 访存 → 写回。

三、存储系统

1. 存储层次结构(Cache-主存-辅存)

-

局部性原理:

-

时间局部性:最近被访问的数据可能再次被访问。

-

空间局部性:相邻存储单元可能被连续访问。

-

-

存储容量与速度关系:速度越快,容量越小(寄存器 > Cache > 内存 > 磁盘)。

2. Cache(高速缓存)

作用:缓解CPU与主存之间的速度差异(CPU访问Cache比主存快10-100倍)。

特点:

-

容量小(KB~MB级)、速度极快(访问时间1~10ns)。

-

通过硬件自动管理数据交换,对程序员透明。

-

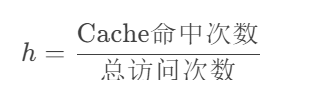

命中率与平均访问时间计算

命中率:

平均访问时间 :

-

映射方式:

映射方式 特点 应用场景 直接映射 主存块固定映射到Cache的某一特定位置 实现简单,冲突率高 全相联映射 主存块可映射到Cache的任意位置 冲突率低,实现复杂 组相联映射 Cache分组,主存块映射到组内任意位置 折中方案(如4路组相联)

3. 虚拟存储器

-

页面置换算法

算法 描述 特点 FIFO 淘汰最早进入的页面 可能产生Belady异常 LRU 淘汰最久未使用的页面 基于历史访问,实现复杂 OPT 淘汰未来最长时间不用的页面 理论最优,无法实际应用

4.主存储器(内存)

1. 内存类型

-

RAM(随机存取存储器):

-

SRAM:速度快、成本高,用于Cache。

-

DRAM:速度较慢、容量大,用于主存。

-

-

ROM(只读存储器):存储固件(如BIOS),数据断电不丢失。

2. 内存编址与容量计算

-

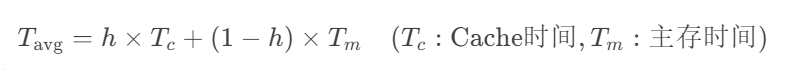

地址总线位数与寻址空间:

-

真题示例:

32位地址总线的最大寻址空间是多少?

答案:

5.存储器分类

按存储介质分类

| 类别 | 特点 | 典型代表 |

|---|---|---|

| 半导体存储器 | 基于半导体集成电路技术,速度快、体积小,部分断电后数据丢失(易失性) | RAM(SRAM 用于高速缓存,速度快、功耗低、成本高;DRAM 用于主存,需定期刷新,容量大、成本低);ROM(PROM 可编程一次;EPROM 紫外线擦除可编程;EEPROM/Flash 电擦除可编程,用于 U 盘、SSD ) |

| 磁表面存储器 | 利用磁性材料存储数据,非易失性,容量大,速度较慢 | 硬盘(HDD,通过磁头读写磁盘表面磁道 )、磁带(顺序存取,用于大规模数据备份 ) |

| 光存储器 | 利用激光读写数据,非易失性,容量大,便携性强 | CD - ROM/DVD/Blu - ray(用于软件分发、影视存储 ) |

| 新型存储器 | - | 相变存储器(PCM,结合 RAM 与非易失性特性 )、铁电存储器(FRAM,高速、低功耗、抗辐射 ) |

按存取方式分类

| 类别 | 特点 | 典型代表 |

|---|---|---|

| 随机存取存储器(RAM) | 可直接访问任意地址,存取时间与位置无关 | SRAM、DRAM(用于主存、Cache ) |

| 顺序存取存储器(SAM) | 必须按顺序访问数据,存取时间与位置相关 | 磁带 |

| 直接存取存储器(DAS) | 直接定位到数据区域后顺序读取 | 硬盘、光盘 |

按信息可保存性分类

| 类别 | 特点 | 典型代表 |

|---|---|---|

| 易失性存储器(Volatile Memory) | 断电后数据丢失 | RAM(SRAM、DRAM,用于主存、Cache ) |

| 非易失性存储器(Non - Volatile Memory) | 断电后数据保留 | ROM、Flash(用于 BIOS、SSD );HDD、光盘(用于长期数据存储 ) |

按功能与作用分类

| 类别 | 特点 | 典型代表 |

|---|---|---|

| 主存储器(内存) | CPU 直接访问,速度快,容量较小,易失性 | DRAM(如 DDR4、DDR5 ) |

| 辅助存储器(外存) | CPU 不能直接访问,需通过 I/O 接口,容量大,非易失性 | HDD、SSD、U 盘 |

| 高速缓存(Cache) | 位于 CPU 与主存之间,速度极快,容量极小(KB - MB 级) | SRAM(L1、L2、L3 Cache ) |

| 寄存器 | 位于 CPU 内部,速度最快,容量最小(存储当前指令或数据) | - |

按读写能力分类

| 类别 | 特点 | 典型代表 |

|---|---|---|

| 只读存储器(ROM) | 数据写入后不可修改,用于固件存储 | BIOS 芯片、嵌入式系统固件 |

| 读写存储器(RWM) | 支持多次读写操作 | RAM、Flash、HDD |

四、中央处理器(CPU)

1. CPU核心组件

1. 运算器(ALU, Arithmetic Logic Unit)

-

功能:执行算术运算(加减乘除)和逻辑运算(与或非)。

-

核心部件:

-

ALU:实际执行运算的电路。

-

累加器(ACC):临时存储运算结果。

-

通用寄存器:存储中间数据(如AX、BX)。

-

2. 控制器(Control Unit)

-

功能:从内存取指令、译码并控制各部件协同工作。

-

核心部件:

-

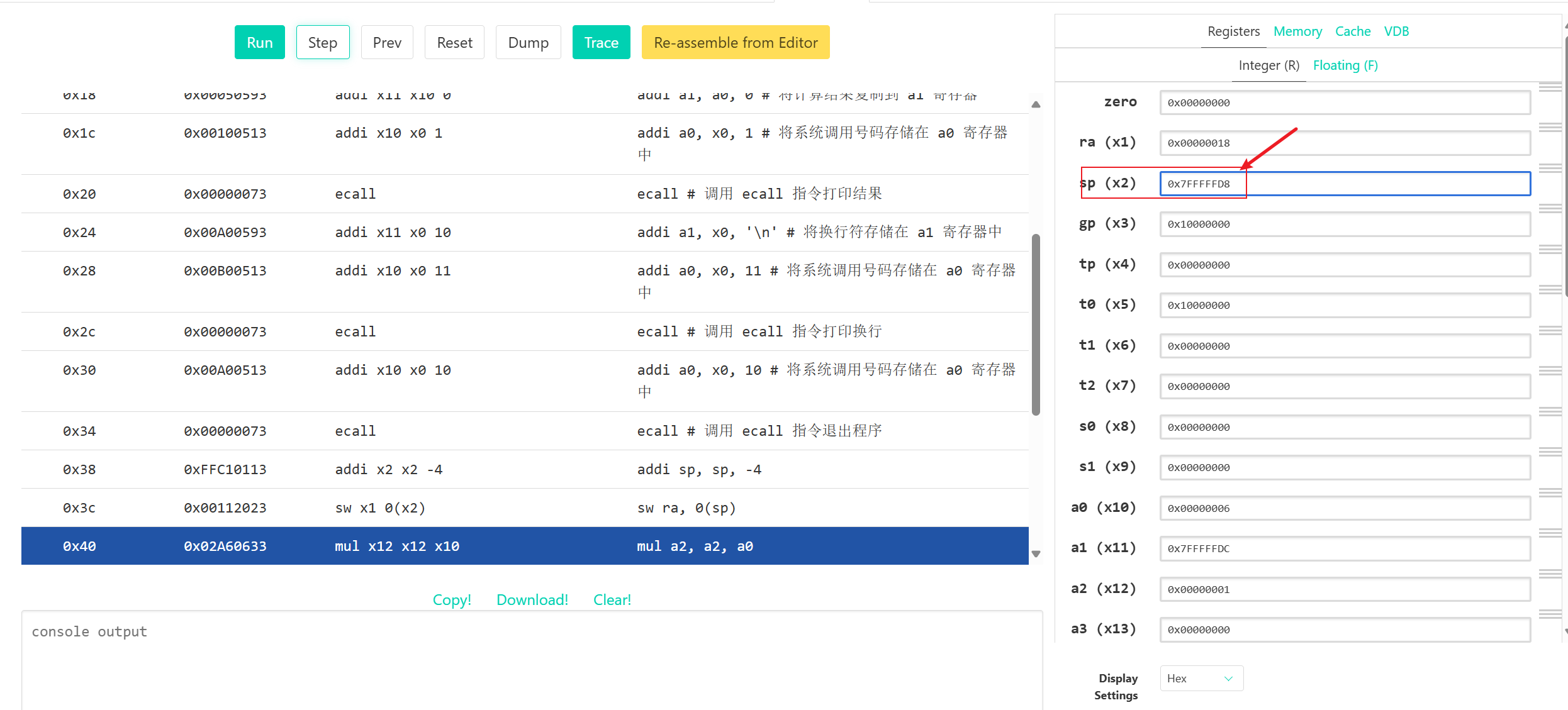

程序计数器(PC):存放下一条指令的地址。

-

指令寄存器(IR):存放当前执行的指令。

-

指令译码器(ID):解析指令操作码。

-

时序发生器:生成时钟信号,同步各部件操作。

-

3. 寄存器组

-

功能:高速存储单元,用于暂存指令、数据和地址。

-

常见寄存器:

-

数据寄存器(AX、BX、CX、DX)。

-

地址寄存器(SP堆栈指针、BP基址指针)。

-

状态寄存器(PSW):存储标志位(如进位、零标志)。

-

2. 流水线技术(必考计算题⭐️)

-

原理:将指令处理过程分解为多个阶段并行执行,提高吞吐率。

-

5级流水线:取指(IF)、译码(ID)、执行(EX)、访存(MEM)、写回(WB)。

-

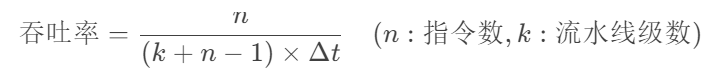

性能计算:

-

吞吐率:

-

加速比:

-

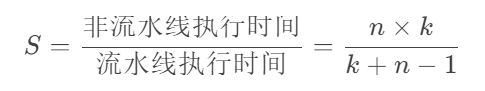

3.主频(时钟频率)

-

定义:CPU每秒的时钟周期数(单位:GHz)。

-

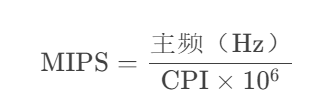

公式

4. CPI(Clock Per Instruction)

-

定义:每条指令平均消耗的时钟周期数。

-

公式:

5. MIPS(Million Instructions Per Second)

-

定义:每秒执行百万条指令数。

-

公式:

6. FLOPS(Floating-point Operations Per Second)

-

定义:每秒浮点运算次数,衡量科学计算能力。

![]()

五、总线系统

1. 总线分类

1. 按功能分类(数地控⭐️)

| 总线类型 | 功能 | 特点 |

|---|---|---|

| 数据总线 | 传输数据(双向) | 总线宽度决定一次传输的数据量(如32位总线一次传4字节)。 |

| 地址总线 | 指定内存或设备的物理地址(单向) | 总线宽度决定寻址空间(如32位总线寻址4GB)。 |

| 控制总线 | 传输控制信号(如时钟、中断、读写信号) | 协调各部件操作,确保时序正确。 |

2. 按位置分类

-

片内总线:CPU内部寄存器与ALU之间的总线。

-

系统总线:连接CPU、内存和I/O接口(如前端总线FSB)。

-

外部总线:连接计算机与外设(如USB、SATA)。

3. 按传输方式分类

-

并行总线:多位数据同时传输(如PCI、ISA),速度快但成本高。

-

串行总线:数据逐位传输(如USB、SATA),成本低、抗干扰强。

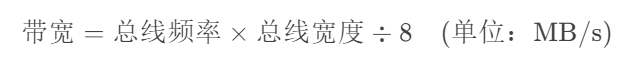

2. 总线带宽计算

-

公式:

3.常见总线标准

| 总线标准 | 类型 | 特点 | 应用场景 |

|---|---|---|---|

| PCI | 并行总线 | 支持即插即用,带宽133MB/s(32位/33MHz) | 扩展卡(显卡、网卡) |

| PCIe | 串行总线 | 点对点传输,高带宽(如PCIe 4.0 x16 ≈ 32GB/s) | 高性能显卡、SSD |

| USB | 串行总线 | 热插拔、多设备级联,USB 3.2带宽20Gbps | 外设连接(U盘、鼠标) |

| SATA | 串行总线 | 专为存储设计,SATA III带宽6Gbps | 硬盘、SSD |

| I²C | 串行总线 | 两线制(时钟+数据),低成本 | 嵌入式系统(传感器) |

六、可靠性与校验码

1. 奇偶校验码(Parity Check)

-

原理:在数据位后添加1位奇偶校验位,使整个数据中“1”的个数为奇数(奇校验)或偶数(偶校验)。

-

特点:只能检测奇数位错误,无法纠错,码距为2。

-

示例:数据

1010001,偶校验时校验位为1(总共有4个1,偶数),完整数据为10100011。

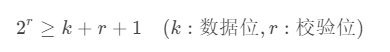

2. 海明码(Hamming Code) ⭐️(码距>=3 )

-

功能:检测并纠正1位错误,检测2位错误。

-

原理:

-

校验位分布在数据位中特定位置(2^k2k位,如1,2,4,8…)。

-

每个校验位覆盖特定数据位的奇偶性。

-

-

计算步骤:

-

确定校验位数量:

例:数据位4位 → 需3位校验位(2^3=8 >=4+3+1=8)。

-

分配校验位位置:

-

校验位位于位置 P_1(1), P_2(2), P_4(4)。

-

-

计算校验位值:

-

每个校验位覆盖其位置对应二进制中某位为1的数据位。

校验位 覆盖位(二进制标记) P_1 1,3,5,7,...(最低位为1) P_2 2,3,6,7,...(次低位为1) P_4P 4,5,6,7,...(第三位为1)

-

-

纠错:

-

接收方重新计算校验位,通过异或操作定位错误位。

-

-

3. 循环冗余校验码(CRC, Cyclic Redundancy Check) ⭐️

-

功能:检测多位错误,广泛用于网络传输(如以太网、ZIP文件)。

-

原理:

-

通过多项式除法生成校验码,附加到数据末尾。

-

关键参数:生成多项式(如CRC-16: x^{16} + x^{15} + x^2 + 1x16+x15+x2+1)。

-

-

计算步骤:

-

数据左移:数据末尾补0(补位数=生成多项式次数)。

-

模2除法:用生成多项式对补0后的数据做模2除法,余数为CRC校验码。

-

附加校验码:将余数附加到原始数据后。

-

-

示例(数据

110101,生成多项式 x^3 + x + 1x3+x+1 → 二进制1011):-

数据补3个0 →

110101000 -

模2除法求余数:

1011 ) 110101000 ^1011 ------ 1100 ^1011 ------ 1110 ^1011 ----- 1010 ^1011 ----- 010 (余数为010)CRC码为

010,完整传输数据为110101010。

-

4. 系统可靠性计算

-

串联系统:

![]()

-

并联系统:

![]()

七、输入输出(I/O)系统

1. I/O控制方式

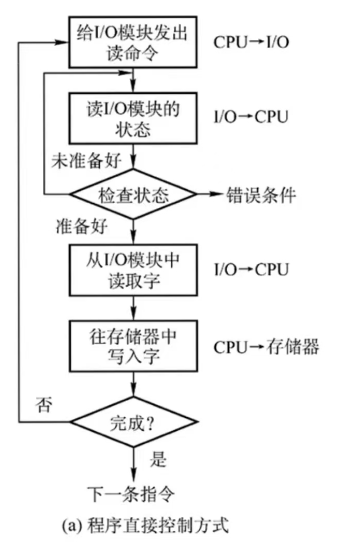

1. 程序查询方式(轮询)

-

原理:CPU通过循环检测设备状态寄存器,确认设备是否就绪。

-

特点:

-

CPU和I/0(外设)只能串行工作CPU需要一直轮询检查,长期处于忙等状态。CPU利用率低

-

一次只能读/写一个宇

-

由CPU将数放入内存。

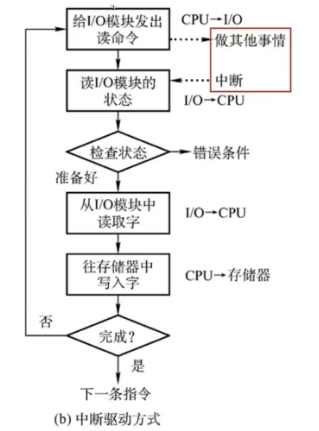

2. 中断驱动方式

-

原理:设备就绪后向CPU发送中断请求,CPU暂停当前任务处理I/O。

-

特点:

-

I/O设备通过中断信号主动报告I/O操作已完成

-

CPU和I/0(外设)可并行工作

-

CPU利用率得到提升

-

由CPU将数放入内存

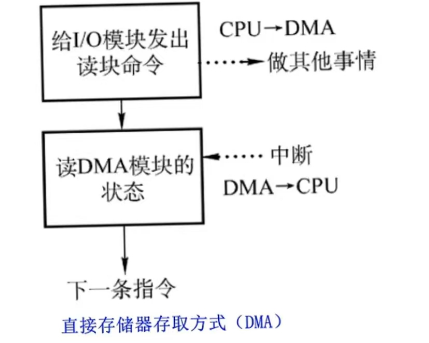

3. DMA(直接存储器访问)方式 ⭐️

-

原理:由DMA控制器直接管理数据传输,无需CPU干预。

-

特点:

-

CPU和I/O(外设)可并行工作

-

仅在传送数据块的开始和结束时需要CPU的干预

-

由外设直接将数据放入内存

-

一次读写的单位为“块”而不是字

4. 通道控制方式

-

原理:专用I/O处理器(通道)管理多个设备,进一步解放CPU。

-

特点:

-

适用于大型系统(如服务器、数据中心)。

-

通道类型:选择通道、多路通道。

-

2. 中断处理过程

1. 中断触发与请求

-

触发条件:

-

外部中断:硬件设备(如键盘、磁盘)通过中断控制器(如8259A)发送中断请求信号(IRQ)。

-

内部中断:CPU执行指令时检测到异常(如除零、缺页)。

-

软中断:程序主动调用中断指令(如

INT 0x80触发系统调用)。

-

-

中断请求信号:设备将中断请求发送到中断控制器,控制器汇总后向CPU发送INT信号。

2. 中断响应与现场保存

-

中断响应条件:

-

CPU处于中断使能状态(IF标志位为1,对可屏蔽中断有效)。

-

当前中断优先级高于正在处理的中断(若允许嵌套)。

-

-

硬件自动完成的操作:

-

关中断:CPU自动清除IF标志位(防止中断嵌套,除非支持优先级抢占)。

-

保存现场:

-

将程序计数器(PC) 和 程序状态字(PSW) 压入栈中。

-

部分架构会保存部分通用寄存器(如x86由软件手动保存)。

-

-

获取中断向量:

-

通过中断控制器或内部逻辑获取中断类型号(如IRQ0对应向量号0x08)。

-

根据中断向量号查询中断向量表(IDT),获取中断服务程序(ISR)入口地址。

-

-

3. 中断服务程序(ISR)执行

-

ISR任务:

-

保护现场:手动保存其他寄存器(如AX、BX等)到栈中(硬件未自动保存时)。

-

处理中断:

-

读取设备状态寄存器,确认中断来源(如键盘缓冲区有数据)。

-

执行设备相关操作(如读取键盘输入、处理磁盘I/O完成)。

-

清除设备中断请求(向设备发送确认信号)。

-

-

恢复现场:从栈中恢复手动保存的寄存器。

-

-

中断嵌套处理(可选)

4. 中断返回与现场恢复

-

中断返回指令

-

硬件自动完成的操作:

-

从栈中恢复PC和PSW。

-

开中断:恢复IF标志位(CPU重新允许响应中断)。

-

-

继续执行原程序:CPU从保存的PC地址继续执行被中断的任务。

| 特性 | 中断(Interrupt) | 异常(Exception) |

|---|---|---|

| 触发源 | 外部设备或程序(异步) | CPU执行指令时出错(同步) |

| 处理方式 | 可延迟响应(可屏蔽) | 必须立即处理(如缺页、除零) |

| 返回行为 | 通常返回到下一条指令 | 可能终止程序或重新执行故障指令 |

八、加密技术与认证技术

1.加密技术分类

1. 对称加密(Symmetric Encryption)(私钥加密)

-

原理:使用同一个密钥进行加密和解密。

-

特点:加密速度快,适合大数据量加密。

-

常见算法:

-

AES(Advanced Encryption Standard):128/192/256位密钥,广泛用于文件加密和网络通信(如Wi-Fi WPA2)。

-

DES(Data Encryption Standard):56位密钥,已因安全性不足被淘汰。

-

3DES:DES的增强版,三次加密,速度较慢。

-

2. 非对称加密(Asymmetric Encryption)(公钥加密)

-

原理:使用公钥加密、私钥解密(或私钥签名、公钥验证)。

-

特点:解决密钥分发问题,支持数字签名。

-

常见算法:

-

RSA:基于大素数分解,支持加密和签名,密钥长度通常2048位。

-

ECC(椭圆曲线加密):相同安全强度下密钥更短(如256位ECC ≈ 3072位RSA)。

-

2.认证技术

1. 数字摘要(Hash)

-

原理:通过哈希函数(如SHA-256)生成固定长度的唯一摘要。

-

特点:

-

不可逆性:无法从摘要还原原始数据。

-

抗碰撞性:不同数据生成相同摘要的概率极低。

-

-

常见算法:

-

SHA-256:比特币、数字证书默认算法。

-

MD5(已不推荐):128位摘要,易受碰撞攻击。

-

2. 数字签名(Digital Signature)

-

原理:

-

发送方用私钥对数据摘要加密,生成签名(不可否认性)。

-

接收方用公钥解密签名,验证摘要与数据是否一致。

-

-

作用:

-

完整性:数据未被篡改。

-

不可否认性:发送方无法否认签名行为。

-

3. 数字证书(Digital Certificate)

-

原理:由CA(证书颁发机构) 颁发的电子文件,包含公钥、持有者信息、CA签名等。

-

标准格式:X.509。

-

证书链验证:浏览器验证证书是否由受信任的CA签发(根证书 → 中间证书 → 终端证书)

3.混合加密系统

-

原理:

结合对称与非对称加密的优势:-

使用非对称加密交换对称密钥(如TLS握手阶段)。

-

使用对称加密加密实际传输数据。

-

4.加密算法对比

| 类型 | 算法示例 | 密钥管理 | 速度 | 典型应用 |

|---|---|---|---|---|

| 对称加密 | AES、DES | 密钥分发困难 | 快 | 文件加密、会话加密 |

| 非对称加密 | RSA、ECC | 公钥公开,私钥保密 | 慢 | 密钥交换、数字签名 |

| 哈希算法 | SHA-256、MD5 | 无密钥 | 快 | 数据完整性验证 |