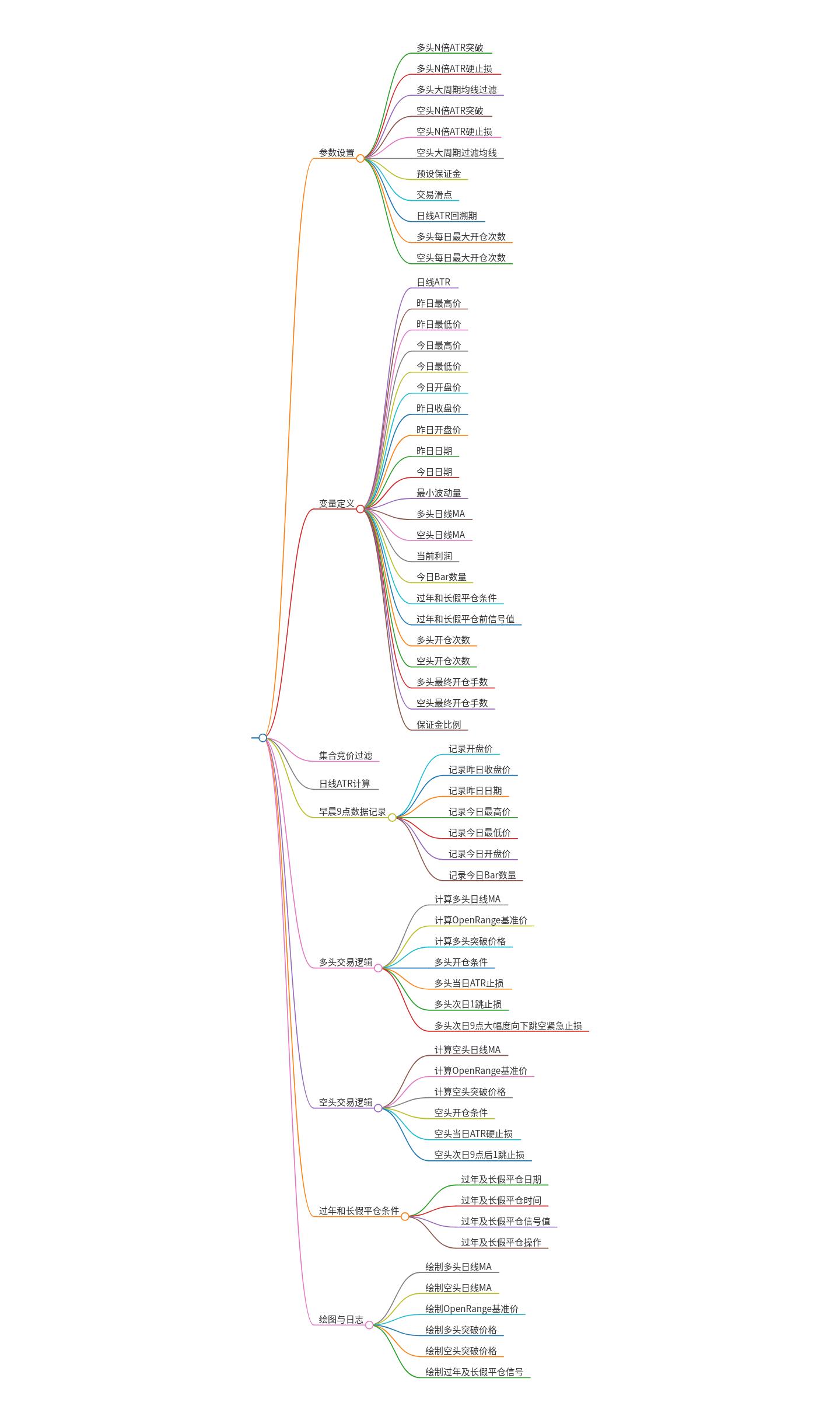

目录

一、校验码

码距

奇偶校验码

循环冗余校验码(CRC)

海明码

真题示例:

二、体系结构

Flynn分类法

三、指令系统

指令组成

指令执行过程

指令的寻址方式

操作数的寻址方式

CISC vs RISC

真题示例:

四、流水线技术

1. 基本概念

2. 流水线优化技术

真题示例:

一、校验码

-

码距

- 单个编码的码距为1(如

00变为01需改1位)。 - 两个编码间的码距是转换所需改变的最小位数(如

00→11码距为2)。 - 码距越大,纠错和检错能力越强。

- 单个编码的码距为1(如

-

奇偶校验码

- 奇校验:编码中1的个数为奇数;偶校验:1的个数为偶数。

- 码距为2,只能检1位错,无法纠错。

-

循环冗余校验码(CRC)

- 通过生成多项式(如

G(x)=x^4+x+1)计算校验位,只能检错,不能纠错。 - 步骤:

- 原始信息后补

r个0(r为生成多项式阶数)。 - 模2除法(不进位、不借位)计算余数。

- 余数作为校验位附加到原始信息后。

- 原始信息后补

- 接收方校验:用相同

G(x)除接收到的数据,余数为0则无错。

- 通过生成多项式(如

-

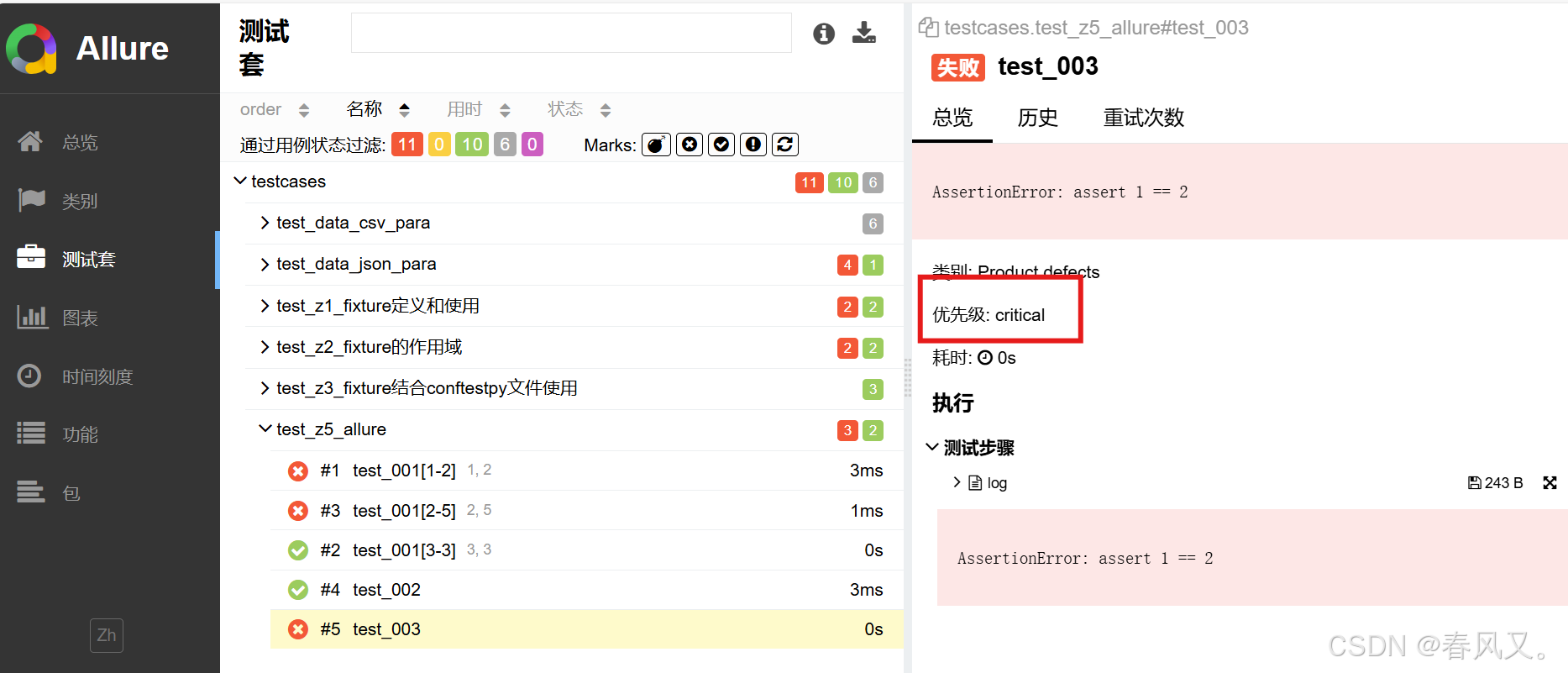

海明码

- 原理:通过插入校验位扩大码距,实现检错和纠错。

- 校验位位置:位于

2^n(如第1、2、4、8位)。 - 计算校验位:

- 数据位编号拆分后,校验位由其覆盖的数据位异或得到(如第4位校验

D7、D6、D5)。

- 数据位编号拆分后,校验位由其覆盖的数据位异或得到(如第4位校验

- 纠错:接收方通过异或运算定位错误位并纠正。

- 公式:

2^k - 1 ≥ n + k(n为数据位数,k为校验位数)。

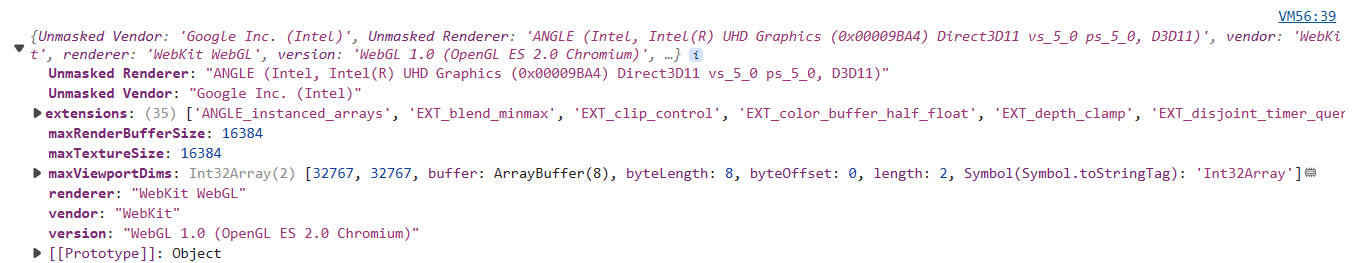

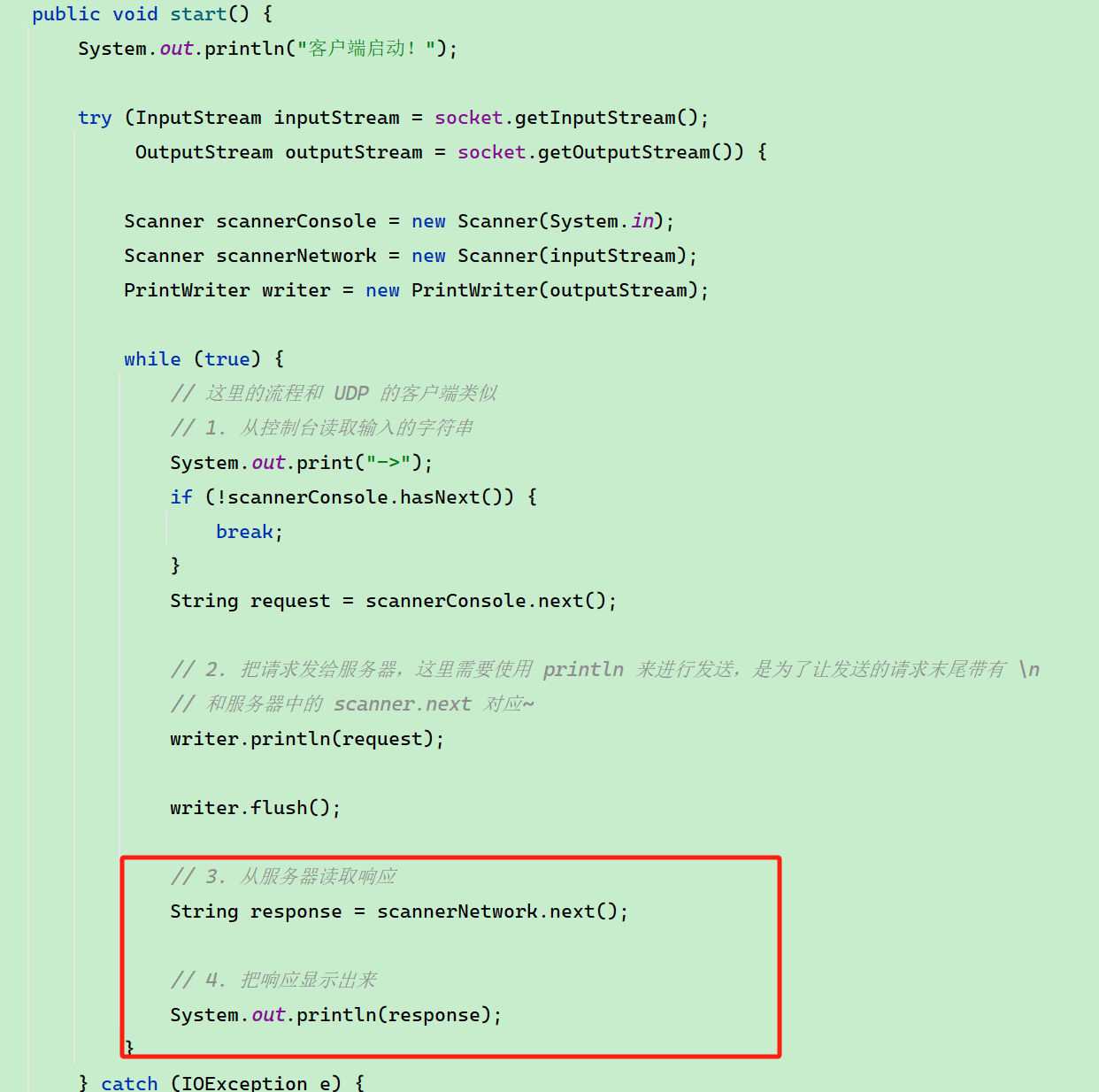

计算校验码

将所有信息位的编号都拆分成二进制表示,如下所示:

7 6 5 4 3 2 1 位数 1 0 1 1 信息位 0 0 1 校验位 上图中,7=4+2+1,表示7由第4位校验位(r2)和第2位校验位(r1)和第1位校验位(r0)共同校验,同理,第6位数据位6=4+2,第5位数据位5=4+1,第3位数据位3=2+1,前面知道,这些2的n次方都是校验位,可知,第4位校验位校验第7、6、5三位数据位,因此,第4位校验位r2等于这三位数据位的值异或,第2位(7,6,3)和第1位(7,5,3)校验位计算原理同上。

计算出三个校验位后,可知最终要发送的海明校验码为1010101

检错和纠错原理

接收方收到海明码之后,会将每一位校验位与其校验的位数分别异或,即做如下三组运算:

r2⊕I4⊕I3⊕I2; r1⊕I4⊕I3⊕I1; r0⊕I4⊕I2⊕I1;

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 位数 |

|---|---|---|---|---|---|---|---|

| I4 | I3 | I2 | I1 | 信息位 | |||

| R2 | R1 | R0 | 校验位 |

校验类型

| 校验类型 | 校验位计算公式 | 示例(数据1011) |

|---|---|---|

| 偶校验 | ri=覆盖数据位异或 | r2=I4⊕I3⊕I2=1⊕0⊕1=0 |

| 奇校验 | ri=覆盖数据位异或⊕1 | r2=(1⊕0⊕1)⊕1=1 |

如果是偶校验,那么运算得到的结果应该全为0,如果是奇校验,应该全为1,才是正确,假设是偶校验,且接收到的数据为1011101(第四位出错),此时,运算的结果为:

r2⊕I4⊕I3⊕I2=1⊕1⊕0⊕1=1; r1⊕I4⊕I3⊕I1=0⊕1⊕0⊕1=0; r0⊕I4⊕I2⊕I1=1⊕1⊕1⊕1=0;

错误定位原理

| 校验子 | 错误位置 | 数学原理 |

|---|---|---|

| 100 | 第4位 | 2²=4 |

| 011 | 第3位 | 2¹+2⁰=3 |

| 101 | 第5位 | 2²+2⁰=5 |

这里不全为0,表明传输过程有误,并且按照r2r1r0排列为二进制100,这里指出的就是错误的位数,表示第100,即第4位出错,找到了出错位,纠错方法就是将该位逆转。

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 位数 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 信息位 | |||

| 0 | 0 | 1 | 校验位 |

真题示例:

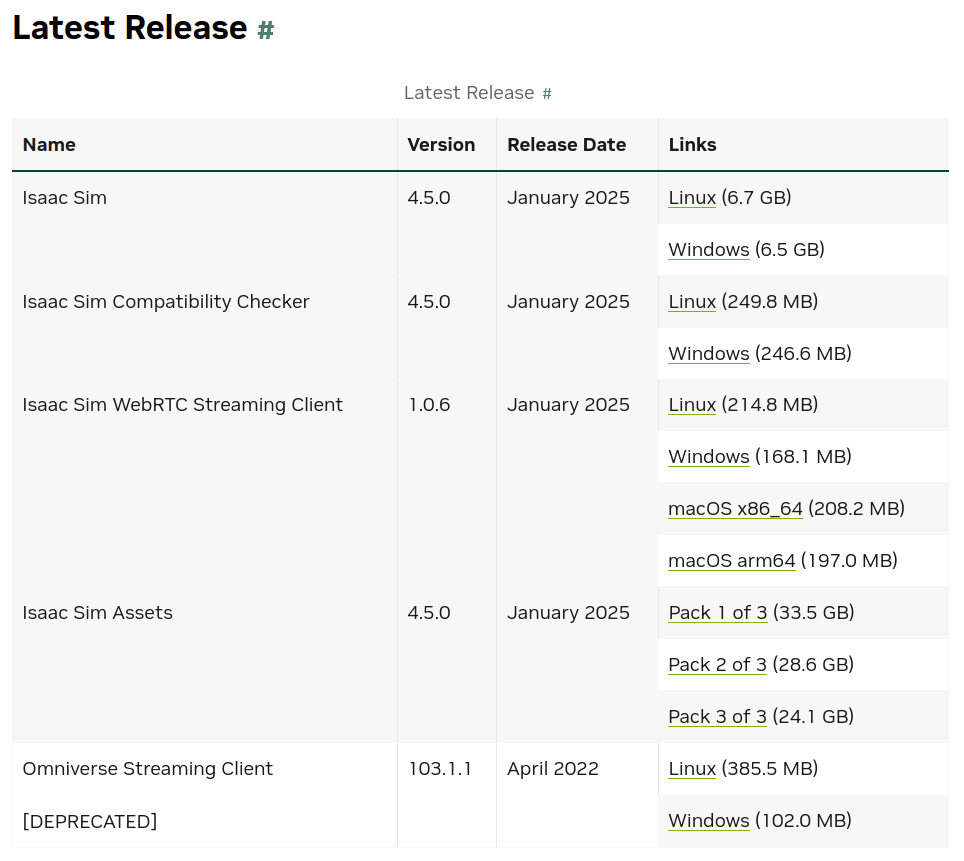

循环冗余校验码(Cyclic Redundancy Check,CRC)是数据通信领域中最常用的一种差错校验码,该校验方法中,使用多项式除法(模2除法)运算后的余数为校验字段。若数据信息为n位,则将其左移k位后,被长度为k + 1位的生成多项式相除,所得的k位余数即构成k个校验位,构成n + k位编码。若数据信息为1100,生成多项式为X³+X+1(即1011),则CRC编码是( )。

A.1100010 B.1011010 C.1100011 D.1011110

根据循环冗余校验码(CRC)的计算步骤来求解。

步骤一:确定数据信息和生成多项式

- 数据信息为

1100 ,其位数n = 4 。 - 生成多项式为 X^3+X+1 ,对应的二进制序列为

1011 ,其长度为 k+1=4 ,则 k=3 ,即校验位的位数为3位。

步骤二:对数据信息左移k位

将数据信息 1100 左移 k=3 位,得到 1100000 。

步骤三:进行模2除法

用左移后的数 1100000 除以生成多项式对应的二进制序列 1011 ,模2除法的计算过程如下:

- 被除数

1100000 ,除数1011 ,第一次相除:1100 -1011 =0011 ,商1 。 - 把被除数下一位

0 移下来,得到00110 ,继续相除:00110 -00000 (因为1011 大于00110 ,这里减0 ) =00110 ,商0 。 - 再把被除数下一位

0 移下来,得到001100 ,相除:001100 -1011 =0101 ,商1 。 - 把被除数最后一位

0 移下来,得到01010 ,相除:01010 -1011 =0001 ,商1 。

最终得到余数为 010 ,这就是3位校验位。

步骤四:得到CRC编码

将校验位 010 附加到原数据信息 1100 后面,得到 1100010 ,即CRC编码为 1100010 。

海明码是一种纠错码,其方法是为需要校验的数据位增加若干校验位,使得校验位的值决定于某些被校位的数据,当被校数据出错时,可根据校验位的值的变化找到出错位,从而纠正错误。对于32位的数据,至少需要加()个校验位才能构成海明码。

设数据位为m位,校验位为r位,要构成海明码需要满足2^r≥m+r+1。 已知数据位m=32,我们可以通过代入不同的r值来进行验证:

- 当r=5时,25=32,m+r+1=32+5+1=38,32<38,不满足条件。

- 当r=6时,26=64,m+r+1=32+6+1=39,64>39,满足条件。

所以对于32位的数据,至少需要加6个校验位才能构成海明码

以10位数据为例,其海明码表示为D9D8D7D6D5D4 P4 D3D2D1 P3 D0 P2P1中,其中Di(0≤i≤9)表示数据位,Pj(1≤j≤4)表示校验位,数据位D9由P4、P3和P2进行校验(从右至左D9的位序为14,即等于8 + 4 + 2,因此用第8位的P4、第4位的P3和第2位的P2校验),数据位D5由()进行校验。

A.P4P1 B.P4P2 C.P4P3P1 D.P3P2P1

从右至左数据位D5的位序为10。将10转换为二进制数:10(10)=1010(2)=2^3+2^1=P4P2

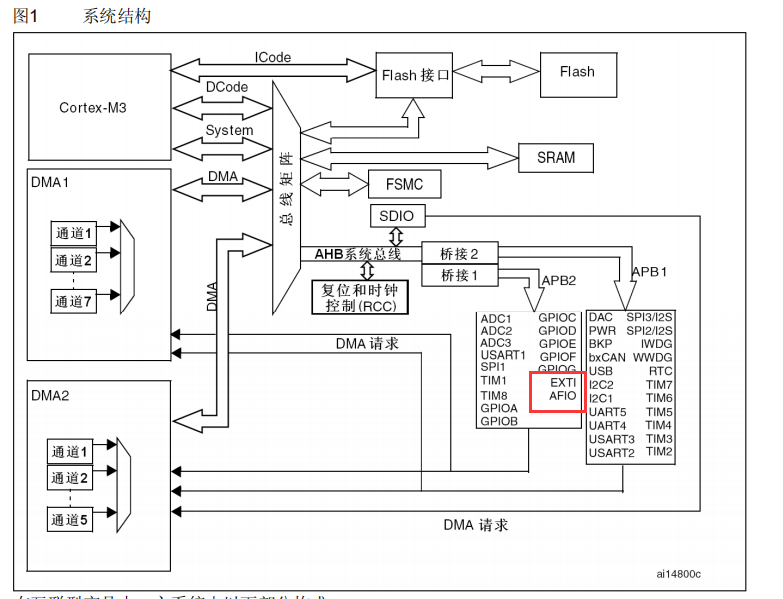

二、体系结构

-

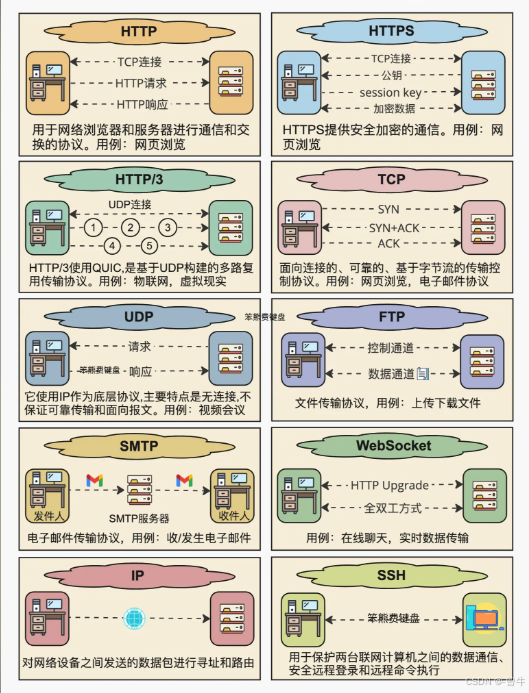

Flynn分类法

根据指令流和数据流的组合方式,计算机体系结构分为4类:

类型 指令流 数据流 特点 代表 SISD 单 单 传统单核串行处理器 单CPU计算机 SIMD 单 多 单指令并行处理多数据 向量机、GPU MISD 多 单 理论存在,无实际应用 - MIMD 多 多 多指令多数据并行 多核CPU、分布式系统 - 多核计算机属于MIMD(多指令流多数据流)。

- MISD不可行:因一条数据流无法被多条指令同时控制。

三、指令系统

-

指令组成

- 操作码:指定操作类型。

- 操作数:参与运算的数据或地址。

-

指令执行过程

-

指令的寻址方式

- 顺序寻址:一条指令接一条指令顺序执行。

- 跳跃寻址:下一条指令的地址码由本条指令给出,跳转后开始顺序执行。(程序计数器的内容也相应改变,以便跟踪新的指令地址)

-

操作数的寻址方式

方式 特点 示例(MOV R1, [X]) 立即寻址 操作数为直接值 MOV R1, 5 直接寻址 地址码为内存地址 MOV R1, [1000H] 间接寻址 地址码指向的内存存储实际地址 MOV R1, [[1000H]] 寄存器寻址 操作数在寄存器中 MOV R1, R2 基址寻址 基址寄存器 + 偏移量 MOV R1, [BX+10H] 变址寻址 变址寄存器 + 偏移量 MOV R1, [SI+20H] -

CISC vs RISC

特性 CISC(复杂指令集) RISC(精简指令集) 指令数量 多(支持复杂操作) 少(仅常用指令) 指令长度 可变长 固定长度 实现方式 微程序控制 硬件实现(硬布线) 寄存器使用 较少 大量通用寄存器 典型应用 x86架构(Intel/AMD) ARM、MIPS、RISC-V

真题示例:

Flynn分类法根据计算机在执行程序的过程中( )的不同组合,将计算机分为4类。当前主流的多核计算机属于( )计算机。

A.指令流和数据流 B.数据流和控制流 C.指令流和控制流 D.数据流和总线带宽

A.SISD B.SIMD C.MISD D.MIMD

Flynn分类法就是依据指令流(计算机执行的指令序列)和数据流(指令执行过程中处理的数据序列)的不同组合来对计算机体系结构进行分类的,这是该分类法的基本定义。

多核计算机中,每个核心可以同时执行不同的指令,处理不同的数据,MIMD(多指令流多数据流)符合多指令流多数据流的特点。SISD(单指令流单数据流)是传统单核串行处理器;SIMD(单指令流多数据流)如向量机、GPU,一条指令处理多个数据;MISD(多指令流单数据流)理论上存在,但实际中没有应用。

以下关于复杂指令集计算机(Complex Instruction Set Computer,CISC) 的叙述中,正确的是( )。

A.只设置使用频度高的一些简单指令,不同指令执行时间差别很小

B.CPU中设置大量寄存器,利用率低

C.常采用执行速度更快的组合逻辑实现控制器

D.指令长度不固定,指令格式和寻址方式多

关于复杂指令集计算机(CISC)的叙述中,正确的是指令长度不固定,指令格式和寻址方式多

- 选项A:只设置使用频度高的一些简单指令,不同指令执行时间差别很小,这是RISC(精简指令集计算机)的特点,而不是CISC的特点,CISC指令集复杂,指令执行时间差别大。

- 选项B:CISC中寄存器数量较少,利用率低,而不是设置大量寄存器,RISC通常设置大量通用寄存器。

- 选项C:CISC常采用微程序控制实现控制器,而不是组合逻辑,RISC常采用执行速度更快的组合逻辑实现控制器。

- 选项D:CISC指令长度不固定,指令格式和寻址方式多,这是CISC的典型特征。

四、流水线技术

1. 基本概念

- 流水线周期:最长段的执行时间。

- 总时间公式:

- 吞吐率:单位时间完成的指令数 = 指令数 / 总时间。

- 加速比:

(理想情况下,加速比≈流水线段数k)

2. 流水线优化技术

| 技术 | 原理 | 特点 |

|---|---|---|

| 超流水线 | 增加流水线级数(时间换空间) | 提高主频,减少每段耗时 |

| 超标量 | 并行多条流水线(空间换时间) | 需硬件调度,提高IPC |

| VLIW | 超长指令字,软件调度并行 | 硬件简单,依赖编译器优化 |

真题示例:

吞吐率

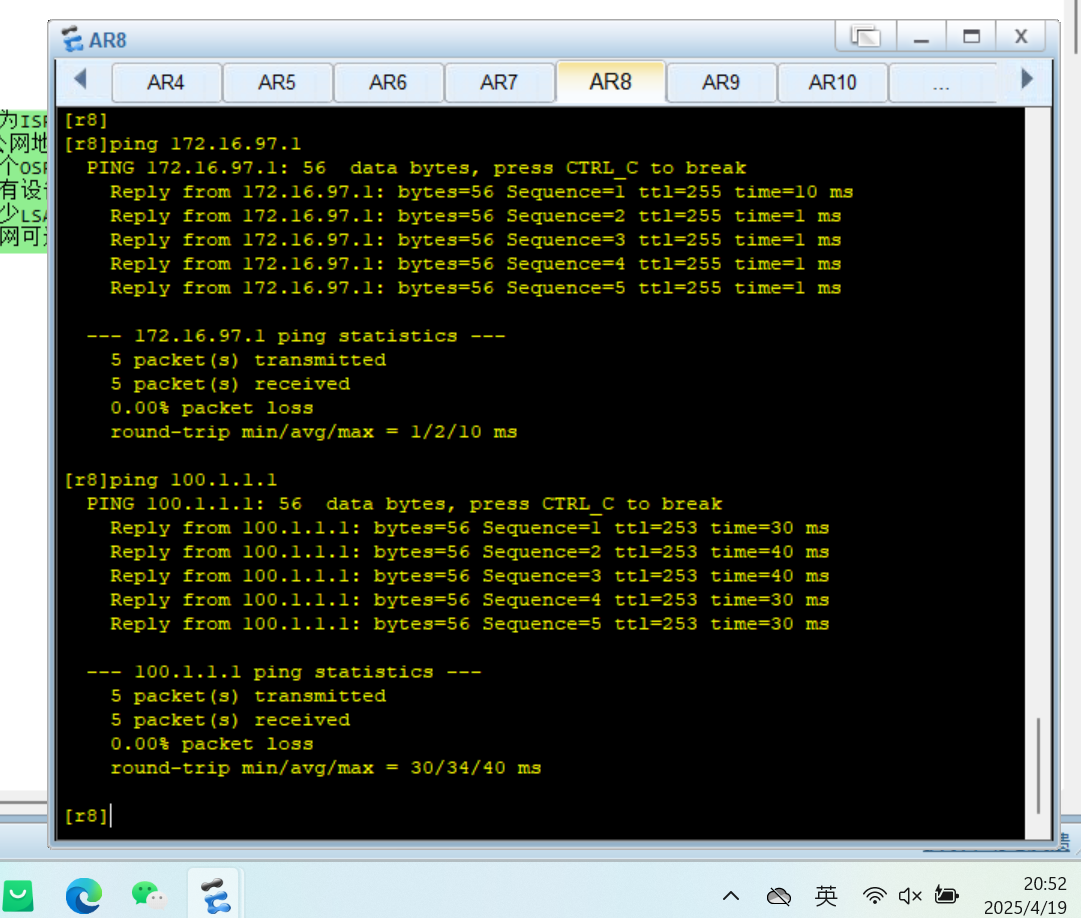

流水线的吞吐率是指流水线在单位时间里所完成的任务数或输出的结果数。设某流水线有5段,有1段的时间为2ns,另外4段的每段时间为1ns,利用此流水线完成100个任务的吞吐率约为( )个/s。

A.500×10^6 B.490×10^6 C.250×10^6 D.167×10^6

- 确定流水线周期:

- 流水线周期由流水线中耗时最长的段决定。在该流水线中,有1段时间为2ns,另外4段每段时间为1ns,所以流水线周期T=2ns。

- 计算完成100个任务的总时间:

- 根据公式总时间=第一条指令完整时间+(指令数−1)×流水线周期。

- 第一条指令完整通过5段流水线,时间为2+1+1+1+1=6ns。

- 后面100−1=99条指令,每条指令的执行时间为流水线周期2ns。

- 所以总时间t=6+(100−1)×2=6+198=204ns。

- 计算吞吐率:

- 吞吐率TP=总时间指令数,指令数为100,总时间t=204ns=204×10^−9s。

- 则

个/s

缓冲区

假设磁盘块与缓冲区大小相同,每个盘块读入缓冲区的时间为15μs,由缓冲区送至用户区的时间是5μs,在用户区内系统对每块数据的处理时间为1μs,若用户需要将大小为10个磁盘块的Doc1文件逐块从磁盘读入缓冲区,并送至用户区进行处理,那么采用单缓冲区需要花费的时间为( )μs;采用双缓冲区需要花费的时间为( )μs。

A.150 B.151 C.156 D.201

A.150 B.151 C.156 D.201

单缓冲区情况

- 分析处理过程:

- 采用单缓冲区时,读入一块数据到缓冲区需要15μs,从缓冲区送至用户区需要5μs,在用户区处理需要1μs。

- 处理第一块数据时,总时间为15+5+1=21μs。

- 从第二块开始,因为是串行处理,每块数据的处理时间为读入时间(15μs,因为在将上一块数据从缓冲区送至用户区并处理时,下一块数据不能读入缓冲区),所以后面9块数据每块处理时间为15μs。

- 计算总时间:

- 总时间t=(15+5+1)+(10−1)×15=21+135=201μs

双缓冲区情况

- 分析处理过程:

- 采用双缓冲区时,两个缓冲区可以交替工作。读入第一块数据到第一个缓冲区需要15μs,然后将第一块数据从第一个缓冲区送至用户区需要5μs,在用户区处理需要1μs,共15+5+1=21μs。

- 在这21μs内,第二块数据可以读入第二个缓冲区(15μs)。

- 之后,从第二个缓冲区送数据到用户区和处理的同时,可以将第三块数据读入第一个缓冲区,以此类推。

- 实际上,除了第一块数据的读入、传送和处理是顺序进行外,后面9块数据的读入时间可以和前面数据的传送与处理时间重叠。

- 计算总时间:

- 总时间t=10×15+5+1=156μs

加速比

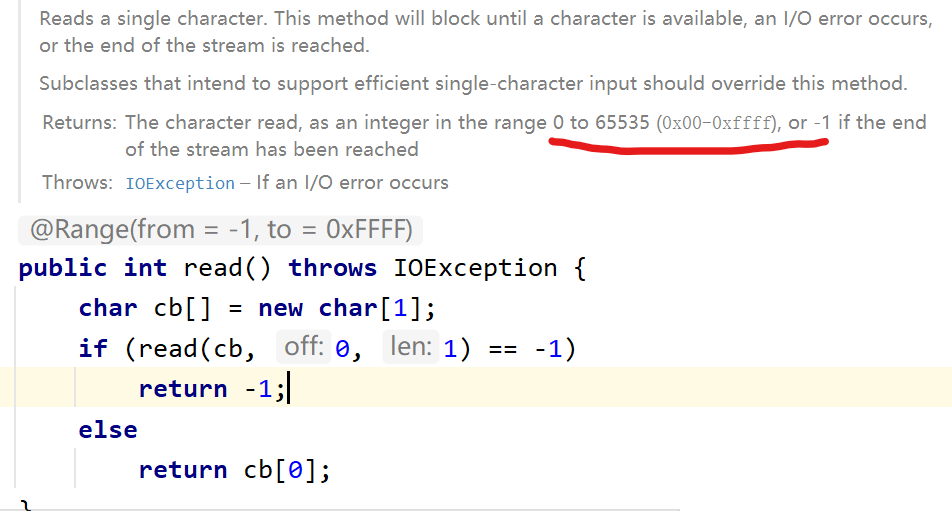

流水线技术是通过并行硬件来提高系统性能的常用方法。对于一个k段流水线,假设其各段的执行时间均相等(设为t),输入到流水线中的任务是连续的理想情况下,完成n个连续任务需要的总时间为( )。若某流水线浮点加法运算器分为5段,所需要的时间分别是6ns、7ns、8ns、9ns和6ns,则其最大加速比为( )。

A. nkt B. (k + n - 1)t C. (n - k)kt D. (k + n + 1)t

A. 4 B. 5 C. 6 D. 7

-

流水线总时间公式:

- 第一条指令需要完整通过k段流水线,耗时kt。

- 后续每条指令只需要一个流水线周期t(因为流水线已充满)。

- 因此,n条指令的总时间为:

T=kt+(n−1)t=(k+n−1)t

-

流水线周期:

- 流水线周期由最慢的段决定,即

。

- 流水线周期由最慢的段决定,即

-

非流水线时间:

- 非流水线情况下,一条指令需要完整通过所有段:

- 非流水线情况下,一条指令需要完整通过所有段:

-

最大加速比:

- 加速比公式:

- 题目问的是“最大加速比”,即理论极限。

- 加速比公式: