3 高速电路 PCB 设计要点

3.1 PCB设计与信号完整性

随着电子技术的发展,电路的规模越来越大,单个器件集成的功能越来越多,速率越来越高,而器件的尺寸越来越小。由于器件尺寸的减小,器件引脚信号变化沿的速率变得越来越高,以致 SI(Signal Integrity,信号完整性)问题成为高速电路设计中必须面对的主要问题。

一般而言,SI 与以下几个因素有关:反射、串扰、辐射、反射是由信号传输路径上的阻抗不连续造成的;串扰与信号的间距有关;而辐射则与高速器件自身以及 PCB 设计均有关。

以下将分几点探讨如何保证高速电路设计的信号完整性。

1.信号的阻抗匹配

信号的阻抗匹配是影响信号完整性最主要的因素。

首先讨论什么样的信号需要考虑阻抗匹配。在第 1 章已经提到,信号的有效频率Fknee取决于信号的边沿速率,当信号的有效频率Fknee比较低,使得信号的有效波长λknee大于信号走线长度的 6 倍时,该信号线可被视为集总式,即,在某一特定时刻,信号线路上任一点的电平状态都近似相同,否则,该信号线应被视为分布式,信号线的走线以传输线来对待。

【案例 2】传输线的判断

判断以下信号的走线是否属于传输线。

信号 1:周期频率 100MHz,上升沿时间 2ns,走线长度 6in(英寸)。

信号 2:周期频率 10MHz,上升沿时间 0.5ns,走线长度 6in。

【讨论】

根据第 1 章介绍的Fknee和λknee计算公式,可得:

对信号 1:

Fknee=0.5/2ns=250MHz

λknee=C/Fknee=(3x10^8 m/s)/250MHz=1.2m=47in(8.1)

对信号 2:

Fknee=0.5/0.5ns=1000MHz

λknee=C/Fknee=(3x10^8 m/s)/1000MHz=0.3m=12in(8.2)

其中,1m=39.37in。

信号 1 走线长度为 6in,小于λknee的 1/6,因此可以视为非传输线。信号 2 走线长度同样为 6in,大于λknee的 1/6,在设计时,应视为传输线。

对于传输线,必须考虑在信号传输路径上阻抗不匹配而带来的反射。信号的反射可利用反射系数ρ计算:

ρ=(Z2-Z1)/(Z2+Z1)(8.3)

式中Z2——反射点之后的线路阻抗;

Z1——反射点之前的线路阻抗。

【案例 3】反射的计算

信号的发送端在 A 点,接收端在 B 点,信号线为传输线,如下图所示,A 点到 B 点的走线传输延时为 5ns,信号输出电平为 3.3V。发送端器件的输出阻抗和传输线阻抗都是 50Ω,则在接收端器件的输入阻抗为 0Ω和无穷大的两种情况下,A 点波形分别如何?

【讨论】

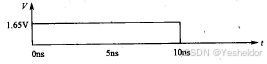

在 A 点,由于发送端器件输出阻抗和传输线阻抗都是 50Ω,因此在 A 点存在分压,信号电平为发送端输出电平的一半,即 1.65V。

当接收端器件的输入阻抗为 0Ω时,

ρ=(0-50)/(0+50)=-1(8.4)

ρ=-1,表示在 B 点,信号将以反向电平而全反射,即反射电平为-1.65V。

反射信号回到 A 点后,

ρ=(50-50)/(50+50)=0(8.5)

ρ=0,表示在 A 点,信号全部被吸收而不再发生反射。

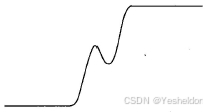

因此,A 点波形如图 下图所示。

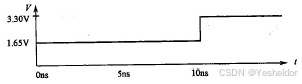

当接收端器件的输入阻抗为无穷大时,

ρ=(∞-50)/(∞+50)=1(8.6)

ρ=1,表示在 B 点,信号将以正向电平而全反射,即反射电平为 1.65V。

反射信号回到 A 点后,同样全部被吸收而不再发生反射。

因此,A 点波形如下图所示。

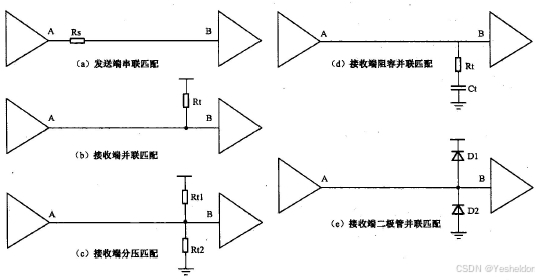

始端、传输路径、终端阻抗的不匹配,都会造成信号的反射。为减小反射,需尽可能地减小反射系数ρ,即要求Z2尽可能地等于Z1。通过在电路上增加元件以减小ρ的方法,称为阻抗匹配设计。电路设计中常用的匹配方式有五种:发送端串联匹配、接收端并联匹配、接收端分压匹配、接收端阻容并联匹配、接收端二极管并联匹配,如下图所示。

1)发送端串联匹配

单点对单点的信号连接,应采用发送端串联匹配。该匹配方式使发送端器件输出阻抗与发送端匹配电阻Rs的和,近似地等于传输线阻抗。这种匹配方式只是实现了发送端的匹配,由以上案例可知,信号传输路径上的电平约为驱动电平的一半,而接收端器件阻抗较大,反射系数ρ近似为 1,从而造成在接收端的全反射,全反射后接收端电平正好等于发送端的驱动电平。

优点:发送端匹配不会引起额外的功耗;匹配方式简单,且不会增加信号线路的 stub(stub:分支)。

缺点:一般仅适用于点对点的信号;受发送端分压的影响,传输路径上的电平低于驱动电平,在接收端,必须依靠反射才能恢复电平;另一方面,匹配电阻\(R_s\)的存在将使信号的边沿变缓,在时序要求较小的场合下,应权衡选择Rs的阻值。

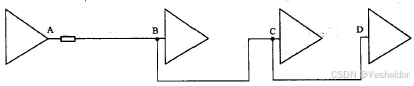

为补充说明的是,若采用发送端串联匹配实现单点对多点的连接,走线应成菊花链式,如下图所示。

由于串联匹配需通过反射才能在接收端建立电平,上图中,D 点的电平最先建立,而 A 点最晚,从时序裕量的方面考虑,D 点最好,然后依次是 C、B。

2)接收端并联匹配

接收端并联匹配适用于单点对多点的连接,与发送端匹配不同,接收端匹配无须借助反射以建立电平,通过使匹配电阻Rt的阻值等于传输线阻抗,可实现接收端的阻抗匹配。

优点:不会影响信号的边沿速率。

缺点:需要在电阻Rt上消耗一定的功率;在接收端,相对电平判别门限,很容易出现低电平不对称的现象。

3)接收端分压匹配

这是 LVPECL 等高速电平常用的匹配方式,对匹配电阻R1和R2的取值,请参考第 3 章相关内容。

优点:不影响信号的边沿速率;较容易实现接收端高、低电平相对门限电平的对称分布;可满足接收端对共模偏置电平的要求。

缺点:需要在电阻R1和R2上消耗一定的功率,当采用接收端分压匹配方式的信号数目较多时,在功耗评估的过程中,不能忽略匹配电阻上的功耗。

4)接收端阻容并联匹配

在上图(b)、(c)的匹配方式中,接收端匹配电阻与电源或地之间直接相连,存在直流通路,产生了一定的功耗,而在阻容并联匹配中,电容C1可阻断该通路,有效地减小了功耗,一般R1的阻值与传输线阻抗近似相等,C1选取几十至几百皮法的陶瓷电容即可。

优点:相对其他接收端匹配方式,功耗较小。

缺点:与上图(b)中的匹配方式类似,同样存在接收端高、低电平不对称的问题;另一方面,由于C1的存在,将使信号的边沿变缓。

5)接收端二极管并联匹配

严格来说,二极管并联匹配只能实现对接收端器件的保护,而无法实现阻抗匹配。当在传输线路径上存在阻抗不匹配时,接收端信号可能存在过冲,对器件的使用寿命构成影响。二极管能有效绝对过冲电平进行钳位,从而实现了对接收端器件的保护。

一般而言,在许多器件的输入端,片内已内置了类似的并联二极管,在这种情况下,设计时,不再需要外加二极管。

优点:保护接收端器件的输入端口。

缺点:无法消除反射;且在功能上,受限于二极管的开关速度。

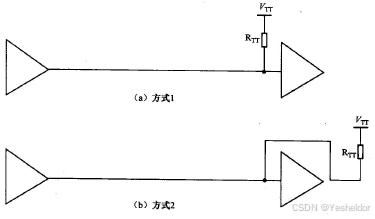

【案例 4】DDR SDRAM 设计时,终端电阻RTT布放位置的选择

在第 7 章对 DDR SDRAM 的介绍中提到,地址、数据信号线在接收端需通过终端电阻RTT上拉至电源VTT,那么,RTT应布放在接收端器件引脚之前还是之后?

【讨论】

本案例对RTT布放位置的讨论,实际上是一个阻抗匹配的问题,如下图所示。在方式 1 中,RTT的上拉路径对于信号线而言,相当于 stub(走线分支),对信号完整性有一定的影响;在方式 2 中,RTT的上拉路径与信号线属于同一路径,并不构成 stub,且RTT作为路径的终端,只要满足RTT与传输线阻抗相等的条件,则不会发生反射,不影响接收端的信号完整性。

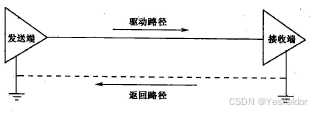

2.信号回路

在上一节的讨论中提到,对层叠结构的设计,很重要的一点就是要保证高速信号的回流,本小节将就这一点展开深入的讨论。

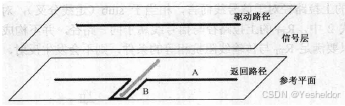

如下图所示,信号的传输路径是由两条方向相反的路径构成,一条是驱动路径,由发送端指向接收端,一条是返回路径,由接收端指向发送端。在发送端、传输路径、接收端测得的信号电平,实质上是该信号在驱动路径和返回路径上对应位置的电压值,由此可以看出,对于信号完整性,这两条路径同样重要。

信号传输时,驱动路径即为信号的 PCB 走线,返回时则选择与驱动路径阻抗最小的路径。需注意的是,这里提到的是“阻抗”而不是“电阻”,即,返回路径选择的是满足式 8.7 最小值的路径。对这条路径的选择,除考虑直流电阻外,还需考虑工作频率下回路的寄生电感和电容所产生的阻抗:

Z=R+jωL+1/(jωC)(8.7)

返回路径的选择方式如下图所示。

信号层的信号将寻找与自身阻抗最小的层作为参考平面,由上一节对阻抗的计算可知,与该信号层距离越近、且平面越完整的层,将被选为参考平面。在参考平面上,返回路径的选择仍将遵循与驱动路径阻抗最小的原则:

在 A 段,参考平面完整,返回路径完全平行于驱动路径。

在 B 段,参考平面存在一条间隙,该间隙与 A 段所处区域的电气性质不同,且与 A 区域之间通过无电气属性的介质隔离,这使得返回路径被迫绕道而行,因此,在 B 段,返回路径与驱动路径之间的阻抗将相对 A 段而增大,从而造成信号路径上阻抗的不连续。阻抗不连续的问题已经在前文讨论过,简要地说,阻抗不连续将造成信号电平的突变,而这种突变,又会带来信号完整性、EMI 等各方面的问题。除阻抗不连续外,B 段存在的另一个问题是信号返回路径上的串扰,由于间隙的存在,许多驱动路径与阻抗不同的其他信号,返回时阻抗最小的路径都是 B 段,使 B 段成为串扰的集中点,这同样不利于信号完整性。

信号回路均参考平面的选择密切相关,一般而言,高速信号应选择完整的电源平面作为参考平面,如果受层叠结构的限制,高速信号所在层距离地层较远,也应选择完整的电源平面作为参考平面。若受布局和布线的限制,PCB 上无法提供完整的电源平面或电源平面,那么至少应确保与高速信号驱动路径相对应的返回路径上无电气间断。

众所周知,完整的地平面是最好的参考平面,那么完整的电源平面是否可以起到同样的效果?

对多数信号而言,信号必须回到发送器件的 GND 才能完成回路,若参考平面为电源平面,则信号的返回路径为电源层,到达发送端后,还需由电源平面回到地平面才能完成回路,若电源层与地层之间距离较近,耦合大且阻抗小(事实上,减小两层之间介质的厚度是减小阻抗最有效的方法),则这种回流方式与地平面为回流的方式几乎没有差别,但若该电源层与地层之间的耦合较差,造成阻抗偏大(例如,该电源层与附近的地层相距较远),则该阻抗对信号的回流有一定的影响,对于这种情况,以电源平面为回流的方式达不到以地平面为回流方式的效果。需要注意的是,这一规则存在某些特例,例如,某些高速总线,如 DDR SDRAM 的控制、地址信号,建议以 2.5V 电源而不是地平面作为参考。

对于差分对信号,对内两信号互为对方提供返回路径,因此差分对内两信号之间的耦合非常重要。既然如此,是否可以该差分对与附近参考平面之间无需紧密耦合?答案是否定的,受限于器件工艺、PCB 走线等因素,对内两信号无法实现完全的对称,不可避免地存在共模分量。这部分共模分量需要通过参考平面实现回流,因此,对于差分对信号而言,与参考平面的耦合也同样重要。

以下继续讨论信号换层对返回路径的影响。

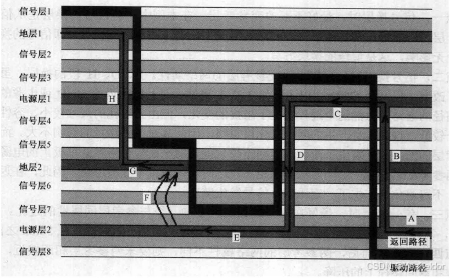

如下图所示,以一个 12 层板为例,说明信号换层时返回路径的选择。

该板有八层信号层,另有两层地层和两层电源层,这是高速电路设计中常见的层叠结构。图示信号通过过孔共经过了四次换层,这也是高密度电路设计常见的情况。为简便起见,假设两个电源层的网络相同(例如,都是 3.3V 的电源平面),且电源层和地层都是完整无分割的平面。

上图中,返回路径与驱动路径的方向相反,各段返回路径说明如下:

A 段:驱动路径位于信号层 8,其最近的参考层是电源层 2,因此,返回路径 A 段位于电源层 2。

B 段:驱动路径发生了换层,由信号层 3 换到信号层 8,与信号层 3 最近的参考层是电源层 1,换层前后参考层的网络属性相同,因此,返回路径可借助信号驱动路径附近的电源过孔实现。

C 段:驱动路径位于信号层 3,电源层 1 作为其参考层。

D 段:驱动路径发生了换层,由信号层 7 换到信号层 3,与信号层 7 最近的参考层是电源层 2,换层前后参考层的网络属性相同,与 B 段类似,返回路径借助驱动路径附近的电源过孔实现。

E 段:驱动路径位于信号层 7,电源层 2 作为其参考层。

F 段:驱动路径发生了换层,由信号层 5 换到信号层 7,与信号层 5 最近的参考层是地层 2,换层前后参考层的网络属性不同,返回路径无法借助过孔实现,只能利用电源层 2 和地层 2 之间的平面耦合电容以及电源的去耦电容形成通路。

G 段:驱动路径位于信号层 5,地层 2 作为其参考层。

H 段:驱动路径发生了换层,由信号层 1 换到信号层 5,与信号层 1 最近的参考层是地层 1,换层前后参考层的网络属性相同,与 B 段类似,返回路径借助驱动路径附近的地过孔实现。

由以上的讨论可以看出,信号换层时,其返回路径同样需要更换参考层,有以下要点需要注意:

要点一,信号换层时,最好不要改变参考层。在本例中,若信号的换层是从信号层 1 换到信号层 2,参考层都是地层 1,在这种情况下,返回路径无需换层,即信号的换层对其返回路径无影响,这是最佳的换层方案。

要点二,信号换层时,最好不改变参考层的网络属性。B、D、H 段的换层,虽然参考层发生了改变,但同为 GND 或电源(如 3.3V)属性,可利用附近的 GND 或电源的过孔实现返回路径的通路,虽然这个过程发生了阻抗的变化,但由于过孔的尺寸较小,容性、感性寄生成分较低,过孔本身产生的阻抗变化可忽略,因此其对返回路径的影响不大。而对于 C 段,参考层的网络属性发生了改变,返回路径只能借助平面耦合电容或单板上的电源耦合电容,且两参考层之间存在层间阻抗,当距离较远时,该阻抗不能被忽略,因此,在返回路径通过时,不可避免地产生了一定压降,信号发生畸变。

要点三,信号换层时,最好在信号过孔附近增加一个与参考层同属性的过孔。在 B、D、H 段,对该过孔的作用已做了讨论,一般要求该过孔与信号过孔距离在 50mil 之内。

要点四,若换层前后,两参考层的网络属性不同,则要求两参考层相距较近,以减小层间阻抗和返回路径上的压降。

要点五,当换层的信号较密集时,附加的地或电源过孔之间应保持一定距离。在第三点提到,信号换层时,信号过孔附近应增加地或电源过孔,当换层的信号很多时,一个地或电源过孔是不够的,需多打几个过孔,若这些过孔相邻较近,则信号回路上会产生串扰,返回路径上的串扰和驱动路径上的串扰对信号完整性的影响是相同的。尤其需要注意的是,由于信号的驱动路径是 PCB 上实际存在的走线,设计者往往对驱动路径上的串扰分析得比较多,而忽视了对返回路径的分析,事实上,信号的返回路径也是很容易出信号完整性问题的地方。

3.地弹

第 1 章已经提到,高速领域应采用分布式的视图来看待器件、走线等。

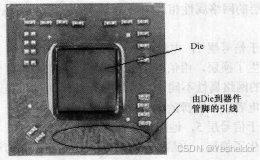

如下图所示是某高速器件的引脚示意图。器件的核心单元称为 Die,Die 一般较小,而器件所需的输入/输出接口数目较多,因此,在器件封装内,由引线连接 Die 与器件的外壳。在许多器件的表面,可以看到图中的这种引线。

在高速工作的条件下,Die 到器件引脚的这部分引线,其寄生感性将表现出很强的阻抗,频率越高,阻抗越大。

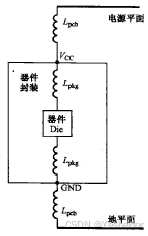

如下图所示为高速器件电源和地引脚的寄生电感示意图。从器件内核 Die 到 PCB 的电源、地平面,器件封装内的引线电感Lpkg、器件引脚到平面的走线电感Lpcb不可忽略,在工作频率较高的情况下,其表现出较大的阻抗,而电流的任何变化,将通过该阻抗转化为电平的波动。这种器件内核所感知到的电源或地相对 PCB 电源或地平面的电平波动称为地弹。由于地弹的存在,即便 PCB 上电源和地平面十分完美,器件内核的信号完整性仍然无法得到保证,更为重要的是,地弹是 EMI 的主要源头之一,若在电路设计中没有充分地考虑地弹的影响,到设计完成进行 EMC 测试时,往往会发现,面对由地弹引起的 EMI 问题,需增加大量的抗干扰器件,不仅提高了成本,而且某些问题还需改板才能得到解决。

在高速设计时,电路设计者无法减小器件封装内部的引线阻抗,但仍可以通过以下措施减小地弹的影响。

措施一,对 BGA 封装的器件,在表层,通过极短的走线将器件的电源、地引脚周边,再通过过孔与内层的电源、地平面相连;对表贴封装的器件,如 SO、TQFP 等封装,也应将电源、地引脚与电源、地平面就近相连,连接线应采用较粗的走线或是就近打过孔。

措施二,数据传输尽可能地采用扰码技术,避免出现多数数据引脚电平同时翻转的现象。器件高速工作时,若同时发生电平翻转的引脚很多,将产生很大的电流,而地弹电压波动等于电流与阻抗的乘积,电流越大,地弹越大,由多数数据引脚电平翻转造成的地弹噪声,称为 SSO(Simultaneous Switching Noise,同步开关噪声),通过扰码,可将接口信号调制成无杂乱无章的码型,达到减小 SSO 的效果。

措施三,返回路径的阻抗越大,地弹噪声越大。因此,保持信号回路的低阻抗,同样有利于减小地弹。

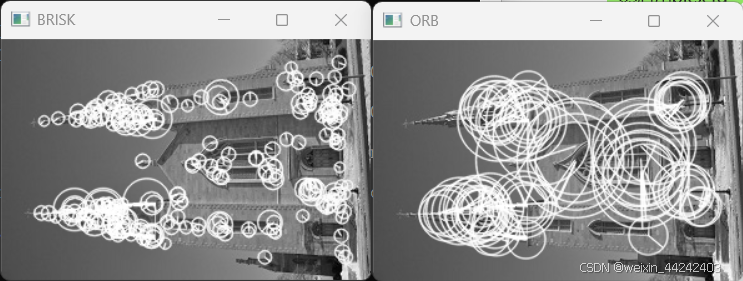

4.串扰

串扰(Crosstalk)是指信号线之间由互感、互容而引起的耦合,由于这种耦合的存在,当某一信号线发生电平的翻转时,在附近的信号线上将感应到一定程度的噪声。

在电路设计中,常用的抑制串扰的方法有以下几点。

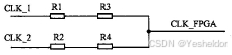

1)控制高速信号线之间的间距和平行走线的长度

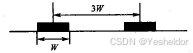

多个高速信号长距离平行走线时,其间距应遵循 3W 原则,如下图所示。

3W 原则指两相邻信号线的中心距不少于信号线宽度的 3 倍,当满足 3W 原则时,信号线之间由互感、互容而产生的互扰可减少 70%。

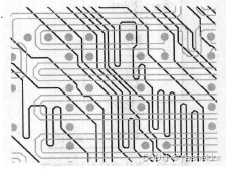

3W 原则不仅适用于对同一层信号线之间间距的约束,对相邻层的信号也同样适用,而这一点往往是很容易被忽略的。为避免相邻层的信号走线间距过小,一般建议交叉走线,如下图所示。

事实上,随着电路板密度的增加,往往无法保证所有信号线之间的间距都满足 3W 原则,一般地,对速率极高、对干扰极敏感的信号,如高速时钟,其与附近信号的间距,必须满足 3W 原则,对无法满足 3W 原则的高速信号,应做仿真实验予以验证。

【案例5】大驱动电流信号对高速数据信号的串扰

某单板在测试时发现 CPU 与 DDR SDRAM 之间的存储接口数据出错,运行底层驱动程序,可证实出错的位是 DQ。

【讨论】

该单板为 16 层板,根据第 7 章的介绍,PCB 设计时应对 DDR SDRAM 的数据总线分组,同组信号走在同一层,DQ[19]所在的组是 DQ[16:23],该组走线在第七层。在第七层附近,第六层是信号层,第八层是参考地平面。检查第七层的走线,DQ[19]信号的走线与该组其他信号类似,没有发现明显的区别,第八层是完整的参考平面,因此问题不在第七、八层。

同时打开第六、七两层,发现在第六层上,与第七层的 DQ19 平行地紧贴着,有一根 DCDC 电源电路的栅极驱动信号,估计问题的根源正是该信号对 DQ19 的串扰。调试时,将栅极驱动信号的源端电阻去掉,从而阻断了 PCB 上的栅极驱动路径,取而代之的是,利用飞线连接电源芯片的 GATE 引脚与 MOSFET 的栅极,重新测试,不再出现存储错误。

【拓展】

设计者在对串扰问题的检查时,很容易忽略两点:

其一,只对同一层信号的间距进行检查,而忽视了相邻信号层的信号。

其二,只对高速信号的间距进行检查,忽视了低速但有较高驱动能力的信号。本例就是这样的一个案例,在第 4 章对 MOSFET 的介绍中已经提到,MOSFET 的栅极驱动信号是有一定电流驱动能力的信号,且在 DCDC 电源工作的过程中,该信号将以数百 kHz 的频率进行翻转,虽不属于高速信号,但由于该信号的驱动能力较强,其对附近其他信号的串扰不能忽视。

2)降低信号的边沿速率

在第 1 章已经提到,高速信号的有效频率取决于信号的边沿速率而不是周期频率,因此信号边沿速率越高,相应地,有效频率也越高,而信号有效频率越高,越容易对附近信号产生耦合,进而造成串扰。

需补充说明的是,信号的边沿速率(或有效频率)不仅与串扰有关,还与信号完整性的其他方面以及 EMC 密切相关。

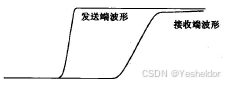

其一,现实中的信号由多种频率分量构成,在这些分量中,频率越高的分量,由 PCB 材质和趋肤效应引起的损耗越大,因此,在信号的传输过程中,高频分量的衰减远高于低频分量,从而,在接收端将出现信号边沿变缓的现象,如下图所示。

信号的频率越高,设计时越不能忽略传输路径上损耗的问题。在图 8.6 所示的层叠结构示例中,内层差分对信号的线宽和线间距分别选择为 4mil 和 6mil,普通的差分对信号可直接应用该规则,而对于极高频差分对信号,如 3.125GHz 的 XAUI 信号、10GHz 的 XFI 信号等,出于高频损耗的考虑,应加大线宽(线宽越宽,衰减越小),为达到同样的目标阻抗,同时还应增大这类极高频差分信号的线间距。即根据工作频率的不同,可为同一单板的差分对信号设置不同的线宽和线间距规则,在满足单板总厚度和目标阻抗的前提下,对普通差分对信号,从节省 PCB 面积的方面考虑,可选择较窄的线宽和线间距,对极高频的差分对信号,从高频信号衰减的方面考虑,应选择宽一些的线宽和线间距。因此,初学者有时候会发现,在一块 PCB 上,高频差分对信号的线间距反而比普通差分对信号的线间距大,正是这个原因。

其二,信号的有效频率越高,产生 EMI 问题的可能性越大。

其三,由第 1 章可知,判断信号线是否属于传输线依据是信号的有效频率,而信号的有效频率取决于边沿速率。因此,信号的边沿速率越高,越容易产生传输线效应,进而影响信号的完整性。

其四,信号边沿速率过高,产生过冲的可能性也越大,信号过冲超过一定范围,可能损坏器件或使 CMOS 工艺的器件门锁。

基于以上原因,从信号完整性以及 EMC 等方面考虑,希望信号的边沿速率低一些,但边沿速率的降低,又会导致时序裕量的减少,所以从时序方面考虑,又希望信号的边沿速率高一些。

许多高速器件,如 DDR SDRAM 等,内部有寄存器以设置不同的边沿速率,在设计中,需均衡考虑信号完整性、EMC、时序等方面,以正确地选择边沿速率。

需要说明的是,对于信号边沿速率,设计者往往关注的都是上升沿,事实上,信号的下降沿速率一般要高于上升沿。其原因在于,CMOS 器件的输出端一般由 NMOS 和 PMOS 互补地搭建而成,输出信号上升沿,即电平由低变高时,NMOS 关断而 PMOS 导通,反之,在输出信号的下降沿,NMOS 导通而 PMOS 关断,由于 NMOS 比 PMOS 导通的速度更快,因此信号的下降沿速率一般高于上升沿。从这一点来看,信号的下降沿更容易出现信号完整性的问题。

【案例6】高速接口器件批次更换造成辐射超标

某单板上接口器件的批次更改后,EMC 测试发现辐射超标。

【讨论】

利用示波器测量新批次接口器件的信号,发现信号的边沿速率快于以前的批次,使得接口部分的 EMC 性能发生恶化。

【拓展】

对于高速电路设计,由于工艺升级而造成的器件批次更新,测试时需仔细验证电源、信号的完整性,对于用户接口器件,还需进行 EMC、防护等测试。

3)降低阻抗

减小信号层与参考层之间的阻抗,实现高速信号的阻抗匹配,同样有助于减小信号间的串扰。

• 微带线和带状线的应用

微带线(Microstrip)指走线在 PCB 表层,且仅与一个参考层相邻的信号线。

带状线(Stripline)指走线在 PCB 内层,位于两个参考层之间的信号线。

前面图中第一层和第十六层的走线为微带线,其参考层分别为第二层和第十五层,而第六层或属于带状线,其参考层为第五、八层。

微带线介于两种材质之间,一种是空气,其\(E_r\)值略大于 1;另一种是 PCB 材质,\(E_r\)值一般处于 3.5~4.5 之间。

(1)微带线的特性:

① 层叠结构的设计无法准确地保证对微带线的阻抗控制。

② 介质常数越小,支持的信号传输速率越高,因此,微带线的传输速率略高于带状线。

③ 微带线直接走线于表层,无法有效地避免其对外界的辐射,同时以微带线走线的信号,抗干扰能力也较弱。

(2)带状线的特性:

① 易于实现对信号的阻抗控制。

② 信号传输速率略低于微带线。

③ 带状线处于两个参考层之间,能有效地屏蔽辐射,且信号的抗干扰能力更强。

在设计中,高速信号的走线应尽量采用带状线而不是微带线。同时,若信号的驱动路径既包含微带线又包含带状线,需注意,微带线的传输速率略高一些,在时序裕量较小的场合,应对微带线部分和带状线部分分别计算走线延时。

5.盲孔、埋孔技术

1)盲孔、埋孔的优势

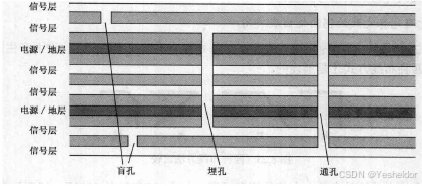

如下图所示,相对于通孔(Through hole via)、盲孔(Blind via)、埋孔(Buried via)有如下优势。

(1)盲孔、埋孔的出现,使更高密度的单板成为可能。随着器件性能的不断提高,高速器件的信号数目越来越多,引脚数在 1000 以上的器件比比皆是。若使用传统的通孔作为信号过孔,则要求较多的层数,而一般而言,单板的厚度都有一定的限度,因此,在总厚度一定的前提下,信号层的层数不可能无止境地增加。而基于盲孔、埋孔,在信号层上,能走线的区域得以增加,层数可以相对地减少,在总层数一定的前提下,单板所能支持的设计复杂度得到增加。

(2)盲孔、埋孔有助于提高信号完整性。原因有二:其一,过孔都存在一定的感性、容性等寄生参数,相对于通孔,盲孔、埋孔的孔径、深度都较小,因此,寄生参数也比较小。仿真可验证,信号过孔采用盲孔、埋孔后,其寄生的感性、容性参数尚不及通孔的一半之一,能极大地减小高频下过孔的阻抗,更好地保持信号传输路径阻抗的连续性;其二,盲孔、埋孔有助于减小信号线的 stub(分支);其三,盲孔、埋孔有助于获得更完整的电源、地参考平面。

2)在盲孔、埋孔的应用中需要注意的问题

(1)对盲孔、埋孔的应用,并不能随心所欲,必须与 PCB 生产厂家沟通可生产性以及成本。上图以八层板为例,若该单板同时要求 16 层的盲孔以及 38 层的盲孔,在 PCB 生产方面,将存在很大的难度。

(2)盲孔、埋孔有助于减少单板的总层数,但不一定能降低总成本,相反,由于盲孔、埋孔对生产的工艺和流程有特殊要求,很可能需要增加成本。

(3)应用盲孔、埋孔时,稍有不慎,反而可能对信号的完整性构成影响。在常规设计中,器件的电源、地引脚需通过通孔与内层的电源、地平面相连,这种做法,虽影响了平面的完整性,但却有利于各层电源或地的紧耦合。前面PCN叠层图示例的十六层板,第二、八、十五层都是地层,虽然它们的网络属性相同,却还需依赖过孔才能实现这三层的同一性,使用盲孔、埋孔,某些器件的某些地过孔只需要通过 12 层的盲孔与第二层地平面相连,从而减少了连接二、八、十五层的过孔,在极端情况下,三个地层之间可能出现松耦合,进而影响以地层为参考层的信号的完整性。

6. 布线

布线方式同样影响着信号完整性。

1)尽量避免在走线的拐角处出现尖角

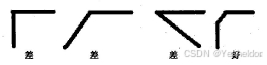

如下图所示,前三种布线方式,在拐角处都会出现线宽的变化,进而产生阻抗的变化,只有第四种布线方式才是最佳的。

另外,布线中的这种尖角,在信号速率极高(如 3.125GHz 的 XAUI、10GHz 的 XFI 等信号)的应用中,将构成 EMI 的源头。

2)尽量避免布线过程中线宽的变化

线宽的变化会造成阻抗的不连续,但在某些走线过程中不得不减小线宽,例如,走线从 BGA 封装的器件扇出时,线宽无法达到根据阻抗计算得出的宽度,只有走线出 BGA 区域后,才能恢复宽度,这就存在一个线宽变化的问题。

一般而言,若扇出时的走线长度较短,且信号速率不是特别高,则影响可忽略。但对极高速信号(如 3.125GHz 以上的信号),应寻找最近的路径扇出,且厂家在芯片设计时,一般也会注意将极高速信号的引脚排列在芯片的边缘,减少扇出的路径长度。

3)蛇形线

在设计时,为了满足时序的要求,经常需要绕线以满足信号的长度。蛇形线是绕线时常用的手段。前面图中的信号的走线就采用了蛇形线。

应用蛇形线时,需重点关注两个要素:平行线段的长度和线段之间的间距。这两个要素对信号完整性和时序都有影响。

平行线段之间会产生耦合,距离越近,平行长度越长,耦合越强,在前面对串扰的讨论中,已经介绍了这种耦合对信号完整性的影响。同时,信号的一部分高频分量将选择与蛇形线绕线垂直的方向传输,导致这部分分量提前到达终端,对接收端的时序和信号完整性造成影响。

因此,对蛇形线的应用,需注意两点,其一,仍然要求满足 3W 原则,其二,高频关键信号尽量不走蛇形线。

4)谨慎控制高速信号过孔的数目

过孔本身是一种容性负载,信号线上过孔过多,会降低信号的边沿速率,产生时序方面的问题。同时,过孔也是造成阻抗不连续的因素之一。因此,高速信号走线时,应尽量减少换层的次数。

5)走线分叉—stub

在阻抗匹配一节,已经提到 stub 会给信号带来反射,为减小 stub,需注意以下几方面。

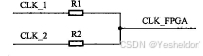

(1)信号分叉处用电阻间隔。如下图所示,FPGA 有两个可选的时钟源:CLK_1 和 CLK_2,通过电阻 R1 和 R2 进行选择。由于 R1 和 R2 只有一个能进入 BOM(Bill of Material,物料清单),在 PCB 设计时,R1 和 R2 之间的走线将成为 stub,因此,要求尽量地减小 R1 和 R2 之间走线的长度。

在设计时比较容易忽略的是,设计者基于串阻靠近发送端的原则,将 R1 和 R2 分别靠近各自的时钟驱动器输出端,当两个时钟驱动器相距较远时,R1 和 R2 之间也相距较远,在这种情况下,可在分叉处增加两个 0Ω电阻(R3 和 R4),如下图所示。

采用电路图 2 后,只需保证 R3 和 R4 之间的连线较短即可。

(2)高速信号线上过孔引入的 stub

当信号速率达到 10GHz,如 XFI 信号,极短的 stub 也会给信号带来严重的完整性问题。类似 10GHz 这种高速信号,拓扑结构往往是单点对单点,那么在走线上是否存在任何 stub?

答案是否定的。事实上,只要信号利用过孔换层,就可能存在 stub。以某支持 XFI 接口的器件为例,其封装为 BGA,根据层叠结构设计,单板为 16 层,XFI 信号线在内层走线,可供选择的内层是第三层和第十四层,这两层的阻抗和 EMC 屏蔽效果完全相同,以下讨论对于 XFI 信号,哪一层是最佳的走线层。

信号从 BGA 扇出后,需要利用过孔,从第一层转入内层,本设计中,过孔类型为 116 层的通孔,若选择第三层为走线层,则过孔的 316 层部分将表现为 stub,若选择第十四层为走线层,则过孔的 1416 层部分将表现为 stub。

十六层单板的总厚度一般为 2mm(约 80mil),316 层的厚度约为 70mil,1416 层的厚度约为 10mil。

厚度约为 10mil,因此,若选择第三层为走线层,由于过孔的存在,相当于在信号线上增加了一段长度为 70mil 的 stub,对设计者而言,当 70mil 的 stub 出现在信号的传输路径上,很容易受到重视,但对这种由于过孔而引起的 stub,则往往容易被忽略,其实,这两种情况都会对信号完整性构成影响,都需要得到同等的重视。

显然,在本例中,应选择第十四层为走线层。

为减小由高速信号过孔产生的 stub,另一种方法是采用背钻技术(Back Drill),如下图所示。

在前面的案例中,若选择第三层为走线层,利用钻头将过孔 316 层的金属部分钻除,同样也能起到减小 stub 的作用。

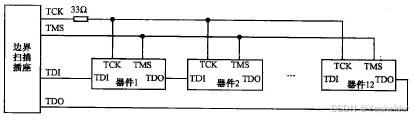

【案例7】TCK 信号出现回沟导致无法通过 JTAG 接口对 CPLD 进行加载

某单板在调试中发现无法通过 JTAG 接口(对该接口的讨论将在 3.7 节进行)加载 CPLD。

【讨论】

利用示波器测试 JTAG 接口的四个信号:TCK、TMS、TDI、TDO,发现在 TCK 信号上存在回沟,如下图所示。

TCK 信号电平为 LVTTL,高电平阈值为 2V,而回沟正好处于 2V 附近,出现了一次 TCK 上升沿触发两次数据采样的情况。

该设计中,将 12 个器件的 JTAG 接口串成一条边界扫描链路,链路如下图所示。TCK 信号的拓扑结构是单点对多点,以菊花链式连接多个器件,在源端串接 330Ω电阻。阻抗匹配一节已经讨论过,发送端串联匹配不适用于单点对多点的应用,信号上的回沟应是反射引起的。调试时,将串阻的阻值由 330Ω 更改为 0Ω,使回沟处的电平提高到 2.6V,避开了阈值门限,可以临时地解决该问题。

TCK 是 JTAG 接口中最关键的信号,虽然速率不高,但当负载数目过多时,仍然会产生完整性问题,对此,改板中做了以下改进。

一方面,更改 TCK 的匹配方式,采用接收端阻容并联匹配,即在器件 12 的 TCK 引脚与 GND 之间并联一个阻容电路,其中,电阻取值 51Ω,电容取值 220pF。

另一方面,减少单条 TCK 链路的负载数目,在源端,先通过 74LVC244 将一个 TCK 信号驱动为四个信号,使得驱动后,每个 TCK 信号的负载减少为三个,信号负载减少后,同样有助于信号边沿的完整性。

温馨提示

① 信号完整性的设计需关注的要点有:阻抗匹配、回路的连续性和无阻隔性、地弹、串扰等。

② 高速信号采用带状线,在成本允许的情况下,采用盲孔、埋孔技术,有利于获得更好的信号完整性。

③ 在布线的过程中,应注意避免出现尖角和缓宽的变化,线宽形变时同样应满足 3W 原则。

④ 不能忽略过孔引入的 stub。

![[物联网iot]对比WIFI、MQTT、TCP、UDP通信协议](https://i-blog.csdnimg.cn/direct/cb73323f30824085b063cfb2f7f6f2c3.png)

![P4305 [JLOI2011] 不重复数字](https://i-blog.csdnimg.cn/direct/1e5a4ac616ea4152a1e897b50c9df629.png)