Xilinx FIFO IP 输入 的最大位宽 是 1024 bit ,当需要缓存的数据是 1280bit 又或者是 1536等 。怎么办呢?

有一个办法就是拆数据,将1280拆5个 256bit输入,也就是可以使用 5个 256位宽输入的FIFO拼接起来。(其它位宽也行,如32bit等,8的倍数);

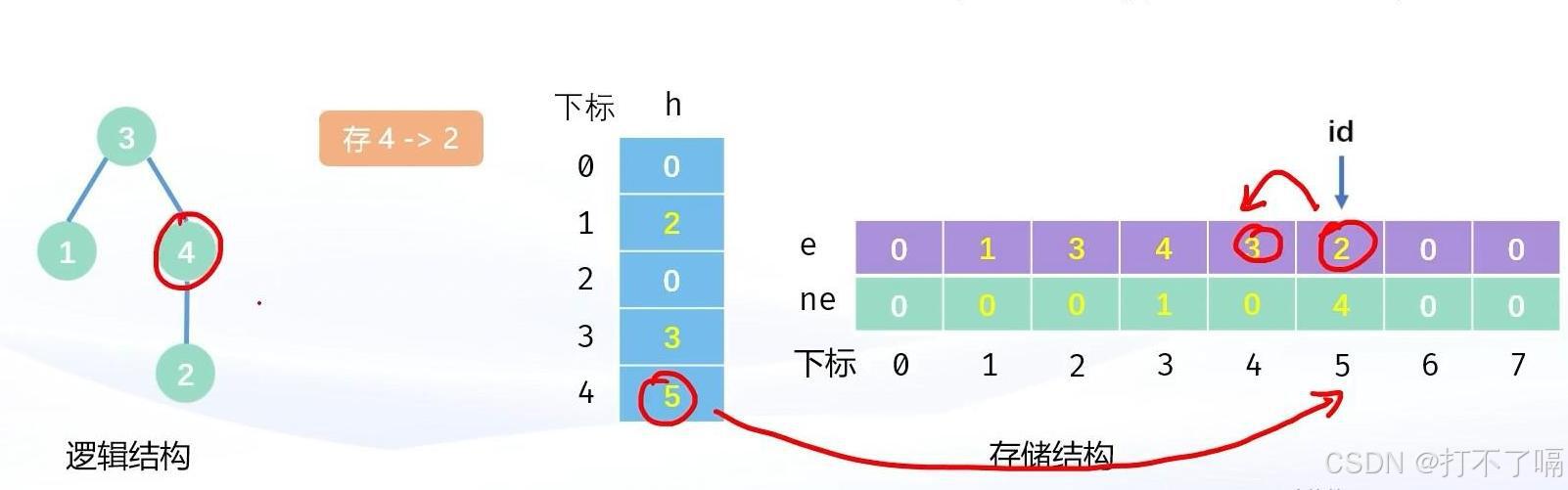

如下框图为例子:

使用如下rtl 代码处理即可;

将所有 子FIFO IP的 full 信号 或 起来;

将所有 子 FIFO IP的 empty 信号 与起来 ;

assign empty = &empty_o ;

assign full = |full_o ;

genvar i;

generate

for(i=FIFO_WIDTH; i<=DATA_WIDTH; i=i+FIFO_WIDTH) begin :

FIFO FIFO_inst(

.rst (rst ),

.wr_clk (wr_clk ),

.rd_clk (rd_clk ),

.din (din[i-1:i-FIFO_WIDTH] ),

.wr_en (wr_en ),

.rd_en (rd_en ),

.dout (dout[i-1:i-FIFO_WIDTH] ),

.full (full_o[i/FIFO_WIDTH-1] ),

.empty (empty_o[i/FIFO_WIDTH-1] )

);

end

endgenerate