mig全称是Memory Interface Generator。

参考自视频:MIG IP配置_哔哩哔哩_bilibili

DDR基础知识

时钟类型

使用流程

选择DDR3

16是地址线的位宽

能在DDR3的型号MT41K256M16XX-125中看出来。

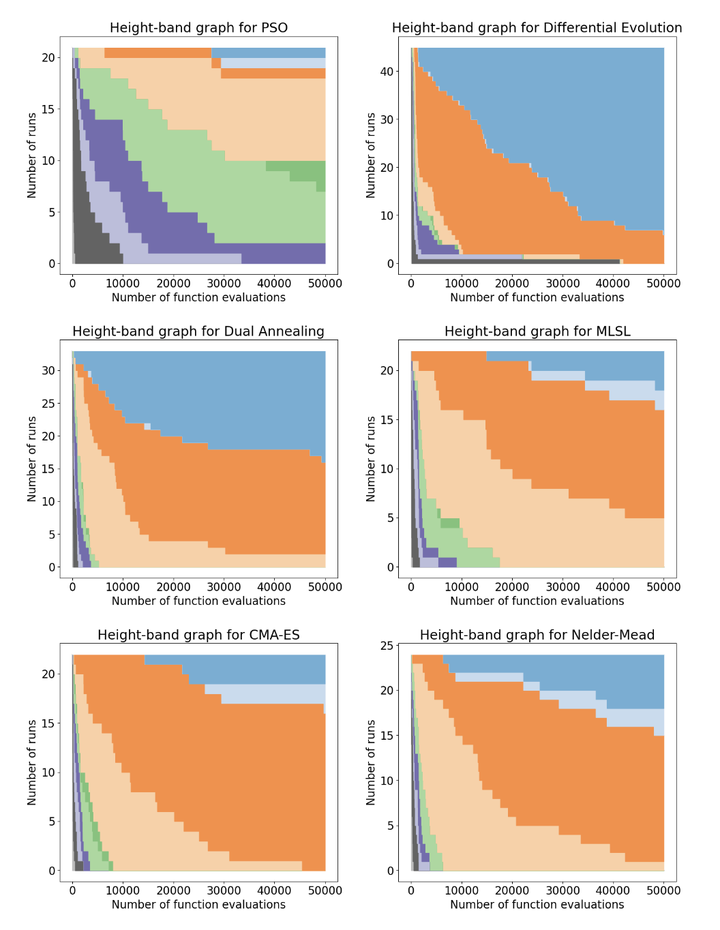

怎么选择clock period 靠的是 芯片型号中的 -125,然后算出 800MHZ,但是我只能选出400MHZ,不太明白为什么,是fpga芯片的问题

- 这是内存控制器的时钟周期,通常指的是控制器访问DDR3存储器时所使用的主时钟周期。例如,图中你设置的 "Clock Period" 为 2.5 ns,对应的是 400 MHz 的时钟频率。

- 这个时钟周期与内存模块通信的速度直接相关,较短的周期意味着更快的时钟频率和更高的数据传输速率。

- 详细解释如手册

参考时钟默认200MHZ,是一个比较固定死的值,如上图的input clock period,就是200MHZ,这个时候就能给参考时钟用的 system clock

XADC的作用主要是

保持默认

点一下restore ,然后next就可以

解决方案是将DQ[8-15]接到另一个byte group上。如下,因为

保持默认

保持默认

用户 MIG DDR的带宽计算

DDR的数据位宽在这里可选

因为存在 用户侧带宽 = DDR带宽 这个等式,所以例化IP核的时候,veo文件会自己计算用户界面的数据位宽。如下所示为128bit

MIG的IP核输入输出和时序

打开示例工程

输入输出

wdf 的全称应该是Write Data FIFO

信号分类:

mig_7series_0 u_mig_7series_0 (

// Memory interface ports

.ddr3_addr (ddr3_addr), // output [14:0] ddr3_addr

.ddr3_ba (ddr3_ba), // output [2:0] ddr3_ba

.ddr3_cas_n (ddr3_cas_n), // output ddr3_cas_n

.ddr3_ck_n (ddr3_ck_n), // output [0:0] ddr3_ck_n

.ddr3_ck_p (ddr3_ck_p), // output [0:0] ddr3_ck_p

.ddr3_cke (ddr3_cke), // output [0:0] ddr3_cke

.ddr3_ras_n (ddr3_ras_n), // output ddr3_ras_n

.ddr3_reset_n (ddr3_reset_n), // output ddr3_reset_n

.ddr3_we_n (ddr3_we_n), // output ddr3_we_n

.ddr3_dq (ddr3_dq), // inout [15:0] ddr3_dq

.ddr3_dqs_n (ddr3_dqs_n), // inout [1:0] ddr3_dqs_n

.ddr3_dqs_p (ddr3_dqs_p), // inout [1:0] ddr3_dqs_p

.init_calib_complete (init_calib_complete), // output init_calib_complete

.ddr3_cs_n (ddr3_cs_n), // output [0:0] ddr3_cs_n

.ddr3_dm (ddr3_dm), // output [1:0] ddr3_dm

.ddr3_odt (ddr3_odt), // output [0:0] ddr3_odt

// Application interface ports

.app_addr (app_addr), // input [28:0] app_addr

.app_cmd (app_cmd), // input [2:0] app_cmd

.app_en (app_en), // input app_en

.app_rdy (app_rdy), // output app_rdy

.app_wdf_data (app_wdf_data), // input [127:0] app_wdf_data

.app_wdf_end (app_wdf_end), // input app_wdf_end

.app_wdf_wren (app_wdf_wren), // input app_wdf_wren

.app_wdf_rdy (app_wdf_rdy), // output app_wdf_rdy

.app_wdf_mask (app_wdf_mask), // input [15:0] app_wdf_mask

.app_rd_data (app_rd_data), // output [127:0] app_rd_data

.app_rd_data_end (app_rd_data_end), // output app_rd_data_end

.app_rd_data_valid (app_rd_data_valid), // output app_rd_data_valid

// app_sr_active ,app_ref_req,app_zq_req 不用可以置零

.app_sr_active (app_sr_active), // output app_sr_active

.app_sr_req (app_sr_req), // input app_sr_req

.app_ref_req (app_ref_req), // input app_ref_req

.app_ref_ack (app_ref_ack), // output app_ref_ack

.app_zq_req (app_zq_req), // input app_zq_req

.app_zq_ack (app_zq_ack), // output app_zq_ack

// 是控制器给到用户界面的时钟和复位

.ui_clk (ui_clk), // output ui_clk

.ui_clk_sync_rst (ui_clk_sync_rst), // output ui_clk_sync_rst

// System Clock Ports

.sys_clk_i (sys_clk_i),

.sys_rst (sys_rst) // input sys_rst

);