(

1

)

ARM+DSP

架构兼备系统控制以及数据处理功能,其中

ARM 承担任

务分配而

DSP

分担数据计算处理,但该系统扩展能力差,后续如想添加新功能

只能更换芯片较为麻烦。

(

2

)

DSP+FPGA

架构中

FPGA

承担数据采集和通信控制的功能,

DSP

负责

算法运算。但任务管理能力差,对于功能繁多的任务来说显然是有所欠缺。

(

3

)

ARM+FPGA

架构具备系统控制以及数据处理功能,相较于

DSP

串行

处理数据的方式,

FPGA

的并行处理在进行数据加速、实时性高的情景下更有优

势。

除上述架构外还有

ARM+DSP+FPGA

架构,该架构优势在于融合多种类型

处理器,提供更完善的功能和更强大的性能,但系统复杂度大幅增加,开发难度

和维护性更高,需要大量人力和物力投入,增加了系统的开发和维护成本。此外,

该架构的优化和调试更具挑战性,需要深入研究不同处理器之间的通信和数据交

换等问题。因此,在选择处理器架构时,需要考虑任务的性质、规模、预算和人

力资源等多方面因素,并在系统性能、复杂度和成本之间进行平衡。所以该架构

不在本次设计考虑范围。

综合考虑各种架构的优缺点以及结合实际开发时的内外在因素,选择基于

FPGA+ARM

架构实现电能质量分析系统设计。

ARM

架构满足三相电力系统电

能质量检测时的任务控制分配,包括三相电压(流)的六通道信号的采集、传输

和处理,并可在后期进行相应的扩展。

FPGA

架构通过对多通道数据并行处理技

术的应用,能够有效降低数据处理时间,实现对实时性要求的满足。

3.2.2

芯片选型

作为整个系统的核心控制组成部分,

ARM

主控核心扮演着极其重要的角色。

在当今市场上众多微处理器种类层出不穷的情况下,选型一款合适的主控核心时

应考虑性能、资源以及配套设施是否完善。包括开发工具、学习资源和实施案例

等方面,在保证系统设计的可靠性和稳定性方面具有重要意义。通过对市场主流

控制芯片的对比分析选型为

STM32F407ZGT6

芯片作为

ARM

端的主控核心。

在

FPGA

芯片选型选择

Xilinx

公司

Spartan-6

系列的

XC6SLX16

芯片作为设

计的目标芯片,并使用

ISE14.7

作为系统工具进行程序设计,采用

Mentor

公司

的

ModelSim

进行仿真功能验证。

3.2.3

硬件架构系统设计

硬件架构设计图如图

3-1

所示。

本系统由前端信号采集预处理模块、基于

FPGA

的数据处理模块和基于

ARM

的人机交互与显示模块构成。

采集预处理模块将电力信号通过调理后转换成适合

ADC

的采样信号,并滤

除所需频率外的高频信号以及保留被测信号的各种信息,承担系统的核心检测工

作,对电能质量参数检测结果的精准性起到了决定性的作用。

基于

FPGA

的数据处理模块包括全数字锁相环模块、主控制模块,

ADC

控

制以及算法等主要模块。其中,主控制器模块负责各模块参数的配置、数据交换

处理等任务,通过与其他模块的协调工作,保证电能质量分析系统的高效有序运

行。

基于

ARM

的人机交互模块是电能质量分析系统的控制部分,集成了

FSMC

控制器模块、配置控制器模块以及通信和存储模块,在系统中起到

“

大脑

”

的作用。

其中

FSMC

是

ARM

和

FPGA

通信总线;

ARM

通过配置控制器模块对

FPGA

进

行相应的初始化配置。

3.3

数据采集预处理电路

电力系统中的电力信号通常是高电压、大电流且存在瞬态事件,因此并不能

直接对其进行数据采集转换,在数据采集时,必须确保仪器具有耐高压的能力,

并在保证使用者自身安全的前提下保证所采集数据的信息完整性。

电力信号的高精度采集依赖于精准可靠的信号采集预处理模块。该模块包括

采集电路、抗混叠滤波电路、同步采样锁相倍频电路、单端转差分电路以及

AD7609

模数转换电路。其中抗混叠滤波电路能有效消除目标信号外的高频干扰

信号,提高采样信号的稳定性和精度;锁相倍频电路可实现信号的精确实时同步,

使得

AD

的采样频率是信号频率的整周期倍,保证采样数据的一致性和准确性;

单端转差分电路可增强信号的抗干扰能力;

AD

模数转换电路将采集到的电力信

号转换为离散数字信号。

本设计是对三相电压和三相电流的六通道信号进行检测,因电压电流预处理

步骤相似,本章仅对电压信号采集模块进行介绍。电压信号采集处理模块结构图

如下图 3-2 所示。

电力信号采样方式有以下两种方式:

(

1

)直流采样:将采集的交流信号不间断的转换成直流信号且与原始信号

保持线性关系,并转换成离散的数字信号。在此过程具有整流和滤波的功能,使

得直流采样具备了很强的抗干扰能力。但实时性不强且对原始信号无法直观观察。

(

2

)交流采样

[47]

:使用互感器对原始交流信号进行采集,并对互感器副边

的交流信号进行采样。优点是采样的信号是与原始信号的频率相同、幅值具有一

定的比例关系的交流信号,具有实时性强且客观的反映出原始信号的波形。

本设计采用的是交流采样的方式对电力信号进行采集,此种方法可以保留原

始信号的波形相位等信息且失真较小。

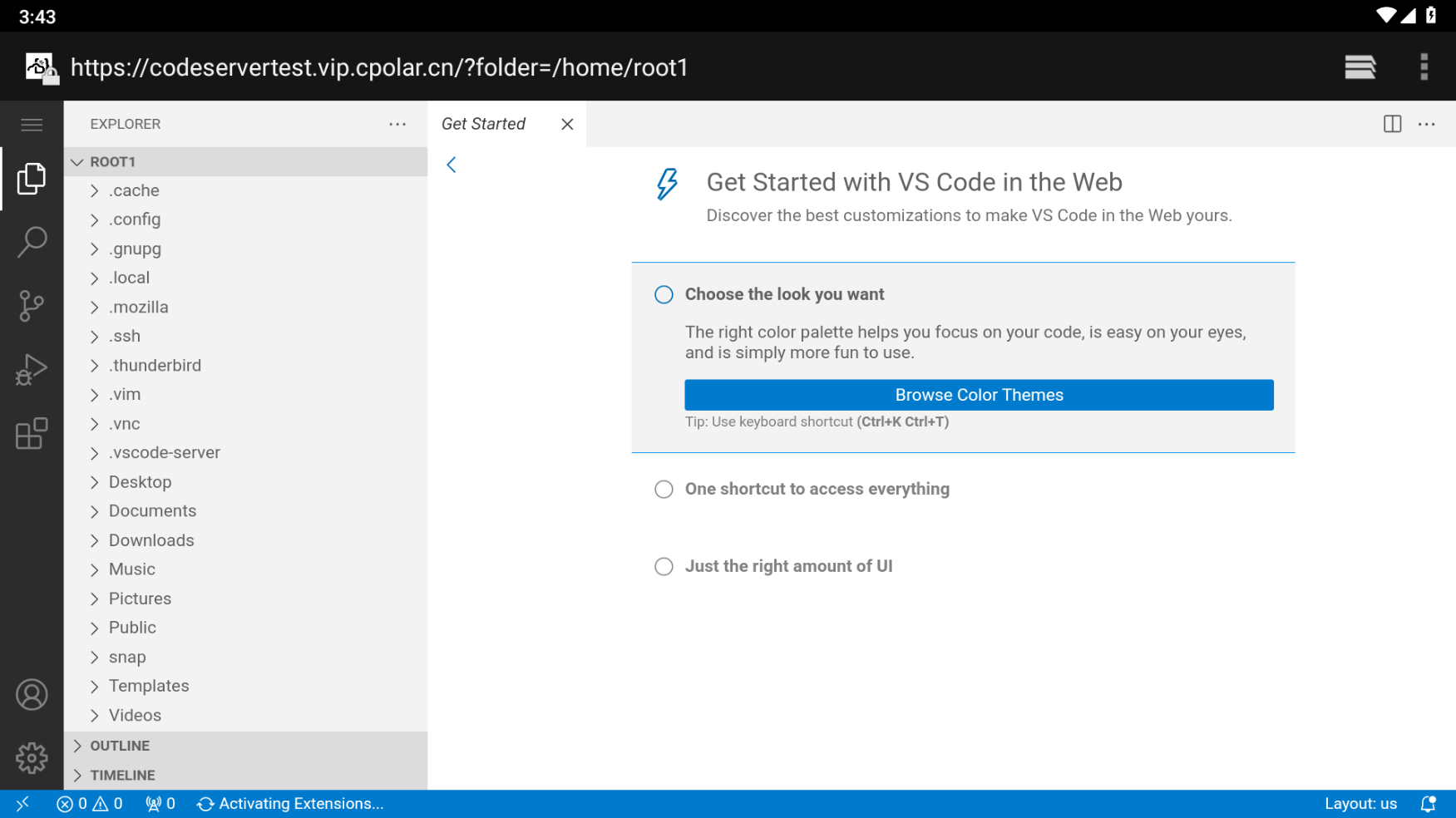

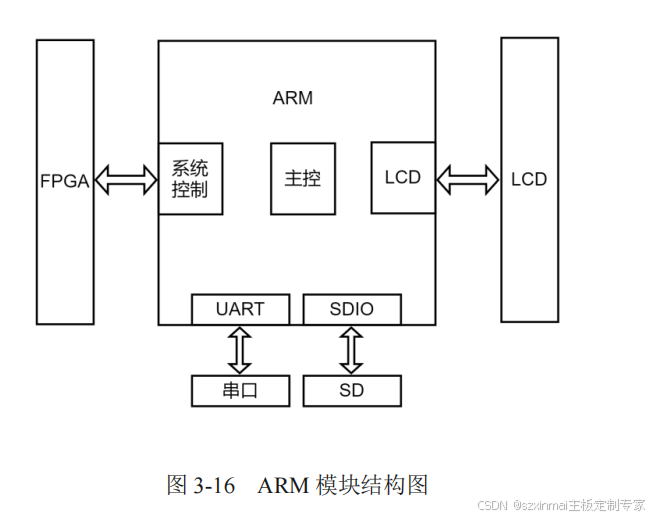

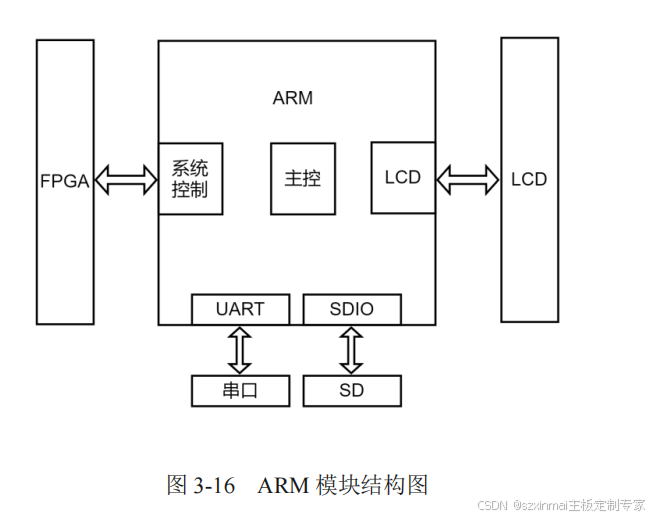

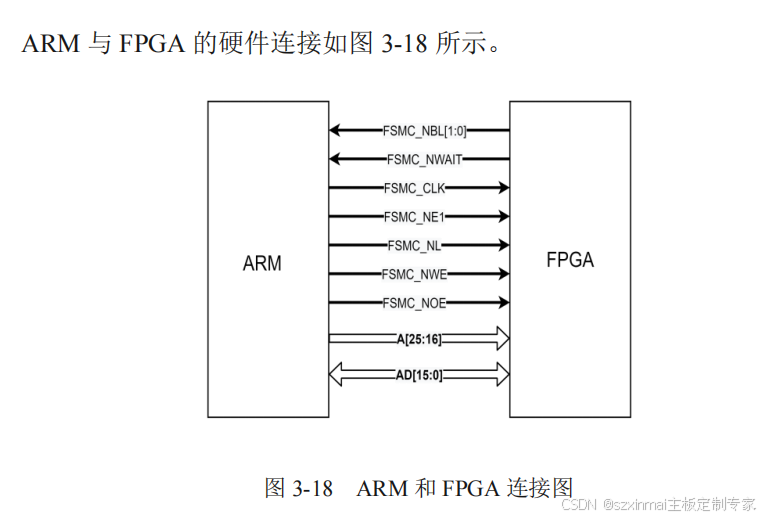

3.6ARM 控制系统设计

ARM 为本系统的控制核心,负责整个系统的协调工作,完成与 FPGA 的数

据传输以及数据存储等。ARM 模块结构框图如图 3-16 所示。

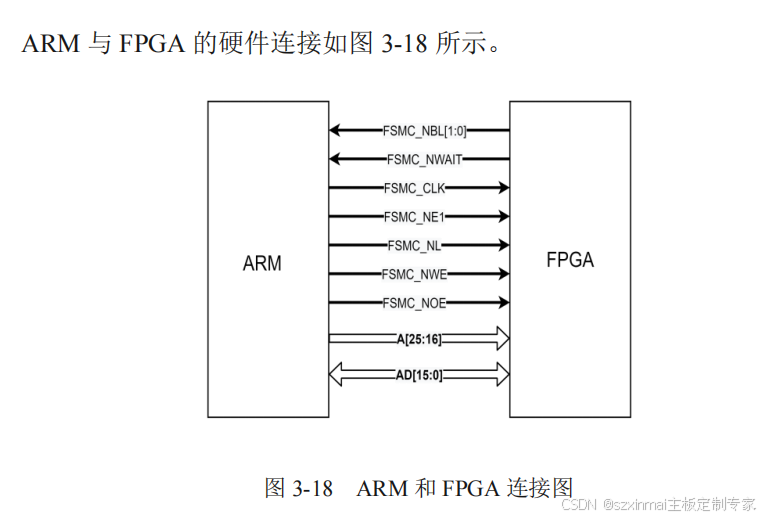

3.5.1 FSMC 接口模块

FSMC 全称为可变静态存储控制器,是 ARM 内嵌的高性能、可靠性的存储

器控制器。该控制器能够连接多种类型的静态存储器,如 SRAM、NOR Flash、

PSRAM 等,并提供高速数据传输和灵活的访问方式,以满足各种嵌入式系统的

需求。FSMC 支持多种数据总线宽度和存储器大小,同时具有多种访问模式和时

序控制功能,以适应不同类型的存储器和应用场景。相对于 EMI 控制器,FSMC

在连接大容量存储器、支持更多的存储器类型、提供更丰富的控制功能和更高的

性能方面更有优势。与 FMC 相比,FSMC 提供更高的数据传输速度和更灵活的

存储器配置方式,同时还具有更高的可靠性和稳定性[54]。因此,本设计采用 FSMC

总线实现 FPGA 与 ARM 的数据通信与传输。

FSMC 将外部静态存储器划分为四个容量相同为 64M 的存储区域,本设计

使用 Bank1 中的 NOR 控制器管理内存。FSMC 存储区域,如图 3-17 所示。

如上图所示,FPGA 与 ARM 通过 FSMC 通信总线连接,通过控制该区域中

FSMC_NE1 的片选信号状态来控制双核的通信以及数据传输;FSMC_NOE 和

FSMC_NEW 是读写控制信号,FSMC_NBL[0:1] 是用于 FPGA 向 STM32 发送

请求中断信号。

3.5.2 数据通信与存储模块

STM32 中 UART 串口仅支持传统的串口通信协议,如 RS-232 或 RS-485 协

议,因此无法直接与上位机进行通信,为实现 STM32 与上位机的通信和控制,需

使用 USB 转串口电路将 UART 串口信号转换为 USB 信号进行传输。USB 转串

口原理图如图 3-19 所示。

![spingboot项目打包到docker镜像[保姆级教程]](https://i-blog.csdnimg.cn/direct/36f4679350784b2ab7667dc2dd3a34c7.png)