目录

- 一、RAM简介

- 1.1 基本特性

- 1.2 RAM对电脑性能的影响

- 1.3 RAM的应用场景

- 二、存储器的分类

- 1.存储器分类

- 2.RAM分类

- 三、实验任务

- 四、程序设计

- 1.系统模块

- 2.波形绘制

- 3.IP核设置

- 4.代码编写

- RTL代码

- Testbench代码

- 五、仿真

提示:以下是本篇文章正文内容,下面案例可供参考

一、RAM简介

RAM,全称为Random Access Memory,即随机存取存储器,是计算机内部数据存储的核心组件,对电脑的流畅运行至关重要。

1.1 基本特性

- 随机存取:RAM允许数据在任何位置被直接读取或写入,无需按照特定顺序,这一特性使其成为处理数据的高速缓存区,能迅速响应CPU的指令。

- 易失性存储:RAM是一种易失性存储器,意味着当电脑关闭或断电时,RAM中的数据会立即消失,无法保留。这是因为RAM依赖电流来维持数据的存储状态。

1.2 RAM对电脑性能的影响

- 容量:RAM的容量越大,电脑能够同时处理的数据量就越多,从而提高了多任务处理的效率。

- 速度:RAM的速度越快,数据在RAM和CPU之间的传输就越迅速,使得电脑在处理复杂任务时更加流畅。

1.3 RAM的应用场景

- 数据存储与缓存:RAM可用于存储配置数据、参数、算法数据和图像数据等,实现快速读写操作,提高系统性能。同时,它也可用于临时存储频繁访问的数据,以提高系统响应速度。

- 图像处理:在图像处理领域,RAM可用于图像帧缓存和存储图像滤波系数等。

- 数据交换与共享:RAM可作为不同模块之间的数据交换区域,实现数据的共享和交互。

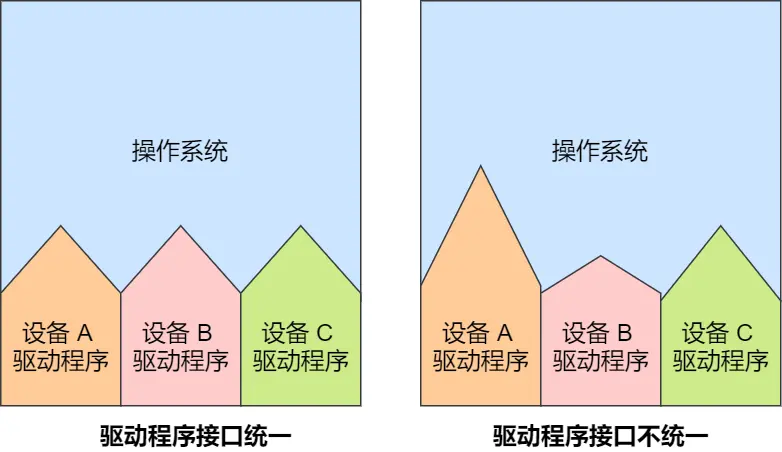

二、存储器的分类

1.存储器分类

2.RAM分类

单端口RAM,简单(伪)双端口RAM,双端口RAM

三、实验任务

使用vivado软件生成一个单端口的RAM并对其进行读写操作,然后通过仿真观察波形是否正确,最后用在线调试工具对实验结果进行验证。如:将RAM设置的深度和宽度分别为32和8进行读写测试

四、程序设计

1.系统模块

2.波形绘制

3.IP核设置

由于实验任务要求深度为32,宽度为8,因此需要对IP核进行简单的设置

4.代码编写

RTL代码

ram_rw模块

module ram_rw (

input clk,

input rst_n,

input [7:0] ram_rd_data,//RAM读出的数据

output reg ram_en,//使能信号

output ram_we,//读写信号

output reg [4:0] ram_addr, //地址

output reg [7:0] ram_wr_data //ram写入的数据

);

reg [5:0] rw_cnt;

assign ram_we = (rw_cnt <= 6'd31 && ram_en == 1'b1)? 1'b1 : 1'b0;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

ram_en <= 1'b0;

else

ram_en <= 1'b1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

rw_cnt <= 6'b0;

else if(ram_en)

rw_cnt <= rw_cnt + 6'b1;

else if(ram_en && rw_cnt == 6'd63)

rw_cnt <= 6'b0;

else

rw_cnt <= 6'b0;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

ram_addr <= 5'b0;

else if(ram_en && ram_addr == 5'd31)

ram_addr <= 5'b0;

else if(ram_en)

ram_addr <= ram_addr + 5'b1;

else

ram_addr <= 5'b0;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

ram_wr_data <= 8'b0;

else if(ram_we && ram_wr_data < 8'd31)

ram_wr_data <= ram_wr_data + 8'b1;

else

ram_wr_data <= 8'b0;

end

endmodule

TOP模块

module ip_1port_ram(

input sys_clk,

input sys_rst_n

);

wire [7:0] ram_rd_data;

wire ram_en;

wire ram_we;

wire [4:0] ram_addr;

wire [7:0] ram_wr_data;

ram_rw u_ram_rw(

.clk (sys_clk),

.rst_n (sys_rst_n) ,

.ram_rd_data (ram_rd_data),

.ram_en (ram_en),

.ram_we (ram_we),

.ram_addr (ram_addr),

.ram_wr_data (ram_wr_data)

);

blk_mem_gen_0 u_blk_mem_gen_0(

.clka (sys_clk),

.ena (ram_en),

.wea (ram_we),

.addra (ram_addr),

.dina (ram_wr_data),

.douta (ram_rd_data)

);

endmodule

Testbench代码

`timescale 1ns/1ns //仿真的单位/仿真的精度s

module tb_ip_1port_ram();

parameter CLK_PERIOD = 20;

reg sys_clk; //周期20ns

reg sys_rst_n; //并非所有的输入都是reg,根据代码编写情况

initial begin

sys_clk <= 1'b0;

sys_rst_n <=1'b0;

#200

sys_rst_n <= 1'b1;

end

always #(CLK_PERIOD/2) sys_clk = ~sys_clk;

ip_1port_ram u_ip_1port_ram (

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n)

);

endmodule

五、仿真

vivado和modelsim联合仿真

仿真结果验证成功!